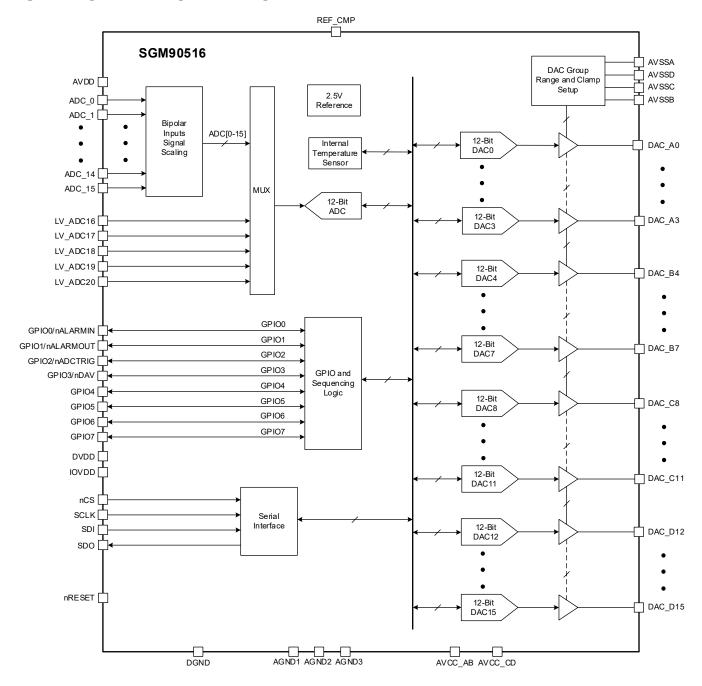

### GENERAL DESCRIPTION

The SGM90516 is a high integrated analog front end, which includes 16 monotonic 12-bit DACs, a 21-input 12-bit SAR ADC, a temperature sensor and an on-chip reference.

The chip also has 8-channel general purpose inputs and outputs (GPIOs). These pins are configurable for ADC inputs or GPIOs.

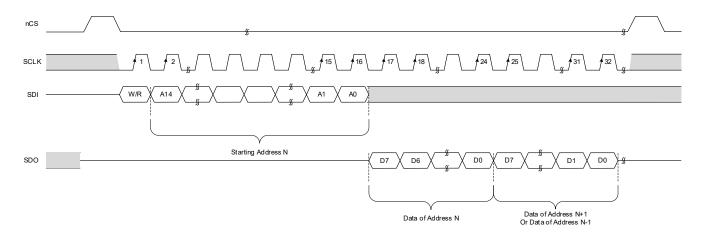

The chip is operated by a 4-wire SPI-compatible interface.

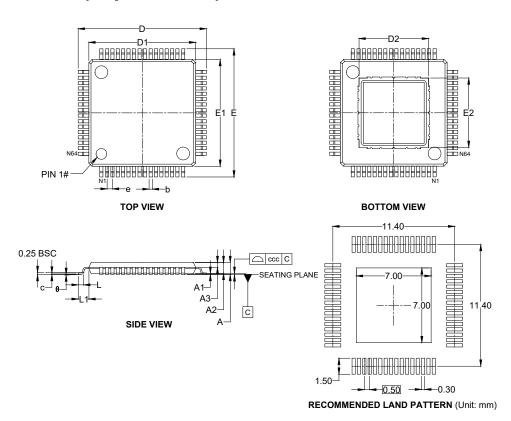

The SGM90516 is available in a Green TQFP-10×10-64L (Exposed Pad) package. It is specified from -40°C to +125°C.

### **APPLICATIONS**

Active Antenna System mMIMO

Distributed Antenna Systems

Macro Remote Radio Unit

Radar

Outdoor Backhaul Unit

Data Acquisition Systems

### **FEATURES**

- 16 Monotonic 12-Bit DACs

- Programmable Voltage Ranges:

-10V to 0V, -5V to 0V, 0V to 5V, and 0V to 10V

SGM90516

- High Current Output: up to ±15mA

- Supports Auto-Range Detector

- Configurable Clamp Voltage

- 12-Bit SAR ADC

- 16 Bipolar Input Channels: -12.5V to +12.5V

- 5 Unipolar Input Channels: 0V to 5V

- Supports Programmable Out-of-Range Alarms

- Internal 2.5V Reference

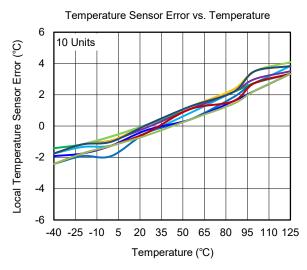

- Internal Temperature Sensor

- -40°C to +125°C Operation

- ±6℃ Accuracy

- 8 General Purpose Input/Output Ports (GPIOs)

- 4-Wire SPI-Compatible Serial Interface

- Supports 1.8V to 5.25V Operation

- -40°C to +125°C Operating Temperature Range

- Available in a Green TQFP-10×10-64L (Exposed Pad) Package

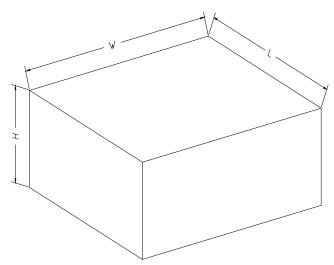

### PACKAGE/ORDERING INFORMATION

| MODEL    | PACKAGE<br>DESCRIPTION          | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING     | PACKING<br>OPTION   |

|----------|---------------------------------|-----------------------------------|--------------------|------------------------|---------------------|

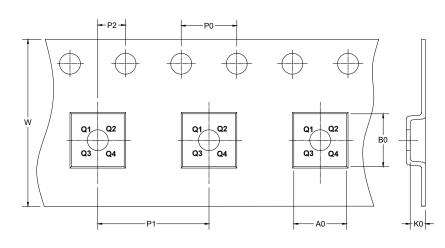

| SGM90516 | TQFP-10×10-64L<br>(Exposed Pad) | -40°C to +125°C                   | SGM90516XTFF64G/TR | 05Q<br>XTFF64<br>XXXXX | Tape and Reel, 1000 |

#### MARKING INFORMATION

NOTE: XXXXX = Date Code. Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

| ABSOLUTE MAXIMUM RATINGS                                                                         |

|--------------------------------------------------------------------------------------------------|

| Voltage Range (with Respect to GND)                                                              |

| V <sub>AVDD</sub> 0.3V to 6V                                                                     |

| V <sub>DVDD</sub> 0.3V to 6V                                                                     |

| V <sub>IOVDD</sub> 0.3V to 6V                                                                    |

| V <sub>AVCC</sub> 0.3V to 18V                                                                    |

| V <sub>AVSSA</sub> 13V to 0.3V                                                                   |

| V <sub>AVSSB</sub> , V <sub>AVSSC</sub> , V <sub>AVSSD</sub> to V <sub>AVSSA</sub> 0.3V to 13V   |

| V <sub>AVCC</sub> to V <sub>AVSSB</sub> , V <sub>AVSSC</sub> , or V <sub>AVSSD</sub> 0.3V to 26V |

| V <sub>AVCC</sub> to V <sub>AVSSA</sub>                                                          |

| DGND to AGND0.3V to 0.3V                                                                         |

| Pin Voltage Range (with Respect to GND)                                                          |

| ADC_[0-15] Analog Inputs13V to 13V                                                               |

| LV_ADC[16-20] Analog Inputs0.3V to V <sub>AVDD</sub> + 0.3V                                      |

| DAC_A[0-3] OutputsV <sub>AVSSA</sub> - 0.3V to V <sub>AVCC</sub> + 0.3V                          |

| DAC_B[4-7] OutputsV <sub>AVSSB</sub> - 0.3V to V <sub>AVCC</sub> + 0.3V                          |

| DAC_C[8-11] OutputsV <sub>AVSSC</sub> - 0.3V to V <sub>AVCC</sub> + 0.3V                         |

| DAC_D[12-15] Outputs $V_{AVSSD}$ - 0.3V to $V_{AVCC}$ + 0.3V                                     |

| REF_CMP0.3V to V <sub>AVDD</sub> + 0.3V                                                          |

| nCS, SCLK, SDI and nRESET0.3V to $V_{\text{IOVDD}}$ + 0.3V                                       |

| SDO0.3V to V <sub>IOVDD</sub> + 0.3V                                                             |

| GPIO[0-7]0.3V to V <sub>IOVDD</sub> + 0.3V                                                       |

| ADC_[0-15] Analog Input Current10mA to 10mA                                                      |

| LV_ADC[16-20] Analog Input Current10mA to 10mA                                                   |

| GPIO[0-7] Sinking Current5mA                                                                     |

| Package Thermal Resistance                                                                       |

| TQFP-10×10-64L (Exposed Pad), $\theta_{JA}$                                                      |

| Junction Temperature+150°C                                                                       |

| Storage Temperature Range65°C to +150°C                                                          |

| Lead Temperature (Soldering, 10s)+260°C                                                          |

| ESD Susceptibility                                                                               |

| HBM2000V                                                                                         |

| CDM500V                                                                                          |

#### RECOMMENDED OPERATING CONDITIONS

| V <sub>AVDD</sub>                                            | 4.7V to 5.5V             |

|--------------------------------------------------------------|--------------------------|

| V <sub>DVDD</sub> <sup>(1)</sup>                             | 4.7V to 5.5V             |

| V <sub>IOVDD</sub> (2)                                       | 1.8V to 5.25V            |

| V <sub>AVCC</sub>                                            | 4.7V to 12.5V            |

| V <sub>AVSSA</sub>                                           | 12.5V to 0V              |

| V <sub>AVSSB</sub> , V <sub>AVSSC</sub> , V <sub>AVSSD</sub> | V <sub>AVSSA</sub> to 0V |

| Specified Operating Temperature Range                        | e40°C to +105°C          |

| Operating Temperature Range                                  | 40°C to +125°C           |

#### NOTES:

- 1. The supply voltage potential of the DVDD pin must be equal to that of the AVDD pin.

- 2. The supply voltage potential of the IOVDD pin must not be higher than that of the DVDD pin.

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### DISCLAIMER

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

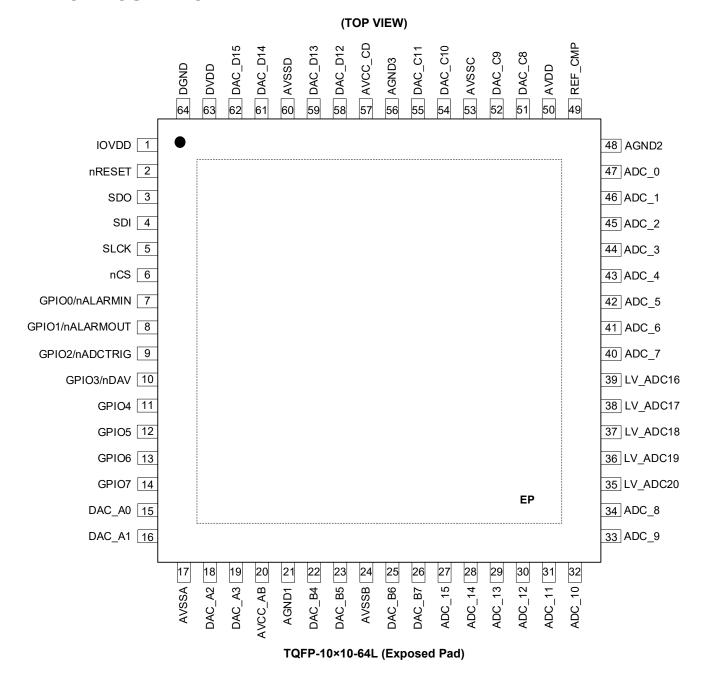

### PIN CONFIGURATION

## **PIN DESCRIPTION**

| PIN | NAME            | I/O | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|-----|-----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1   | IOVDD           | I   | Digital Interface Input/Output Power Supply. It can be operated from 1.8V to 5.25V. The supply voltage potential of the IOVDD pin must not be higher than that of the DVDD pin.                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 2   | nRESET          | I   | Hardware Reset Input Pin. It is active low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 3   | SDO             | 0   | Serial Data Output Pin. When nCS pin is pulled high, SDO is in high-impedance. When nCS pin is low, the data is shifted out by this pin at each falling edge of the SCLK.                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 4   | SDI             | 1   | Serial Data Input Pin. Data is shifted in at each rising edged of the SCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 5   | SCLK            | ı   | Serial Interface Clock Pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 6   | nCS             | I   | Chip Select Pin. This pin also works as the data frame synchronization signal. It is active low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

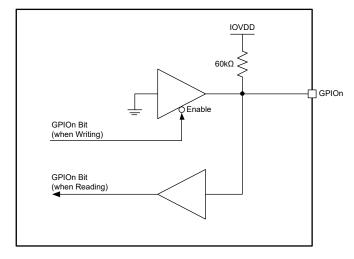

| 7   | GPIO0/nALARMIN  | I/O | General Purpose Digital Input/Output Pin0 (default). It is a bidirectional pin which has an internal $60k\Omega$ resistor pulled up to IOVDD. This pin can be alternatively configured as nALARMIN input pin, which is an active low input signal. This pin can be floated if it is not used.                                                                                                                                                                                                                                                                             |  |  |

| 8   | GPIO1/nALARMOUT | I/O | General Purpose Digital Input/Output Pin1 (default). It is a bidirectional pin which has an internal $60k\Omega$ resistor pulled up to IOVDD. This pin can be alternatively configured as nALARMOUT output pin, which is an open-drain output. If there is an alarm event is generated, it outputs low. This pin can be floated if it is not used.                                                                                                                                                                                                                        |  |  |

| 9   | GPIO2/nADCTRIG  | I/O | General Purpose Digital Input/Output Pin2 (default). It is a bidirectional pin has an internal 60kΩ resistor pulled up to IOVDD. This pin can be alternated configured as nADCTRIG input pin, which is an active low input signal. The edge of nADCTRIG starts ADC sampling and conversion. This pin can be float it is not used.                                                                                                                                                                                                                                         |  |  |

| 10  | GPIO3/nDAV      | I/O | General Purpose Digital Input/Output Pin3 (default). It is a bidirectional pin which has an internal $60k\Omega$ resistor pulled up to IOVDD. This pin can be alternatively configured as nDAV output pin, which is an active low signal that indicates data are available. When the device is in direct mode, the nDAV goes low if the conversion ends. When the device is in auto mode, it will generate a 1µs pulse on nDAV pin if a conversion cycle is completed. When it is in deactivated state, nDAV pin remains high. This pin can be floated if it is not used. |  |  |

| 11  | GPIO4           | I/O |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 12  | GPIO5           | I/O | General Purpose Digital Input/Output Pins. These pins are bidirectional pins which                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 13  | GPIO6           | I/O | each have an internal $60 k\Omega$ resistor pulled up to IOVDD. If they are not used, these pins can be floated.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 14  | GPIO7           | I/O |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 15  | DAC_A0          | 0   | DAC Group A. All DACs in group A have the same output range and clamp voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 16  | DAC_A1          | 0   | When one of the DACs works in a negative range, the others must also be in a negative range.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 17  | AVSSA           | I   | This pin is the negative power supply of DAC group A. It sets the power-on-reset and clamp voltage potential of the DAC group A.                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 18  | DAC_A2          | 0   | DAC Group A. All DACs in group A have the same output range and clamp voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 19  | DAC_A3          | 0   | When one of the DACs works in a negative range, the others must also be in a negative range.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 20  | AVCC_AB         | I   | This pin is the positive analog power of DAC group A and group B. Care should be taken that AVCC_AB and AVCC_CD must have the same voltage potential (AVCC).                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

## **PIN DESCRIPTION (continued)**

| PIN | NAME      | I/O | FUNCTION                                                                                                                                               |  |  |  |

|-----|-----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 21  | AGND1     | ı   | Analog Ground. This pin is the ground of the analog circuits of the chip. AGND1, AGND2 and AGND3 must be connected to same reference point (AGND).     |  |  |  |

| 22  | DAC_B4    | 0   | DAC Group B. All DACs in group B have the same output range and clamp voltage. When one of the DACs works in a negative range, the others must also be |  |  |  |

| 23  | DAC_B5    | 0   | in a negative range.                                                                                                                                   |  |  |  |

| 24  | AVSSB     | I   | This pin is the negative power supply of DAC group B. It sets the power-on-reset and clamp voltage potential of the DAC group B.                       |  |  |  |

| 25  | DAC_B6    | 0   | DAC Group B. All DACs in group B have the same output range and clamp voltage. When one of the DACs works in a negative range, the others must also be |  |  |  |

| 26  | DAC_B7    | 0   | in a negative range.                                                                                                                                   |  |  |  |

| 27  | ADC_15    | I   |                                                                                                                                                        |  |  |  |

| 28  | ADC_14    | I   | Pipeler Appled Inputs, The input veltage range is between 12.5V and 12.5V                                                                              |  |  |  |

| 29  | 29 ADC_13 |     | Bipolar Analog Inputs. The input voltage range is between -12.5V and 12.5V.                                                                            |  |  |  |

| 30  | ADC_12    | I   |                                                                                                                                                        |  |  |  |

| 31  | ADC_11    | I   |                                                                                                                                                        |  |  |  |

| 32  | 32 ADC_10 |     | Dinelar Analog Inputs The input voltage range is between 12 5V and 12 5V                                                                               |  |  |  |

| 33  | ADC_9     | I   | Bipolar Analog Inputs. The input voltage range is between -12.5V and 12.5V.                                                                            |  |  |  |

| 34  | ADC_8     | I   |                                                                                                                                                        |  |  |  |

| 35  | LV_ADC20  | I   |                                                                                                                                                        |  |  |  |

| 36  | LV_ADC19  | I   |                                                                                                                                                        |  |  |  |

| 37  | LV_ADC18  | I   | General Purpose Analog Inputs. The input voltage is between 0 and 2 $\times$ V <sub>REF</sub> .                                                        |  |  |  |

| 38  | LV_ADC17  | I   |                                                                                                                                                        |  |  |  |

| 39  | LV_ADC16  | I   |                                                                                                                                                        |  |  |  |

| 40  | ADC_7     | I   |                                                                                                                                                        |  |  |  |

| 41  | ADC_6     | I   | Disclar Anales books. The insult valteurs are used in between 40.507 and 40.507                                                                        |  |  |  |

| 42  | ADC_5     | I   | Bipolar Analog Inputs. The input voltage range is between -12.5V and 12.5V.                                                                            |  |  |  |

| 43  | ADC_4     | I   |                                                                                                                                                        |  |  |  |

| 44  | ADC_3     | I   |                                                                                                                                                        |  |  |  |

| 45  |           |     | Dinalar Analar Innuts. The innut valtage resum is between 40.517                                                                                       |  |  |  |

| 46  | ADC_1     | I   | Bipolar Analog Inputs. The input voltage range is between -12.5V and 12.5V.                                                                            |  |  |  |

| 47  | ADC_0     | I   |                                                                                                                                                        |  |  |  |

## **PIN DESCRIPTION (continued)**

| PIN         | NAME    | I/O | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 48          | AGND2   | ı   | Analog Ground. This pin is the ground of the analog circuits of the chip. AGND1, AGND2 and AGND3 must be connected to same reference point (AGND).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

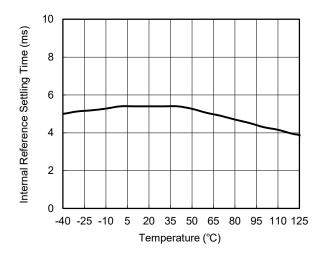

| 49          | REF_CMP | 0   | Internal Reference Decoupling Pin. Connect it with a 4.7µF capacitor to AGND2 pin. Be noted that it will take about 5ms for the REF_CMP voltage fully settling after the ADC_REF_BUFF bit (which is D[4] in ADC configuration register) is enabled from a previous disabled status and at same time at least one ADC channel is selected in ADC MUX configuration registers (which is set by registers 0x13 to 0x15). Before the REF_CMP voltage fully settles, any ADC conversion result is untrusted, and any ADC conversion operation is not recommended. The REF_CMP voltage settling time depends on the decoupling capacitor. The REF_CMP voltage settling time is a setting time when the internal reference source charges to the external decoupling capacitor. The REF_CMP voltage does not need a settling time when the ADC_REF_BUFF bit is enabled from a previous enabled status and any ADC channels that are selected by ADC MUX configuration registers are re-configured. For all the upping explanations, assume that the internal reference is already enabled by setting PREF bit (which is configured in register 0xB4). |

| 50          | AVDD    | I   | Analog Supply Voltage (4.7V to 5.5V). The voltages of AVDD and DVDD pins must be same.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 51          | DAC_C8  | 0   | DAC Group C. All DACs in group C have the same output range and clamp voltage. When one of the DACs works in a negative range, the others must also be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 52          | DAC_C9  | 0   | in a negative range.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 53          | AVSSC   | 1   | This pin is the negative power supply of DAC group C. It sets the power-on-reset and clamp voltage potential of the DAC group C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 54          | DAC_C10 | 0   | DAC Group C. All DACs in group C have the same output range and clamp voltage. When one of the DACs works in a negative range, the others must also be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 55          | DAC_C11 | 0   | in a negative range.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 56          | AGND3   | 1   | Analog Ground. This pin is the ground of the analog circuits of the chip. AGND1, AGND2 and AGND3 must be connected to same reference point (AGND).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 57          | AVCC_CD | I   | This pin is the positive analog power of DAC group C and group D. Care should be taken that AVCC_AB and AVCC_CD must have the same voltage potential (AVCC).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 58          | DAC_D12 | 0   | DAC Group D. All DACs in group D have the same output range and clamp voltage. When one of the DACs works in a negative range, the others must also be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 59          | DAC_D13 | 0   | in a negative range.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 60          | AVSSD   | I   | This pin is the negative power supply of DAC group D. It sets the power-on-reset and clamp voltage potential of the DAC group D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 61          | DAC_D14 | 0   | DAC Group D. All DACs in group D have the same output range and clamp voltage. When one of the DACs works in a negative range, the others must also be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 62          | DAC_D15 | 0   | in a negative range.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 63          | DVDD    | I   | Digital Supply Voltage (4.7V to 5.5V). The voltages of AVDD and DVDD pins must be same.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 64          | DGND    | 1   | Digital Ground. This pin is the ground of the digital circuits of the chip.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Exposed Pad | EP      | I   | Exposed Pad. It should be connected to the same potential as the AVSSA pin or left open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

NOTE: I = input, O = output, I/O = input and output.

## ELECTRICAL CHARACTERISTICS

$(V_{AVDD} = V_{DVDD} = 4.7V \text{ to } 5.5V, V_{AVCC} = 12V, V_{IOVDD} = 1.8V \text{ to } 5.25V, \text{AGND} = \text{DGND} = 0V, V_{AVSSA} = V_{AVSSB} = V_{AVSSC} = V_{AVSSD} = -12V \text{ (for DAC groups in negative range) or 0V (for DAC groups in positive ranges), DAC output range = 0V to 10V for all groups, no load on the DACs, <math>T_A = -40^{\circ}\text{C}$  to  $+105^{\circ}\text{C}$ , typical values are at  $T_A = +25^{\circ}\text{C}$ , the following electrical ratings apply to all specifications in this datasheet, unless otherwise noted.)

| PARAMETER                                   | CONDITIONS                                        |                                          |       | TYP       | MAX  | UNITS  |

|---------------------------------------------|---------------------------------------------------|------------------------------------------|-------|-----------|------|--------|

| DAC DC Accuracy                             |                                                   |                                          |       |           |      |        |

| Resolution                                  |                                                   |                                          | 12    |           |      | Bits   |

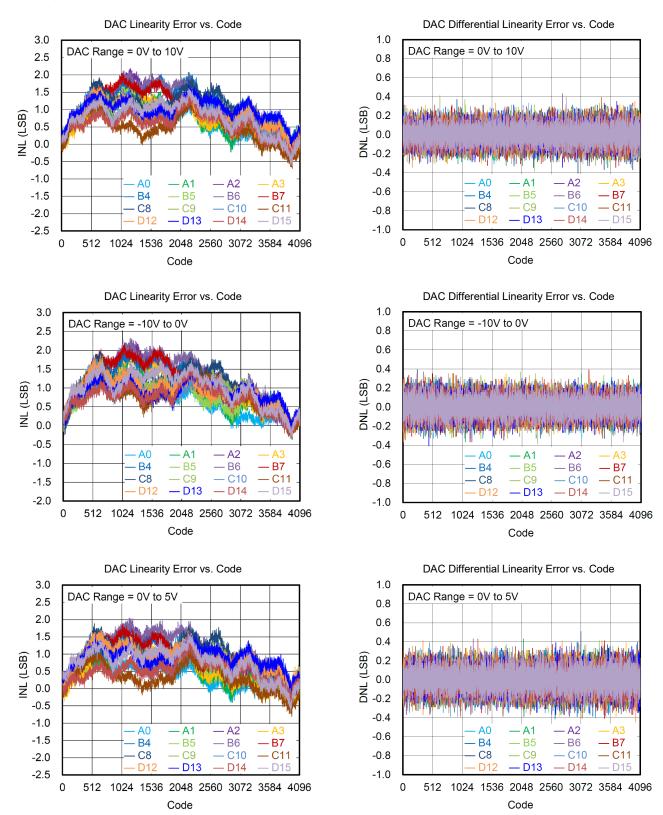

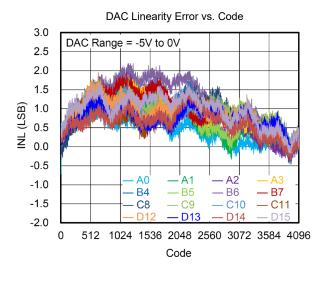

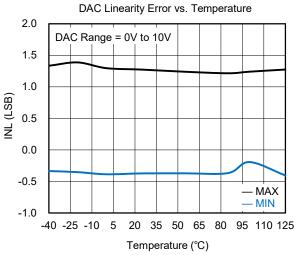

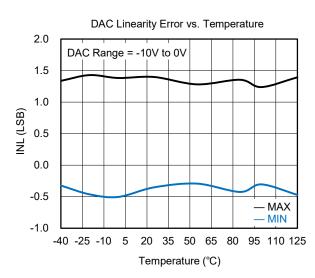

| D 1 ( A ( ) ( ) ( )                         | FE0h)                                             | V ranges (measured codes 020h and        | -3.2  | -0.3/1.2  | 5.5  | 1.00   |

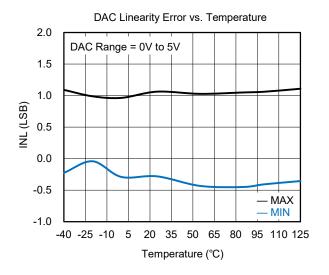

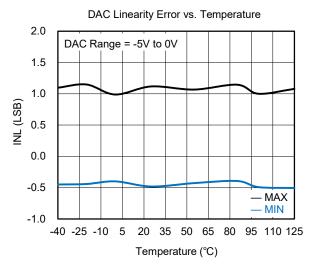

| Relative Accuracy (INL)                     | 0V to 5V and -5V to 0V FE0h)                      | / ranges (measured codes 020h and        | -3.5  | -0.3/1.2  | 5.5  | LSB    |

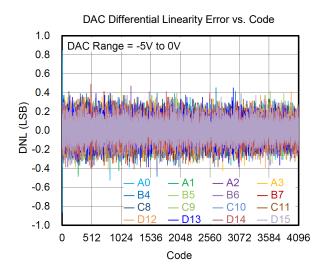

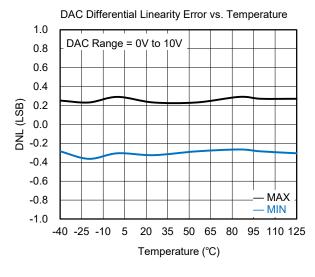

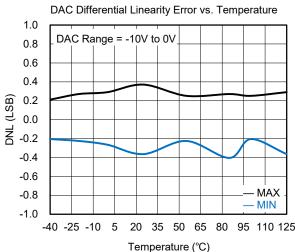

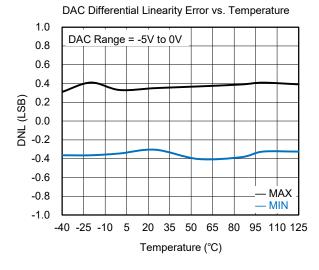

| Differential Nonlinearity (DNL)             | Specified monotonic. 0' (measured codes 020h a    | V to 10V and -10V to 0V ranges and FE0h) | -0.99 | ±0.3      | 0.99 | LSB    |

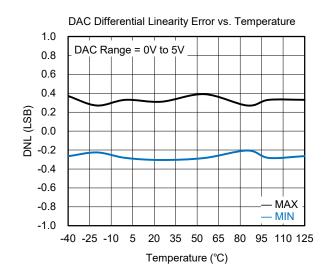

| Differential Notilineanty (DNL)             | Specified monotonic. 0V codes 020h and FE0h)      | to 5V and -5V to 0V ranges (measured     | -0.99 | ±0.3      | 0.99 | LSB    |

|                                             |                                                   | 0V to 10V range                          | -144  | -8.9/2.3  | 90   |        |

| Total Unadjusted Error <sup>(1)</sup> (TUE) | T - 125°C                                         | -10V to 0V range                         | -117  | -1.2/9.5  | 156  |        |

| Total Unadjusted Error (TUE)                | T <sub>A</sub> = +25°C                            | 0V to 5V range                           | -77   | -6.9/5.1  | 74   | mV     |

|                                             |                                                   | -5V to 0V range                          | -62   | -2.4/10.0 | 99   |        |

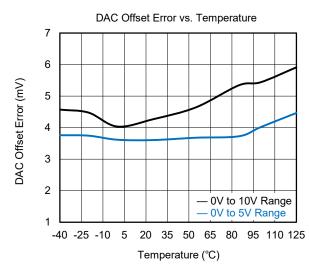

| O#5 - A F                                   | 0V to 10V range (measured codes 020h and FE0h)    |                                          | -72   | 2.4       | 74   | >/     |

| Offset Error                                | 0V to 5V range (measured codes 020h and FE0h)     |                                          |       | 4         | 80   | mV     |

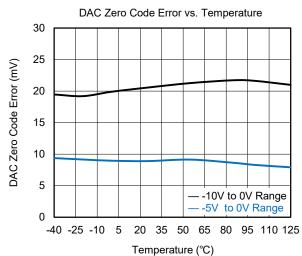

|                                             | T0500                                             | Code 000h, -10V to 0V range              | -137  | 20        | 174  | mV     |

| Zero-Code Error                             | T <sub>A</sub> = +25°C Code 000h, -5V to 0V range |                                          | -85   | 10        | 107  | mv     |

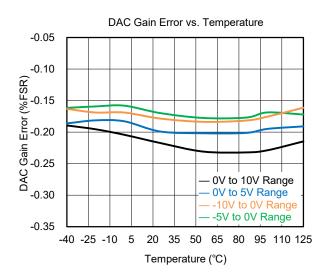

|                                             | 0V to 10V range (measured codes 020h and FE0h)    |                                          | -1.75 | -0.20     | 1.30 |        |

| Online France (1)                           | -10V to 0V range (measured codes 020h and FE0h)   |                                          |       | -0.20     | 1.30 | 0,505  |

| Gain Error (1)                              | 0V to 5V range (measured codes 020h and FE0h)     |                                          |       | -0.20     | 1.35 | %FSR   |

|                                             | -5V to 0V range (measured codes 020h and FE0h)    |                                          |       | -0.20     | 1.35 | 1      |

|                                             | 0V to 10V range                                   |                                          |       | 1         |      | 100    |

| Offset Temperature Coefficient              | 0V to 5V range                                    |                                          |       | 1.5       |      | ppm/°C |

| 7 0 1 7 1 0 5 1                             | -10V to 0V range                                  |                                          |       | 2         |      | 10.0   |

| Zero-Code Temperature Coefficient           | -5V to 0V range                                   |                                          |       | 2         |      | ppm/°C |

|                                             | 0V to 10V range                                   |                                          |       | 1         |      |        |

| O : T                                       | -10V to 0V range                                  |                                          |       | 1.5       |      | ppm/°C |

| Gain Temperature Coefficient (1)            | 0V to 5V range                                    |                                          |       | 3         |      |        |

|                                             | -5V to 0V range                                   |                                          |       | 3         |      | 1      |

#### NOTE:

1. The contribution of internal reference is not included.

## **ELECTRICAL CHARACTERISTICS (continued)**

DAC (continued)

$(V_{AVDD} = V_{DVDD} = 4.7V \text{ to } 5.5V, V_{AVCC} = 12V, V_{IOVDD} = 1.8V \text{ to } 5.25V, AGND = DGND = 0V, V_{AVSSA} = V_{AVSSB} = V_{AVSSC} = V_{AVSSD} = -12V \text{ (for DAC groups in negative range) or 0V (for DAC groups in positive ranges), DAC output range = 0V to 10V for all groups, no load on the DACs, <math>T_A = -40^{\circ}\text{C}$  to  $+105^{\circ}\text{C}$ , typical values are at  $T_A = +25^{\circ}\text{C}$ , the following electrical ratings apply to all specifications in this datasheet, unless otherwise noted.)

| PARAMETER                                      | CONDITIONS                                                                                                                                        | MIN | TYP               | MAX  | UNITS        |  |  |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------|------|--------------|--|--|

| DAC Output Characteristics                     |                                                                                                                                                   |     | •                 | •    | •            |  |  |

| Full-Scale Output Voltage Range <sup>(2)</sup> | DAC_RANGEn[2:0] = 100                                                                                                                             | -10 |                   | 0    |              |  |  |

|                                                | DAC_RANGEn[2:0] = 101                                                                                                                             | -5  |                   | 0    | V            |  |  |

| Full-Scale Output Voltage Range                | DAC_RANGEn[2:0] = 110                                                                                                                             | 0   |                   | 10   | ]            |  |  |

|                                                | DAC_RANGEn[2:0] = 111                                                                                                                             | 0   |                   | 5    | $\exists$    |  |  |

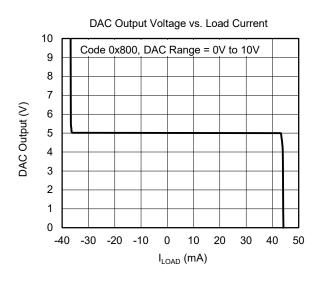

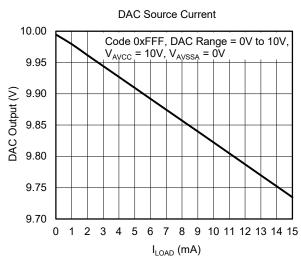

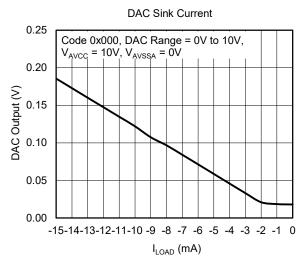

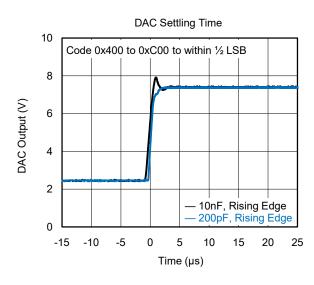

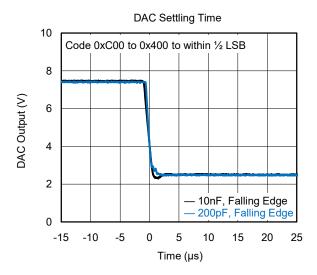

| Output Voltage Settling Time                   | Transition: Code 400h to C00h to within $\frac{1}{2}$ LSB, R <sub>L</sub> = $2k\Omega$ , C <sub>L</sub> = 200pF. 0V to 10V and -10V to 0 V ranges |     | 5                 |      | - IIS        |  |  |

| Calput Voltage Colling Time                    | Transition: Code 400h to C00h to within $\frac{1}{2}$ LSB, R <sub>L</sub> = $2k\Omega$ , C <sub>L</sub> = 200pF. 0V to 5V and -5V to 0V ranges    |     | 5                 |      | μs           |  |  |

| Slew Rate                                      | Transition: Code 400h to C00h, 10% to 90%, $R_L$ = $2k\Omega$ , $C_L$ = 200pF. 0V to 10V and -10V to 0V ranges                                    |     | 4                 |      | V/µs         |  |  |

| Old Mate                                       | Transition: Code 400h to C00h, 10% to 90%, $R_L$ = $2k\Omega$ , $C_L$ = 200pF. 0V to 5V and -5V to 0V ranges                                      |     | 4                 | ν/μ5 |              |  |  |

| Short Circuit Current                          | Full-scale current shorted to the DAC group AVSS or AVCC voltage                                                                                  |     | ±45               |      | mA           |  |  |

| Load Current (3)                               | Source or sink with 1V headroom from the DAC group AVCC or AVSS voltage, voltage drop < 25mV                                                      | ±15 |                   |      | - mA         |  |  |

|                                                | Source or sink with 300mV headroom from the DAC group AVCC or AVSS voltage, voltage drop < 25mV                                                   | ±10 |                   |      | IIIA         |  |  |

| Maximum Capacitive Load (4)                    | $R_L = \infty$ , the capability of load of cap directly                                                                                           | 0   |                   | 10   | nF           |  |  |

| DC Output Impedance                            | Code set to 800h, ±15mA                                                                                                                           |     | 0.2               |      | Ω            |  |  |

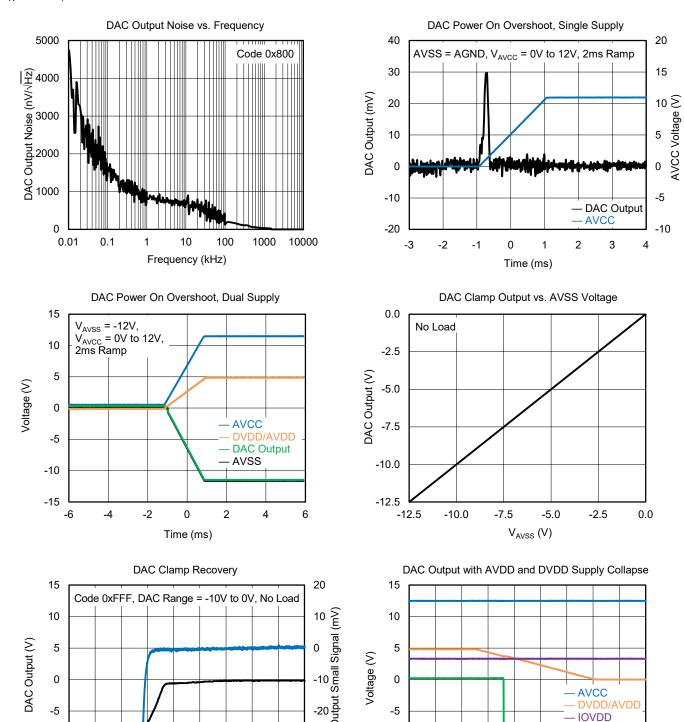

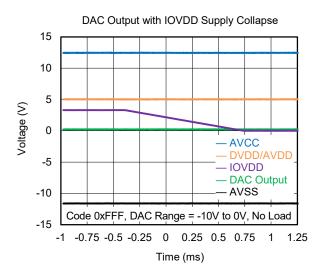

| Power-On Overshoot                             | $V_{AVCC}$ = 12V, $V_{AVSSA}$ = $V_{AVSSB}$ = $V_{AVSSC}$ = $V_{AVSSD}$ = 0V to -12V, 2ms ramp                                                    |     | 30                |      | mV           |  |  |

| Glitch Energy                                  | Transition: Code 7FFh to 800h; 800h to 7FFh                                                                                                       |     | 1                 |      | nV-s         |  |  |

| 0.1.111                                        | 1kHz, code 800h, includes internal reference noise                                                                                                |     | 1000              |      | nV/√Hz       |  |  |

| Output Noise                                   | Integrated noise from 0.1Hz to 10Hz, code 800h, includes internal reference noise                                                                 |     | 100               |      | $\mu V_{PP}$ |  |  |

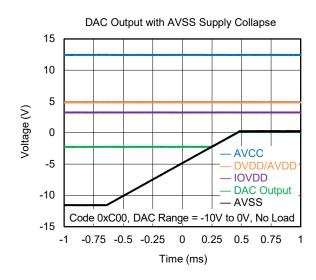

| Clamp Outputs                                  |                                                                                                                                                   |     |                   |      |              |  |  |

|                                                | DAC output range: 0V to 10V, AVSS = AGND                                                                                                          |     | 0                 |      |              |  |  |

| Clamp Output Voltage (5)                       | DAC output range: 0V to 5V, AVSS = AGND                                                                                                           |     | 0                 |      | V            |  |  |

| Ciamp Output voltage                           | DAC output range: -10V to 0V, V <sub>AVSS</sub> = -12V                                                                                            |     | V <sub>AVSS</sub> |      |              |  |  |

|                                                | DAC output range: -5V to 0V, V <sub>AVSS</sub> = -6V                                                                                              |     | V <sub>AVSS</sub> |      |              |  |  |

| Clamp Output Impedance                         |                                                                                                                                                   |     | 80                |      | Ω            |  |  |

#### NOTES:

- 2. The output voltage range of each DAC must be within the positive power supply rail AVCC pin (AVCC\_AB or AVCC\_CD) and the negative power supply rail AVSS pin (AVSSA, AVSSB, AVSSC or AVSSD).

- 3. Make sure that the thermal condition of the chip is within restricted if all channels are loaded simultaneously.

- 4. To be sampled with limited samples, not guaranteed by production testing.

- 5. Tested under the condition that DAC output is floated.

## **ELECTRICAL CHARACTERISTICS (continued)**

### **ADC and Temperature Sensor**

$(V_{AVDD} = V_{DVDD} = 4.7V \text{ to } 5.5V, V_{AVCC} = 12V, V_{IOVDD} = 1.8V \text{ to } 5.25V, AGND = DGND = 0V, V_{AVSSA} = V_{AVSSB} = V_{AVSSC} = V_{AVSSD} = -12V \text{ (for DAC groups in negative range) or 0V (for DAC groups in positive ranges), DAC output range = 0V to 10V for all groups, no load on the DACs, <math>T_A = -40^{\circ}\text{C}$  to  $+105^{\circ}\text{C}$ , typical values are at  $T_A = +25^{\circ}\text{C}$ , the following electrical ratings apply to all specifications in this datasheet, unless otherwise noted.)

| PARAMETER                         | CONE                                 | DITIONS                    | MIN        | TYP  | MAX                     | UNITS  |

|-----------------------------------|--------------------------------------|----------------------------|------------|------|-------------------------|--------|

| Resolution                        |                                      |                            | 12         |      |                         | Bits   |

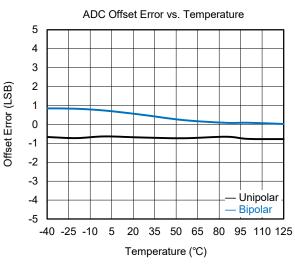

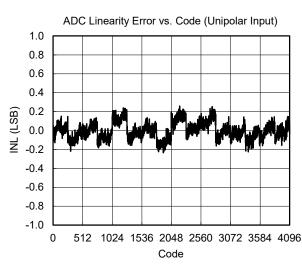

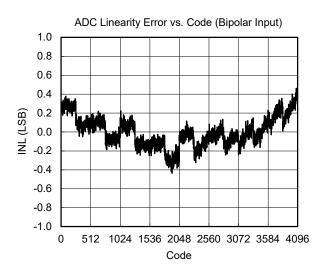

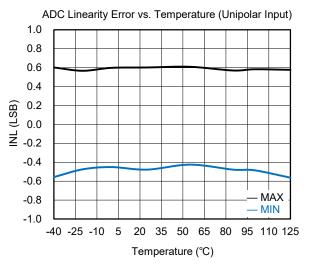

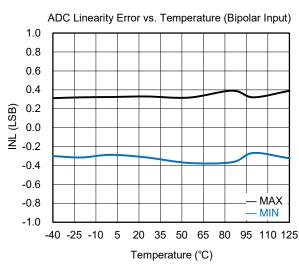

| Internal Naulin conte             | Unipolar input channels              |                            | -1.7       | ±0.5 | 2.2                     | - 0    |

| Integral Nonlinearity             | Bipolar input channels               |                            | -1.5       | ±0.5 | 1.5                     | LSB    |

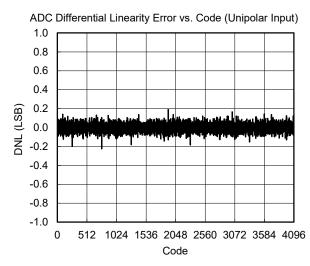

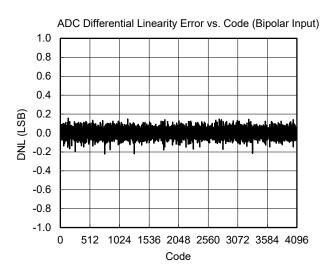

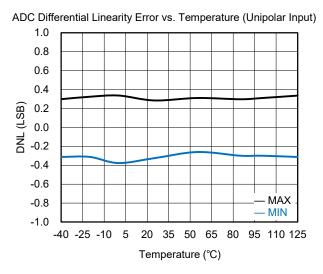

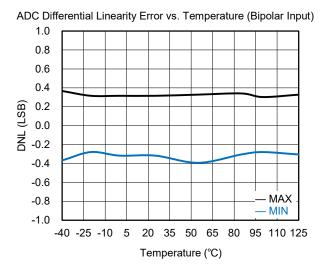

| Differential Nonlinearity         | Specified monotonic. All input       | t channels                 | -0.99      | ±0.5 | 0.99                    | LSB    |

| Unipolar Analog Inputs: LV_ADC1   | 6 to LV_ADC20                        |                            |            |      |                         |        |

| Absolute Input Voltage Range      |                                      |                            | AGND - 0.2 |      | V <sub>AVDD</sub> + 0.2 | V      |

| Full Scale Input Range            | V <sub>REF</sub> measured at REF_CMP | pin                        | 0          |      | 2 × V <sub>REF</sub>    | V      |

| Input Capacitance                 |                                      |                            |            | 15   |                         | pF     |

| DC Input Leakage Current          | Unselected ADC input                 |                            | -10        |      | 10                      | μΑ     |

| Offset Error                      |                                      |                            | -3         | -0.7 | 1.5                     | LSB    |

| Offset Error Match                |                                      |                            |            | ±0.2 |                         | LSB    |

| Gain Error (1)                    |                                      |                            | -3         | 0.6  | 4                       | LSB    |

| Gain Error Match                  |                                      |                            |            | ±0.3 |                         | LSB    |

| Update Time                       | Single unipolar input, tempera       | ature sensor disabled      |            | 12.5 |                         | μs     |

| Bipolar Analog Inputs: ADC_0 to   | ADC_15                               |                            |            |      | •                       |        |

| Absolute Input Voltage Range      |                                      |                            | -13        |      | 13                      | V      |

| Full Scale Input Range            |                                      |                            | -12.5      |      | 12.5                    | V      |

| Input Resistance                  |                                      |                            |            | 120  |                         | kΩ     |

| Offset Error                      |                                      |                            | -7.5       | 0.45 | 9.2                     | LSB    |

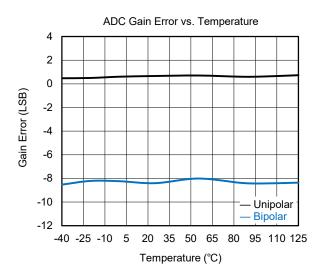

| Gain Error (1)                    |                                      |                            | -28        | -8.3 | 11                      | LSB    |

| Update Time                       | Single bipolar input, temperat       | ure sensor disabled        |            | 26   |                         | μs     |

| Temperature Sensor                |                                      |                            |            |      | •                       |        |

| Operating Range                   |                                      |                            | -40        |      | 125                     | °C     |

| Accuracy                          | V <sub>AVDD</sub> = 5V               |                            |            | ±2   | ±6                      | °C     |

| Resolution                        | LSB size                             |                            |            | 0.25 |                         | °C     |

| Update Time                       | All ADC input channels disable       | ed                         |            | 258  |                         | μs     |

| ADC Update Time                   |                                      |                            |            |      | •                       |        |

| Internal Oscillator Frequency     |                                      |                            | 3.7        | 4    | 4.4                     | MHz    |

| ADO Ha data Tira                  | All 21 ADC inputs enabled, te        | emperature sensor disabled |            | 465  |                         | μs     |

| ADC Update Time                   | All 21 ADC inputs enabled, te        | emperature sensor enabled  |            | 720  |                         | μs     |

| Internal Reference                |                                      |                            |            |      | •                       |        |

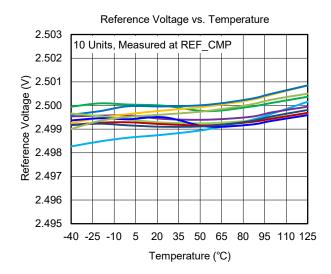

| Initial Assumant                  | T .0590                              | After aging                | 2.49       | 2.5  | 2.51                    |        |

| Initial Accuracy                  | T <sub>A</sub> = +25°C               | Before aging               | 2.497      | 2.5  | 2.503                   | V      |

| Reference Temperature Coefficient |                                      |                            |            | 5    |                         | ppm/°C |

## **ELECTRICAL CHARACTERISTICS (continued)**

#### General

$(V_{AVDD} = V_{DVDD} = 4.7V \text{ to } 5.5V, V_{AVCC} = 12V, V_{IOVDD} = 1.8V \text{ to } 5.25V, AGND = DGND = 0V, V_{AVSSA} = V_{AVSSB} = V_{AVSSC} = V_{AVSSC} = -12V \text{ (for DAC groups in negative range) or 0V (for DAC groups in positive ranges), DAC output range = 0V to 10V for all groups, no load on the DACs, <math>T_A = -40^{\circ}\text{C}$  to  $+105^{\circ}\text{C}$ , typical values are at  $T_A = +25^{\circ}\text{C}$ , the following electrical ratings apply to all specifications in this datasheet, unless otherwise noted.)

| PARAMETER                                      | CONDITIONS                                        | MIN                       | TYP          | MAX                    | UNITS |

|------------------------------------------------|---------------------------------------------------|---------------------------|--------------|------------------------|-------|

| AVSS Detector                                  |                                                   |                           |              | •                      |       |

| AVSS Threshold Detector (V <sub>AVSSTH</sub> ) |                                                   | -3.5                      |              | -1.5                   | V     |

| Digital Logic: GPIO                            |                                                   |                           |              |                        |       |

| High-Level Input Voltage                       | V <sub>IOVDD</sub> = 1.8V to 5.25V                | 0.75 × V <sub>IOVDD</sub> |              |                        | V     |

| Low-Level Input Voltage                        | V <sub>IOVDD</sub> = 1.8V                         |                           |              | 0.45                   | V     |

| Low-Level Input Voltage                        | V <sub>IOVDD</sub> = 2.7V to 5.25V                |                           |              | $0.3 \times V_{IOVDD}$ | V     |

| Low Lovel Output Voltage                       | $V_{IOVDD}$ = 1.8V, $I_{LOAD}$ = -2mA             |                           |              | 0.4                    | V     |

| Low-Level Output Voltage                       | $V_{IOVDD} = 5.25V$ , $I_{LOAD} = -5mA$           |                           |              | 0.4                    | V     |

| Input Impedance                                | To IOVDD                                          |                           | 60           |                        | kΩ    |

| Digital Logic: All Except GPIO                 |                                                   |                           |              |                        |       |

| High-Level Input Voltage                       | V <sub>IOVDD</sub> = 1.8V to 5.25V                | 0.75 × V <sub>IOVDD</sub> |              |                        | V     |

| Low-Level Input Voltage                        | V <sub>IOVDD</sub> = 1.8V                         |                           |              | 0.45                   | V     |

| Low-Level Input Voltage                        | V <sub>IOVDD</sub> = 2.7V to 5.25V                |                           |              | $0.3 \times V_{IOVDD}$ | V     |

| High-Level Output Voltage                      | I <sub>LOAD</sub> = -1mA                          | V <sub>IOVDD</sub> - 0.4  |              |                        | V     |

| Low-Level Output Voltage                       | I <sub>LOAD</sub> = 1mA                           |                           |              | 0.4                    | V     |

| High Impedance Leakage                         |                                                   | -5                        |              | 5                      | μΑ    |

| High Impedance Output Capacitance              |                                                   |                           | 5            |                        | pF    |

| Power Requirements                             |                                                   |                           |              |                        |       |

| AVDD Supply Current (I <sub>AVDD</sub> )       |                                                   |                           | 3.9          | 6                      |       |

| AVCC Supply Current (I <sub>AVCC</sub> )       |                                                   |                           | 2.3          | 5                      | 4     |

| AVSS Supply Current (I <sub>AVSS</sub> )       | No DAC load, all DACs at 800h code and ADC at the | -5                        | <b>-</b> 2.5 |                        | mA    |

| DVDD Supply Current (I <sub>DVDD</sub> )       | fastest auto conversion rate                      |                           | 1.4          | 3                      | ļ     |

| IOVDD Supply Current (I <sub>IODD</sub> )      |                                                   |                           | 10           | 20                     | μΑ    |

| Power Consumption                              |                                                   |                           | 100          |                        | mW    |

| AVDD Supply Current (I <sub>AVDD</sub> )       |                                                   |                           | 0.04         | 0.1                    |       |

| AVCC Supply Current (I <sub>AVCC</sub> )       |                                                   |                           | 0.3          | 1                      | A     |

| AVSS Supply Current (I <sub>AVSS</sub> )       | Power-down mode                                   | -1                        | -0.6         |                        | mA    |

| DVDD Supply Current (I <sub>DVDD</sub> )       | Tower-down fliode                                 |                           | 0.12         | 0.2                    | İ     |

| IOVDD Supply Current (I <sub>IODD</sub> )      |                                                   |                           | 10           | 18                     | μΑ    |

| Power Consumption                              |                                                   |                           | 20           |                        | mW    |

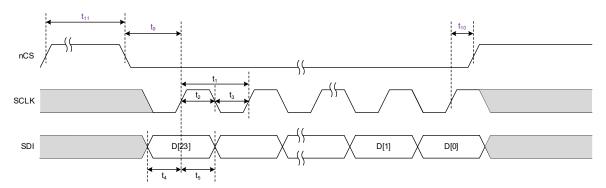

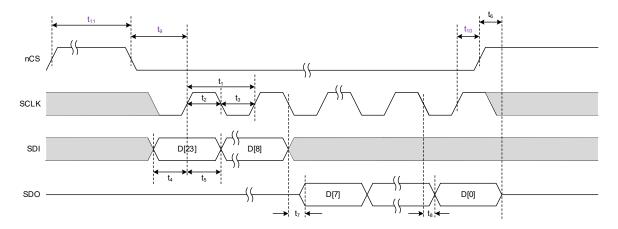

### **TIMING REQUIREMENTS**

$(V_{AVDD} = V_{DVDD} = 4.7V \text{ to } 5.5V, V_{AVCC} = 12V, V_{AVSSA} = -12V, AGND = DGND = V_{AVSSB} = V_{AVSSC} = V_{AVSSD} = 0V, DAC \text{ output range} = 0V \text{ to } 10V \text{ for all groups, no load on the DACs, } T_A = -40^{\circ}C \text{ to } +105^{\circ}C, \text{ typical values are at } T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

| PARAMETER                                                                             | CONDITIONS                         | MIN | TYP | MAX | UNITS |  |

|---------------------------------------------------------------------------------------|------------------------------------|-----|-----|-----|-------|--|

| Serial Interface (1)                                                                  |                                    |     |     |     |       |  |

|                                                                                       | V <sub>IOVDD</sub> = 1.8V to 2.7V  |     |     | 20  |       |  |

| SCLK Frequency (f <sub>SCLK</sub> )                                                   | V <sub>IOVDD</sub> = 2.7V to 5.25V |     |     | 20  | MHz   |  |

| 2                                                                                     | V <sub>IOVDD</sub> = 1.8V to 2.7V  | 50  |     |     | ns    |  |

| SCLK Period <sup>(2)</sup> (t <sub>1</sub> )                                          | V <sub>IOVDD</sub> = 2.7V to 5.25V | 50  |     |     |       |  |

|                                                                                       | V <sub>IOVDD</sub> = 1.8V to 2.7V  | 23  |     |     | ne    |  |

| SCLK Pulse Width High <sup>(2)</sup> (t <sub>2</sub> )                                | V <sub>IOVDD</sub> = 2.7V to 5.25V | 23  |     |     | ns    |  |

| (2)                                                                                   | V <sub>IOVDD</sub> = 1.8V to 2.7V  | 23  |     |     |       |  |

| SCLK Pulse Width Low (2) (t <sub>3</sub> )                                            | V <sub>IOVDD</sub> = 2.7V to 5.25V | 23  |     |     | ns    |  |

| 271.2 (2) (1)                                                                         | V <sub>IOVDD</sub> = 1.8V to 2.7V  | 10  |     |     | 1     |  |

| SDI Setup <sup>(2)</sup> (t <sub>4</sub> )                                            | V <sub>IOVDD</sub> = 2.7V to 5.25V | 10  |     |     | ns    |  |

| 27(2) (4.)                                                                            | V <sub>IOVDD</sub> = 1.8V to 2.7V  | 10  |     |     | ns    |  |

| SDI Hold <sup>(2)</sup> (t₅)                                                          | V <sub>IOVDD</sub> = 2.7V to 5.25V | 10  |     |     |       |  |

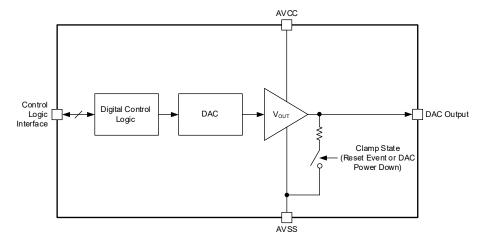

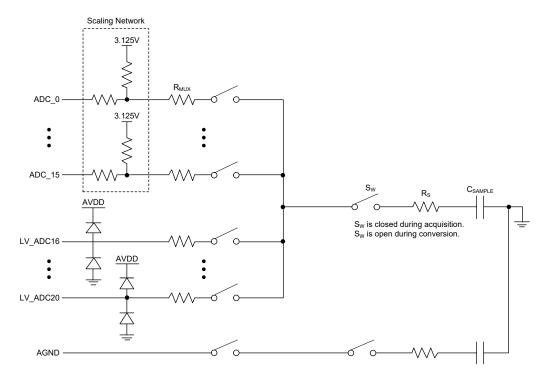

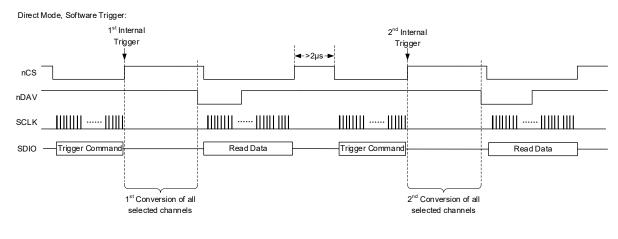

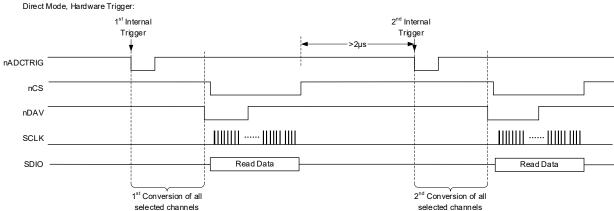

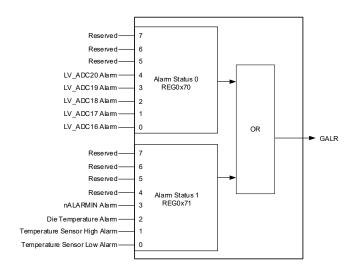

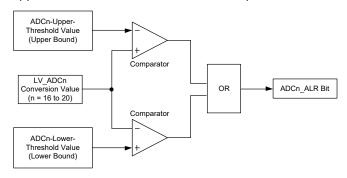

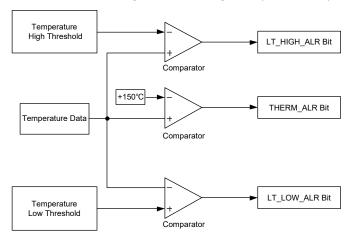

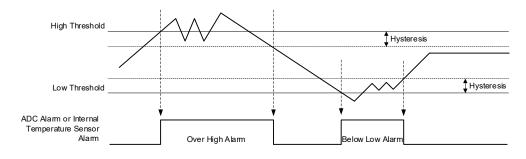

| 00000 (3)(4)(4)                                                                       | V <sub>IOVDD</sub> = 1.8V to 2.7V  | 0   |     | 15  | ns    |  |