# SGM48522Q Automotive Dual 5V, 7A/6A Low-side GaN and MOSFET Driver

### **GENERAL DESCRIPTION**

The high-speed, dual-channel low-side driver SGM48522Q is designed to drive GaN FETs and logic level MOSFETs. The application areas include LiDAR, time of flight, facial recognition, and power converters using low-side drivers. The SGM48522Q provides 7A source and 6A sink output current capability. Split output configuration allows individual turn-on and turn-off time optimization depending on FET. The Flip-Chip TQFN package and pinout minimize parasitic inductances to reduce the rise and fall time and limit the ringing. Additionally, the 2ns propagation delay with minimized tolerances and variations allows efficient operation at high frequencies.

The driver has internal under-voltage lockout and over-temperature protection against overload and fault events.

This device is AEC-Q100 qualified (Automotive Electronics Council (AEC) Standard Q100 Grade 1) and it is suitable for automotive applications.

The SGM48522Q is available in a Green TQFN-2×2-10AL package.

# FEATURES

- AEC-Q100 Qualified for Automotive Applications Device Temperature Grade 1 T<sub>A</sub> = -40°C to +125°C

- 5V Supply Voltage

- 7A Peak Source and 6A Peak Sink Currents

- Ultra-Fast, Low-side Gate Driver for GaN and Si FETs

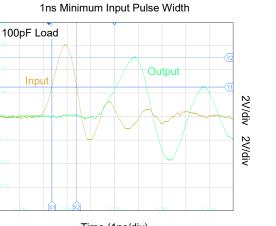

- Minimum Input Pulse Width: 1ns

- Up to 60MHz Operation

- Propagation Delay: 2ns (TYP)

- Rise Time: 720ps (TYP)

- Fall Time: 570ps (TYP)

- Protection Features:

- Under-Voltage Lockout (UVLO)

- Over-Temperature Protection (OTP)

- Available in a Green TQFN-2×2-10AL Package

## **APPLICATIONS**

Automotive Applications Laser Distance Measuring System (LiDAR) 5G RF Communication System Wireless Charging System GaN DC/DC Conversion System

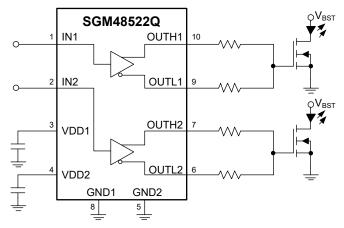

## **TYPICAL APPLICATION**

Figure 1. Typical Application Circuit

### Automotive Dual 5V, 7A/6A Low-Side GaN and MOSFET Driver

### **PACKAGE/ORDERING INFORMATION**

| MODEL     | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING | PACKING<br>OPTION   |

|-----------|------------------------|-----------------------------------|--------------------|--------------------|---------------------|

| SGM48522Q | TQFN-2×2-10AL          | -40°C to +125°C                   | SGM48522QTSV10G/TR | 0HT<br>XXXX        | Tape and Reel, 3000 |

### MARKING INFORMATION

NOTE: XXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, V <sub>DD1</sub> , V <sub>DD2</sub> 0.3 | 3V to 6V |

|---------------------------------------------------------|----------|

| IN1, IN2 Pin Voltage, V <sub>INx</sub> 0.3              | 3V to 6V |

| OUTH1, OUTH2 Pin Voltage, VOUTHX0.3V to VDI             | D + 0.3V |

| OUTL1, OUTL2 Pin Voltage, V <sub>OUTLx</sub>            |          |

| DC0.3                                                   | 3V to 6V |

| Repetitive Pulse < 5ns2                                 | 2V to 7V |

| Package Thermal Resistance                              |          |

| TQFN-2×2-10AL, θ <sub>JA</sub> 8                        | 1.8°C/W  |

| TQFN-2×2-10AL, θ <sub>JB</sub> 18                       | 8.9°C/W  |

| TQFN-2×2-10AL, θ <sub>JC</sub> 5                        | 7.3°C/W  |

| Junction Temperature                                    | .+150°C  |

| Storage Temperature Range65°C to                        | +150°C   |

| Lead Temperature (Soldering, 10s)                       | .+260°C  |

| ESD Susceptibility                                      |          |

| НВМ                                                     | 4000V    |

| CDM                                                     | 1500V    |

|                                                         |          |

### **RECOMMENDED OPERATING CONDITIONS**

| Supply Voltage, V <sub>DD1</sub> , V <sub>DD2</sub> | 4.5V to 5.5V   |

|-----------------------------------------------------|----------------|

| IN1, IN2 Pin Voltage, V <sub>INx</sub>              | 0V to 5.5V     |

| Operating Ambient Temperature Range                 | 40°C to +125°C |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### ESD SENSITIVITY CAUTION

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### DISCLAIMER

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

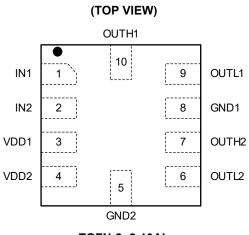

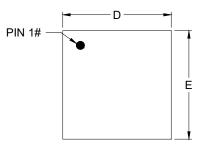

# **PIN CONFIGURATION**

TQFN-2×2-10AL

# **PIN DESCRIPTION**

| PIN | NAME  | I/O | FUNCTION                                                                                                                                                              |

|-----|-------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | IN1   | Ι   | Channel 1 Control Logic Input (Non-Inverting).                                                                                                                        |

| 2   | IN2   | I   | Channel 2 Control Logic Input (Non-Inverting).                                                                                                                        |

| 3   | VDD1  | I   | Channel 1 Input Voltage Supply. Bypass to GND with a low inductance ceramic capacitor.                                                                                |

| 4   | VDD2  | I   | Channel 2 Input Voltage Supply. Bypass to GND with a low inductance ceramic capacitor.                                                                                |

| 5   | GND2  | _   | Channel 2 Ground. Internally connected to GND1 by anti-parallel diodes.                                                                                               |

| 6   | OUTL2 | 0   | Channel 2 Pull-Down Gate Drive Output. Connect it to the gate of the target transistor with an optional resistor.                                                     |

| 7   | OUTH2 | 0   | Channel 2 Pull-Up Gate Drive Output. Connect it to the gate of the target transistor with an optional resistor. Internally connected to GND2 by anti-parallel diodes. |

| 8   | GND1  | _   | Channel 1 Ground.                                                                                                                                                     |

| 9   | OUTL1 | 0   | Channel 1 Pull-Down Gate Drive Output. Connect it to the gate of the target transistor with an optional resistor.                                                     |

| 10  | OUTH1 | 0   | Channel 1 Pull-Up Gate Drive Output. Connect it to the gate of the target transistor with an optional resistor.                                                       |

NOTE: I = input, O = output.

## **FUNCTION TABLE**

| INx Pin | OUTHx Pin | OUTLx Pin |

|---------|-----------|-----------|

| L       | Open      | L         |

| Н       | Н         | Open      |

# Automotive Dual 5V, 7A/6A Low-Side GaN and MOSFET Driver

# **ELECTRICAL CHARACTERISTICS**

(V<sub>DD</sub> = 4.5V to 5.5V,  $T_A$  = -40°C to +125°C, typical values are at  $T_A$  = +25°C, unless otherwise noted.)

| PARAMETER                                        | SYMBOL                              | CONDITIONS                                        | MIN  | TYP  | MAX  | UNITS |

|--------------------------------------------------|-------------------------------------|---------------------------------------------------|------|------|------|-------|

| DC Characteristics                               |                                     | ·                                                 |      |      |      |       |

| VDD Quiescent Current                            | 1                                   | $V_{\rm IN1} = V_{\rm IN2} = V_{\rm DD}$          |      | 50   | 100  |       |

| VDD Quescent Current                             | VDDQ                                | $V_{\rm IN1} = V_{\rm IN2} = 0V$                  |      | 50   | 100  | μA    |

| VDD Operating Current                            |                                     | f <sub>sw</sub> = 30MHz, no load                  |      | 48   |      | mA    |

| VDD Operating Current                            | IVDD_OP                             | f <sub>sw</sub> = 30MHz, 100pF load               |      | 63   |      | mA    |

| Under-Voltage Lockout Threshold                  | V <sub>DD_UVLO</sub>                | V <sub>DDx</sub> rising. Per channel              | 3.95 | 4.18 | 4.40 | V     |

| UVLO Hysteresis                                  | $\Delta V_{\text{DD}\_\text{UVLO}}$ |                                                   |      | 97   |      | mV    |

| Over-Temperature Shutdown, Rising Edge Threshold | T <sub>OTP</sub>                    | Per channel                                       |      | 175  |      | °C    |

| Over-Temperature Hysteresis                      | $\Delta T_{\text{OTP}}$             |                                                   |      | 23   |      | °C    |

| Input DC Characteristics                         |                                     |                                                   |      |      |      |       |

| IN1, IN2 High Threshold                          | V <sub>IH</sub>                     |                                                   | 1.7  | 2.1  | 2.6  | V     |

| IN1, IN2 Low Threshold                           | VIL                                 |                                                   | 1.1  | 1.4  | 1.8  | V     |

| IN1, IN2 Hysteresis                              | V <sub>HYS</sub>                    |                                                   | 0.38 |      | 1    | V     |

| Input Pull-Down Resistance                       | R <sub>INx</sub>                    | INx to GNDx                                       | 100  | 200  | 250  | kΩ    |

| Input Pin Capacitance                            | C <sub>INx</sub>                    | INx to GNDx                                       |      | 2.3  |      | pF    |

| Output DC Characteristics                        |                                     |                                                   |      |      |      |       |

| Output Low Voltage (OUTLx)                       | V <sub>OL</sub>                     | I <sub>OUTLx</sub> = 100mA, V <sub>INx</sub> = 0V |      |      | 36   | mV    |

| Output High Voltage (OUTHx)                      | V <sub>DDx</sub> - V <sub>OHx</sub> | $I_{OUTHx}$ = 100mA, $V_{INx}$ = 5V               |      |      | 50   | mV    |

| Peak Source Current                              | I <sub>он</sub>                     | V <sub>OUTHx</sub> = 0V, V <sub>INx</sub> = 5V    |      | 7    |      | А     |

| Peak Sink Current                                | I <sub>OL</sub>                     | V <sub>OUTLx</sub> = 5V, V <sub>INx</sub> = 0V    |      | 6    |      | А     |

## SWITCHING CHARACTERISTICS

(V<sub>DD</sub> = 4.5V to 5.5V, T<sub>A</sub> = -40°C to +125°C, typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.)

| PARAMETER                                                                                          | SYMBOL             | CONDITIONS                                                               | MIN | TYP | MAX | UNITS |

|----------------------------------------------------------------------------------------------------|--------------------|--------------------------------------------------------------------------|-----|-----|-----|-------|

| Startup Time, V <sub>DDx</sub> Rising above UVLO                                                   | t <sub>START</sub> | $_{\rm IRT}$ INx = VDDx, V <sub>DDx</sub> rising to 4.4V to OUTHx rising |     | 57  | 78  | μs    |

| ULVO Falling t <sub>SHUTOFF</sub> INx = VDDx, V <sub>DDx</sub> falling below 3.9V to OUTLx falling |                    | 0.7                                                                      | 2.5 | 3.5 | μs  |       |

| Turn-On Propagation Delay                                                                          | t <sub>PDR</sub>   | INx to OUTHx, 100pF load                                                 |     | 2.1 | 4   | ns    |

| Turn-Off Propagation Delay                                                                         | t <sub>PDF</sub>   | INx to OUTLx, 100pF load                                                 |     | 1.7 | 4   | ns    |

| Pulse Positive Distortion ( $t_{PDR}$ - $t_{PDF}$ )                                                | $\Delta t_{PD}$    |                                                                          |     | 400 |     | ps    |

| Output Rise Time                                                                                   | t <sub>RISE</sub>  | $0\Omega$ series 100pF load <sup>(1)</sup>                               |     | 720 |     | ps    |

| Output Fall Time                                                                                   | t <sub>FALL</sub>  | 0Ω series 100pF load <sup>1)</sup>                                       |     | 570 |     | ps    |

| Minimum Input Pulse Width                                                                          | t <sub>MIN</sub>   | $0\Omega$ series 100pF load <sup>(1)</sup>                               |     | 1   |     | ns    |

NOTE:

1. Rise and fall are calculated as a 20% to 80%.

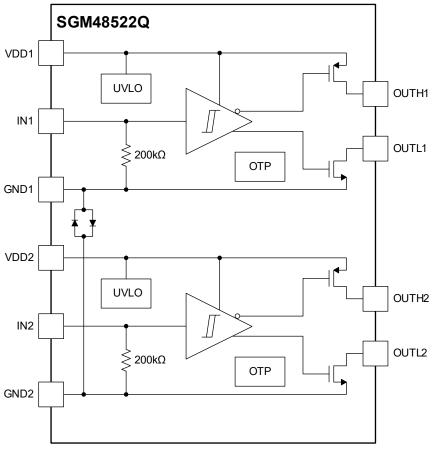

# FUNCTIONAL BLOCK DIAGRAM

Figure 2. Functional Block Diagram

## Automotive Dual 5V, 7A/6A Low-Side GaN and MOSFET Driver

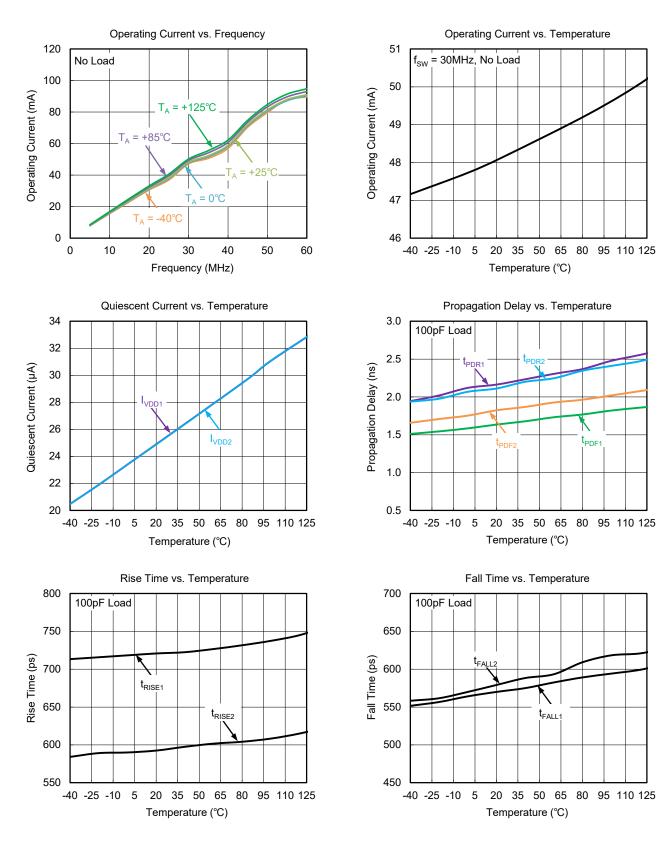

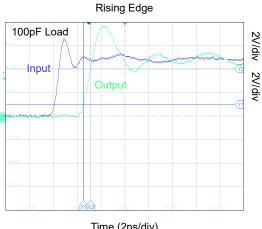

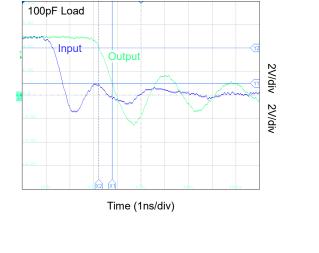

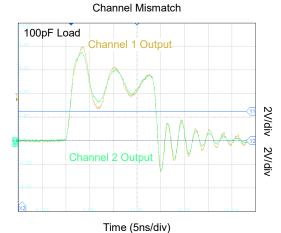

# **TYPICAL PERFORMANCE CHARACTERISTICS**

SG Micro Corp

Falling Edge

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

Time (1ns/div)

SG Micro Corp SGMICRO WWW.Sg-micro.com

# DETAILED DESCRIPTION

The high-speed, dual low-side driver SGM48522Q is designed to drive GaN FETs and logic level MOSFETs. The application areas include LiDAR, time of flight, facial recognition, and power converters using low-side drivers.

SGM48522Q provides the lowest propagation delay of 2ns from the drivers to the power transistors.

#### **Input Stage**

There are Schmitt triggers at the input pins IN1 and IN2 to improve noise immunity. In order to prevent the output from accidentally turning on when the input is in the floating state, IN1 and IN2 are internally connected to pull-down resistors.

#### **Output Stage**

SGM48522Q provides 7A peak source and 6A sink currents, and the outputs are separated to allow custom pull-up and pull-down drive strength to suit the application. The OUTHx and OUTLx pins can be severally connected to transistor gates with separate drive resistors, adjusting the driving speed of turning on and off to control the slew rate and EMI of the driving signal and the ringing on the gate signal. Controlling ringing as much as possible reduces the stress on the driver and switch device, which is very important for high-performance applications and reliability of GaN FETs. In order to prevent the device  $C_{ISS}$  from turning the FET on by mistake, the OUTLx pins will be pulled low in under-voltage conditions.

### VDD and Under-Voltage Lockout

The rated working voltage of SGM48522Q is  $5V \pm 0.5V$ . In the application, the error of the power supply of the driver chip needs to be ensured within 0.5V, and the transient overshoot voltage of the power supply cannot exceed the absolute maximum voltage of the part. In the VDD Overshoot Solution section, there are more specific design details.

SGM48522Q provides independent under-voltage lockout (UVLO) function on each channel to protect the circuits in the event of a fault condition. The UVLO rising trigger point is typically set at 4.18V, and the hysteresis voltage point is 97mV. This UVLO level ensures that the GaN FET operates in the low  $R_{DSON}$  region. When UVLO is triggered, the output is low.

### **Over-Temperature Protection (OTP)**

The SGM48522Q provides independent over-temperature protection (OTP) function for each channel with a trigger point of  $+175^{\circ}$ C. The hysteresis temperature is 23 °C. If the OTP is triggered, switching action is stopped for the channel with the corresponding OUTLx held low. Then when the junction temperature of the device falls below  $+152^{\circ}$ C, normal operation resumes.

# **APPLICATION INFORMATION**

Since the output of the PWM controller cannot often provide the voltage required by the gate of the power device, a high-performance gate driver is usually required between the PWM output of the controller and the gate of the GaN transistor, so that the GaN transistor can operate at correct gate voltages. In addition, the gate driver can reduce switching losses and maximize the performance of GaN transistors in high-frequency applications. Especially in the field of digital power control, it is common for the PWM signal of the digital controller to be a 3.3V logic signal, and GaN transistors cannot work optimally with this gate voltage. The gate driver boosts the 3.3V signal to the preferred gate drive voltage of 5V, which fully turns on the power device and minimizes conduction losses.

The good noise immunity of the SGM48522Q gate driver also minimizes the effects of high frequency switching noise when the driver is placed near the power switch. Adding a gate driver also transfers the gate charge power loss from the controller to the driver, which effectively reduces the power consumption and thermal stress in the controller.

The SGM48522Q is a low-side high-speed gate driver with a maximum operating frequency of 60MHz and an operating voltage of 5V. It is optimized to drive GaN FETs. The output has an independent configuration architecture, which can flexibly adjust the turn-on and turn-off speed, while providing a strong current sinking and sourcing capabilities.

The SGM48522Q is primarily used to drive GaN transistors, which are used in various power converters, LiDAR, wireless chargers, and synchronous rectifiers. The SGM48522Q can be used as a driver for high-speed pulsed laser diodes.

#### **Typical Application**

A typical application circuit for the SGM48522Q is shown in Figure 1, with a dual-channel, 5V drive voltage, specifically designed to drive GaN transistors or logic-level Si FETs. The output has a separated structure, so that the turn-on and turn-off speeds can be controlled separately by driving resistors. If it is not necessary to adjust the turn-on and turn-off speeds separately, OUTHx and OUTLx may be connected directly together (with a single gate drive resistor added if necessary).

In order to avoid voltage overstress caused by the parasitic inductance of the drive circuit, SGMICRO recommends using at least  $2\Omega$  resistors at OUTHx and OUTLx.

For applications requiring a smaller resistance value, please contact SGMICRO E2E for guidance.

#### **Design Requirements**

There are some key factors to consider when designing with the SGM48522Q gate driver and GaN power FETs, especially for high MHz frequency (or nanosecond pulse) applications. These factors include circuit layout, PCB trace design, passive component selection, and maximum operating frequency.

#### Detailed Design Procedure Handling Ground Bounce

Place the ground pin of the SGM48522Q as close as possible to the source of the low-side FET to get the smallest gate current loop, the smallest parasitic inductance, and maximize the switching performance. However, this can cause ground bounce on the SGM48522Q, resulting in incorrect switching logic at the input and wrong level at the output.

In order to eliminate this effect, SGM48522Q has built-in Schmitt triggers on the input terminals to increase the input hysteresis. Equation 1 shows the relationship between the input hysteresis and the maximum allowable di/dt:

$$\frac{di}{dt} = \frac{V_{HYS}}{L_{P}}$$

(1)

#### where

$\label{eq:L_P:Parasitic inductance between source and Ground. $V_{HYS}$: Hysteresis voltage of the input port. $di/dt: Current slew rate.$

# **APPLICATION INFORMATION (continued)**

Assuming that the parasitic inductance is 0.7nH and the hysteresis voltage is 0.7V, the maximum allowable current slew rate is 1A/ns by calculation. If the current slew rate generated in the application is higher than 1A/ns, this exceeds the hysteresis voltage range and causes the output signal to be unstable. Using the inverting input to accept the PWM signal and connecting the non-inverting input to VDD reduce the possibility of false pulses or oscillations and improve stability. High di/dt produces high transient voltage spikes that affect the input of the SGM48522Q. In order to protect the device from a large current spike at INx, a 100 $\Omega$  current limiting resistor can be placed before the INx input.

If the current slew rate is not too high, and the pulse width is not very short (for example, 1ns range), the extra delay can be accepted. The parasitic capacitance of the SGM48522Q input can be used as a good advantage to create an RC filter to reduce high-frequency noise by adding a resistor in series with the input pin. The SGM48522Q has stable input capacitance of about 2.3pF at the input pins, which is convenient for this purpose.

In applications that use current sensing resistors, the ground bounce phenomenon is particularly serious. In the application circuit with current sense resistor, the ground of the SGM48522Q is connected to the source of the GaN FET, and one side of the current sense resistor is connected to the controller ground. In the case of high-speed switching and large current, the potential rebound due to the parasitic inductance of the current detection resistor will cause the circuit to turn on/off by mistake, and in severe cases may cause damage to the device. When the pulse width is not

extremely narrow, a resistor can also be added to the signal output line before SGM48522Q to form an RC filter as a supplement. Although the circuit can improve the ground bounce problem by connecting the ground of the driver to the signal ground after the current sense resistor, this circuit is not recommended. The drawback of this circuit is that the voltage drop across the current sense resistor and its parasitic inductance reduce the transient and DC gate drive voltage to the FET, thus reducing efficiency. In severe cases, the voltage ringing caused by the inductance of the sense resistor path can even cause the FET to spuriously turn on and off.

### **VDD Overshoot Solution**

Due to the existence of PCB parasitic inductance. inductance ringing and transient overshoot voltage are prone to occur under high current switching conditions. In the PCB design process, it is necessary to evaluate and control the overshoot caused by the ringing, so as not to exceed the stress of the device. The strength of the overshoot voltage and the percentage of the overshoot duration to the switching time are parameters that affect the stress. Keeping the overshoot below maximum allowable pin voltage is the best solution. The parasitic inductance can be decreased by optimizing PCB layout. To limit the voltage overshoot, low ESL components and series resistance can be helpful as well. If the overshoot is too large, the accuracy of the power supply needs to be considered. For example, if the overshoot voltage is 0.5V, the maximum error voltage of the power supply cannot exceed 5.5V (10% accuracy). Therefore, if the overshoot voltage is large, a power supply with higher accuracy is necessary.

### **APPLICATION INFORMATION (continued)**

### **Applications at High Frequencies**

SGM48522Q has a rise/fall time of 720ps/570ps, and provides a minimum output capability of 1ns pulse width and a maximum operating frequency of 60MHz. According to the capacitive load, different output modes and frequencies can be selected. Under the working condition of high-frequency pulse, in order to prevent the device from overheating, a high-frequency pulse train with a certain interval time can be used. This can increase the transient frequency and keep the effective value of the output current unchanged. At this time, a larger decoupling capacitor is needed to charge the capacitive load at a high frequency.

#### **Power Supply Recommendations**

In order to provide high peak current when the FET is turned on and improve the stability of the VDD pin supply voltage, a low ESR/ESL ceramic capacitor needs to be used as a bypass capacitor placed as close as possible to the IC's VDD and GND pins. To avoid ringing at the IC pins as much as possible, the decoupling capacitors need to be placed on the same side as the IC, and vias cannot be used.

In order to achieve the best transient performance, SGMICRO recommends choosing a three-terminal capacitor and a capacitor with a larger capacitance in parallel. The three-terminal capacitor needs to be placed close to the VDD and GND pins of the IC, and the other capacitor is placed close to the three-terminal capacitor. The three-terminal capacitor has the lowest ESL, and the larger capacitor provides enough drive peak current. Under normal circumstances, it is recommended to use  $0.1\mu$ F 0402 or through-core capacitors in parallel with  $1\mu$ F 0603 capacitors.

### Layout Guidelines

Proper PCB layout is extremely important in a high-current, fast-switching circuit to provide appropriate device operation and design robustness.

In order to achieve the best performance, a PCB with at least four routing layers is recommended to minimize the parasitic inductance. Using resistors and capacitors in a smaller package (0201) can also minimize inductance and PCB space. It is necessary to calculate the resistor power of a small package to meet the requirements of gate drive power loss.

#### **Drive Loop Inductance and Grounding**

SGM48522Q should be placed as close to the GaN FET as possible, and the trace of the gate drive circuit should be as wide as possible to reduce parasitic inductance.

To achieve minimum drive loop inductance, it is recommended to use the second layer of the PCB as the source loop of the GaN FET, near the bottom of the device (top layer). Both the vias connected to the GND pin and the source of the FET are connected to this layer with minimal impedance. Please note that the coupling of the ground plane will be decreased only when the GND plane is connected to the source power plane at the FET.

#### **Bypass Capacitor**

The VDD pins require bypass capacitors connected to their respective GND pins, placed as close to the pins of the SGM48522Q as possible. The capacitor should be connected to VDD and GND power planes, which should be large and as close to the top layer of the PCB as possible. Due to the high operating frequency of the IC, the inductance of the bypass capacitor is critical, so the value of the bypass capacitor should be between 0.1µF and 1µF, and the material should be X7R or better. The best capacitors for the application are low inductance chip capacitors (LICC), interdigital capacitors (IDC), feedthrough and LGA capacitors. Finally, in order to meet the demand of driving peak current, an extra 1µF capacitor between VDD and GND should be added in parallel close to the IC.

## **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Original (AUGUST 2024) to REV.A    | Page |

|-------------------------------------------------|------|

| Changed from product preview to production data | All  |

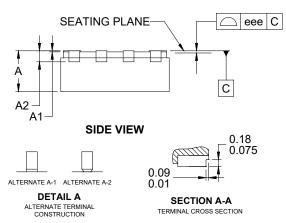

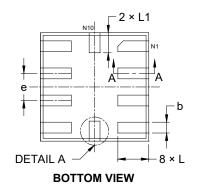

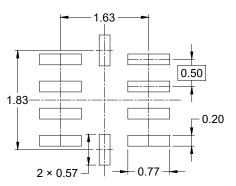

# PACKAGE OUTLINE DIMENSIONS TQFN-2×2-10AL

TOP VIEW

RECOMMENDED LAND PATTERN (Unit: mm)

| Symphol | D     | Dimensions In Millimeters |       |  |  |  |  |

|---------|-------|---------------------------|-------|--|--|--|--|

| Symbol  | MIN   | NOM                       | MAX   |  |  |  |  |

| А       | 0.700 | -                         | 0.800 |  |  |  |  |

| A1      | 0.000 | -                         | 0.050 |  |  |  |  |

| A2      |       | 0.203 REF                 |       |  |  |  |  |

| b       | 0.150 | -                         | 0.250 |  |  |  |  |

| D       | 1.900 | -                         | 2.100 |  |  |  |  |

| E       | 1.900 | -                         | 2.100 |  |  |  |  |

| е       |       | 0.500 BSC                 |       |  |  |  |  |

| L       | 0.470 | -                         | 0.670 |  |  |  |  |

| L1      | 0.270 | -                         | 0.470 |  |  |  |  |

| eee     |       | 0.080                     |       |  |  |  |  |

NOTE: This drawing is subject to change without notice.

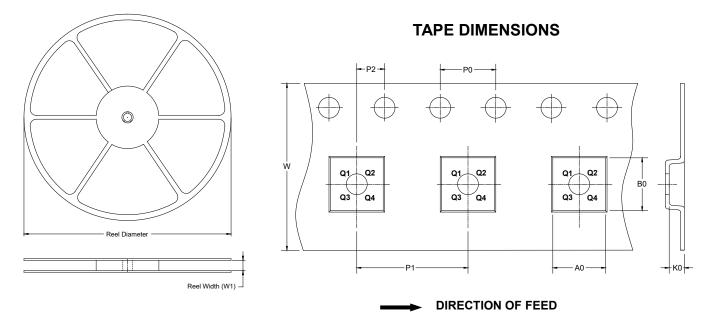

# TAPE AND REEL INFORMATION

### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

### KEY PARAMETER LIST OF TAPE AND REEL

| Package Type  | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| TQFN-2×2-10AL | 7"               | 9.5                      | 2.30       | 2.30       | 1.10       | 4.0        | 4.0        | 2.0        | 8.0       | Q1               |

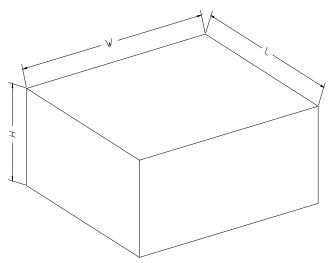

### **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

### **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type   | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |        |

|-------------|----------------|---------------|----------------|--------------|--------|

| 7" (Option) | 368            | 227           | 224            | 8            |        |

| 7"          | 442            | 410           | 224            | 18           | DD0002 |