## SGM41603B I<sup>2</sup>C Controlled 10A Bidirectional Switched-Capacitor Converter

#### GENERAL DESCRIPTION

The SGM41603B is an efficient 2:1/1:2 bidirectional switched-capacitor converter with integrated power switches. It can deliver 10A in forward direction (2:1 voltage divider) and 5A in the reverse direction (1:2 voltage doubler). This device allows using a 2S Li+ power source as a 1S Li+ solution by inserting it between the 2S battery pack and Buck charger output and saves the existing 1S power architecture that is powered from the same battery.

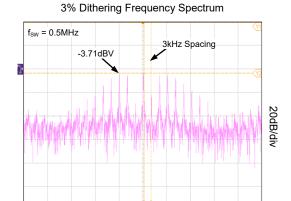

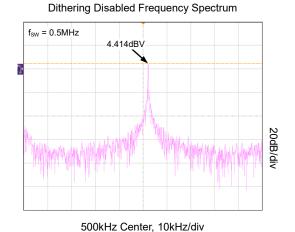

This 2-channel high switching frequency (MAX 1.5MHz) and inductor-less topology allow low profile design with small footprint. The high switching frequency also reduces the size and quantity of the required capacitors. Safe operation is assured by over-voltage, under-voltage, over-current and thermal protections. Interference is also minimized by the built-in frequency dithering option. This device can achieve 99.3% efficiency which is among the highest in its class. Thermal management of such a low loss device is simple that makes it an ideal choice for industrial, consumer, and medical applications.

The I<sup>2</sup>C interface allows flexible parameter settings including OCP, OVLO, switching frequency thresholds and soft-start currents and durations. The SGM41603B is available in a tiny WLCSP-2.85×2.59-42B-A package.

## **APPLICATIONS**

Smartphones, Tablets, Ultrabooks, Chromebooks, DSLR and Mirrorless Cameras, Power Banks, 2S Li+ Battery Applications, Smartphone Direct Charging, Portable Printers, Portable Gaming Devices, Two-Way Radios

#### **FEATURES**

- Bidirectional Switched Capacitor Converter

- Forward Direction 2:1 Conversion, Reverse Direction 1:2 Conversion

- 2-Channel Interleaved Operation (90° or 180°)

- 8 Integrated N-Type MOSFET Switches

- 10A Output Current Capability

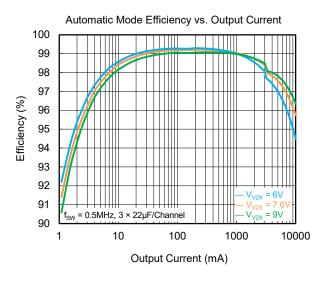

- 99.3% Peak Efficiency

- Low IQ Current: 50µA Forward Operating

- 11µA V2X Consumption Current in Ship Mode

- Support System Reset and Ship Mode

- I<sup>2</sup>C Interface with Interrupt Signaling

- Adjustable Soft-Start Current and Timeout

- 0.25MHz to 1.5MHz Adjustable Switching Frequency

- Low EMI with Switching Frequency Dithering

- Enable Input

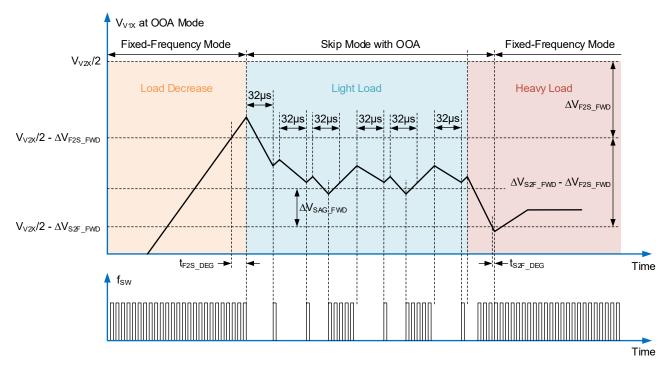

- Out-of-Audio Option at Light Load

- Power Good Output

- Programmable V1X & V2X Over-Voltage Lockout

- Separate OCP Adjustment for Each Direction

- Thermal Alarm and Protection

- Available in a Green WLCSP-2.85×2.59-42B-A Package

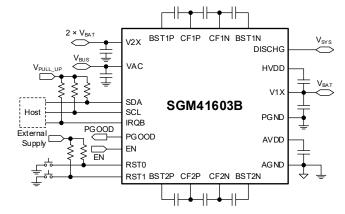

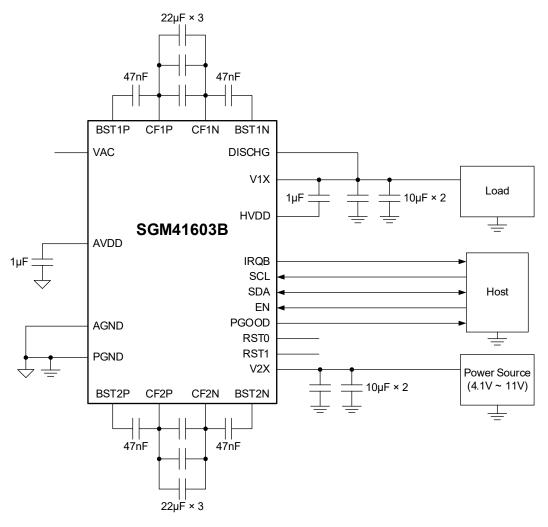

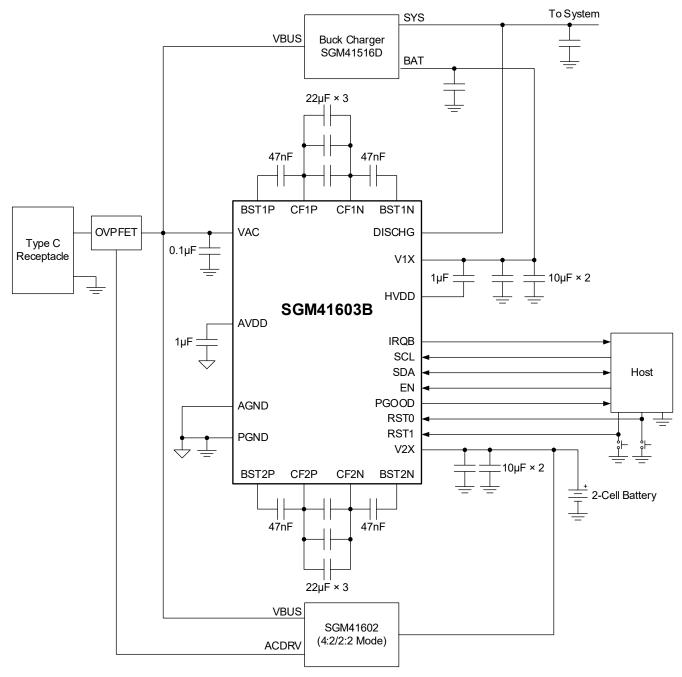

#### TYPICAL APPLICATION

Figure 1. Typical Application Circuit

#### PACKAGE/ORDERING INFORMATION

| MODEL     | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING    | PACKING<br>OPTION   |

|-----------|------------------------|-----------------------------------|--------------------|-----------------------|---------------------|

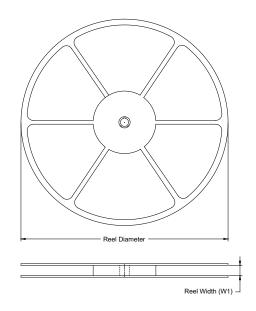

| SGM41603B | WLCSP-2.85×2.59-42B-A  | -40°C to +85°C                    | SGM41603BYG/TR     | 26I<br>XXXXX<br>XX#XX | Tape and Reel, 5000 |

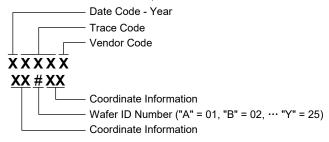

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code. XX#XX = Coordinate Information and Wafer ID Number.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

# I<sup>2</sup>C Controlled 10A Bidirectional Switched-Capacitor Converter

#### **ABSOLUTE MAXIMUM RATINGS**

| VAC to PGND                            | 0.3V to 28V                     |

|----------------------------------------|---------------------------------|

| V2X to PGND                            | 0.3V to 16V                     |

| BSTxP to PGND                          | 0.3V to 16V                     |

| BSTxN to PGND                          | 0.3V to 8V                      |

| BSTxP to CFxP                          | 0.3V to 6V                      |

| BSTxN to CFxN                          | 0.3V to 6V                      |

| CFxP to PGND                           | 0.3V to (V <sub>V1X</sub> + 6V) |

| CFxN to PGND                           | 0.3V to 6V                      |

| V1X to PGND                            | 0.3V to 6V                      |

| PGND to AGND                           | 0.3V to 0.3V                    |

| HVDD to AGND                           | 0.3V to (V <sub>V1X</sub> + 6V) |

| AVDD to AGND                           | 0.3V to 6V                      |

| EN, RST0, RST1 to AGND                 | 0.3V to 16V                     |

| DISCHG, IRQB to AGND                   | 0.3V to 6V                      |

| SCL, SDA to AGND                       | 0.3V to 6V                      |

| PGOOD to AGND                          | 0.3V to 2.0V                    |

| V1X Continuous RMS Current (Forward    | Mode)10A                        |

| Package Thermal Resistance             |                                 |

| WLCSP-2.85×2.59-42B-A, θ <sub>JA</sub> | 38.7°C/W                        |

| WLCSP-2.85×2.59-42B-A, θ <sub>JB</sub> | 6.3°C/W                         |

| WLCSP-2.85×2.59-42B-A, θ <sub>JC</sub> | 14.6°C/W                        |

| Junction Temperature                   | +155°C                          |

| Storage Temperature Range              | 65°C to +155°C                  |

| Lead Temperature (Soldering, 10s)      | +260°C                          |

| ESD Susceptibility (1)(2)              |                                 |

| HBM                                    | ±2000V                          |

| CDM                                    | ±1000V                          |

|                                        |                                 |

#### NOTES:

- 1. For human body model (HBM), all pins comply with ANSI/ESDA/JEDEC JS-001 specifications.

- 2. For charged device model (CDM), all pins comply with ANSI/ESDA/JEDEC JS-002 specifications.

#### RECOMMENDED OPERATING CONDITIONS

| VAC                                         | 22V (MAX)      |

|---------------------------------------------|----------------|

| V2X (Forward Mode) (3)                      | 4.1V to 11V    |

| V1X (Reverse Mode) (4)                      |                |

| I <sub>V1X</sub> (Forward Mode, Continuous) | 0A to 10A      |

| I <sub>V2X</sub> (Reverse Mode, Continuous) | 0A to 5A       |

| (BST1P - CF1P), (BST1N - CF1N)              | 0V to 5V       |

| (CF1P - V1X), CF1N                          | 0V to 5.5V     |

| (BST2P - CF2P), (BST2N - CF2N)              | 0V to 5V       |

| (CF2P - V1X), CF2N                          | 0V to 5.5V     |

| AVDD, (HVDD - V1X)                          | 0V to 5V       |

| EN, RST0, RST1                              | 0V to 12V      |

| PGOOD                                       | 0V to 1.8V     |

| DISCHG, SDA, SCL, IRQB                      | 0V to 5V       |

| Junction Temperature Range                  | 40°C to +125°C |

#### NOTES:

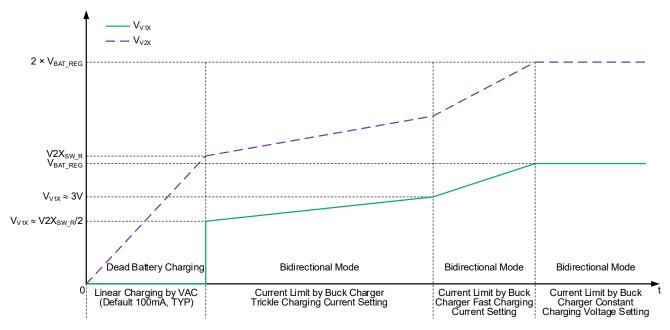

- 3. The V2X voltage must be higher than  $V2X_{SW_R}$  for switching, and the SGM41603B can switch down to 4.1V V2X voltage after starting switching.

- 4. The V1X voltage must be higher than V1 $X_{SW_R}$  for switching, and the SGM41603B can switch down to 2.7V V1X voltage after starting switching.

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

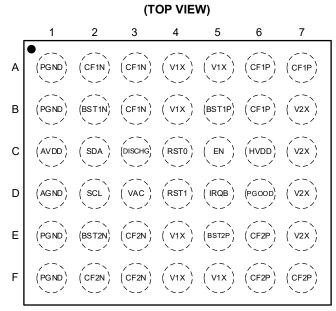

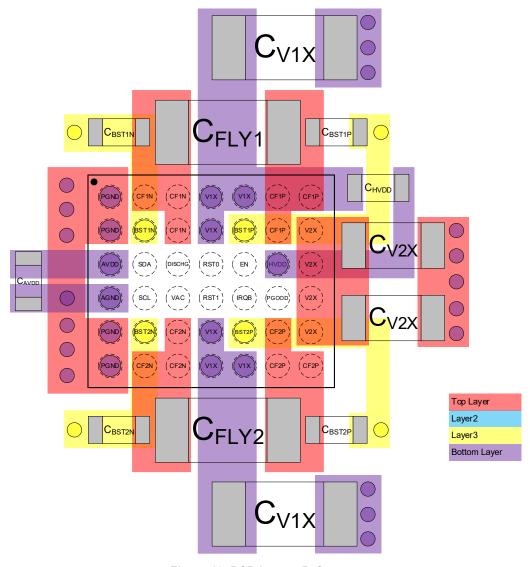

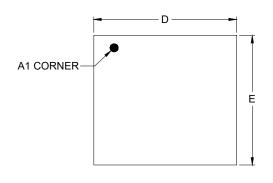

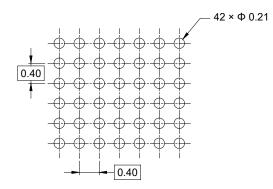

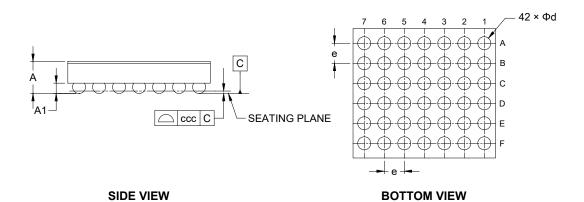

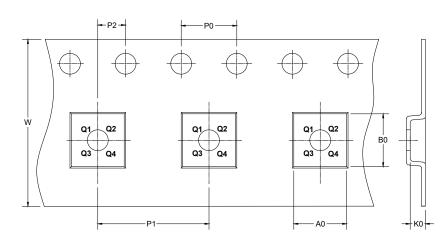

#### **PIN CONFIGURATION**

WLCSP-2.85×2.59-42B-A

## **PIN DESCRIPTION**

| PIN                       | NAME   | TYPE (1) | FUNCTION                                                                                                                                                                                                                                                                                                                                       |

|---------------------------|--------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, B1, E1, F1            | PGND   | Р        | Power Ground.                                                                                                                                                                                                                                                                                                                                  |

| A2, A3, B3                | CF1N   | Р        | Channel-1 Flying Capacitor Negative Node. Connect three parallel 22µF capacitors between CF1P and CF1N pins as close as possible to these pins.                                                                                                                                                                                                |

| A4, A5, B4,<br>E4, F4, F5 | V1X    | Р        | Lower Voltage (1X) Power Port. It is an output in forward mode and an input in reverse mode. Two 10µF capacitors are recommended to be placed between V1X and PGND.                                                                                                                                                                            |

| A6, A7, B6                | CF1P   | Р        | Channel-1 Flying Capacitor Positive Node. Connect three parallel 22µF capacitors between CF1P and CF1N pins as close as possible to these pins.                                                                                                                                                                                                |

| B2                        | BST1N  | Р        | Bootstrap Capacitor Connection for $Q_{CL1}$ Gate Driver Supply. Place a 47nF or larger ceramic capacitor between this pin and CF1N.                                                                                                                                                                                                           |

| B5                        | BST1P  | Р        | Bootstrap Capacitor Connection for Q <sub>CH1</sub> Gate Driver Supply. Place a 47nF or larger ceramic capacitor between this pin and CF1P.                                                                                                                                                                                                    |

| B7, C7, D7, E7            | V2X    | Р        | Higher Voltage (2X) Power Port. It is an input in forward mode and an output in reverse mode. Two 10µF capacitors are recommended to be placed between V2X and PGND.                                                                                                                                                                           |

| C1                        | AVDD   | AO       | 5V LDO Output. Decouple AVDD to AGND with at least 1µF high quality ceramic capacitor (X5R or better). Do not connect any external load to AVDD.                                                                                                                                                                                               |

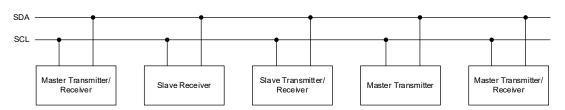

| C2                        | SDA    | DIO      | I <sup>2</sup> C Interface Data Line. The SDA line is forced to release when the I <sup>2</sup> C timeout fault occurs.                                                                                                                                                                                                                        |

| C3                        | DISCHG | AIO      | System Discharge Pin in Reset Mode. When both RST0 and RST1 are low for at least $t_{\text{SYS\_RST}}$ , chip discharges the DISCHG pin with 10mA sink for 500ms. Keep it short to V1X if not used.                                                                                                                                            |

| C4                        | RST0   | DI       | Reset Input 0. 1.8V Internal Pull-up.  1. If VAC is not present, when both RST0 and RST1 are low for at least t <sub>SYS_RST</sub> , chip stops switching and discharges the DISCHG pin with 10mA sink for 500ms.  2. When RST0 keeps low for t <sub>SHIPMODE</sub> , chip exits the ship mode.  Keep it floating or short to V1X if not used. |

| C5                        | EN     | DI       | Active High Device Enable Input.                                                                                                                                                                                                                                                                                                               |

| C6                        | HVDD   | AO       | $(V_{V1X}$ + 5V) LDO Output. Decouple HVDD to V1X with at least $1\mu F$ high quality ceramic capacitor (X5R or better). Do not connect any external load to HVDD.                                                                                                                                                                             |

| D1                        | AGND   | Р        | Analog Ground.                                                                                                                                                                                                                                                                                                                                 |

| D2                        | SCL    | DI       | I <sup>2</sup> C Interface Clock Line. The device I <sup>2</sup> C controller block is forced to reset when receiving 9 clock pulses on the SCL line.                                                                                                                                                                                          |

| D3                        | VAC    | Р        | VBUS Sense and Power Supply for Internal Circuit. Bypass this pin to AGND with at least 0.1µF high quality ceramic capacitor (X5R or better). Keep it floating or short to ground if not used.  When VAC OVP is triggered, device will stop the linear charging current if it exists.                                                          |

| D4                        | RST1   | DI       | Reset Input 1. 1.8V Internal Pull-up. When both RST0 and RST1 are low for t <sub>SYS_RST</sub> , chip stops switching and discharges the DISCHG pin with 10mA sink for 500ms. Keep it floating or short to V1X if not used.                                                                                                                    |

| D5                        | IRQB   | DO       | Open-Drain Active Low Interrupt Output. A low on IRQB indicates a fault condition. The external pull-up resistor should be greater than $1k\Omega$ .                                                                                                                                                                                           |

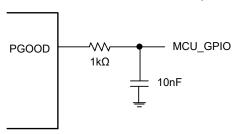

| D6                        | PGOOD  | DO       | Power Good Output.                                                                                                                                                                                                                                                                                                                             |

| E2                        | BST2N  | Р        | Bootstrap Capacitor Connection for $Q_{\text{CL2}}$ Gate Driver Supply. Place a 47nF or larger ceramic capacitor between this pin and CF2N.                                                                                                                                                                                                    |

| E3, F2, F3                | CF2N   | Р        | Channel-2 Flying Capacitor Negative Node. Connect three parallel 22µF capacitors between CF2P and CF2N pins as close as possible to these pins.                                                                                                                                                                                                |

| E5                        | BST2P  | Р        | Bootstrap Capacitor Connection for $Q_{\text{CH2}}$ Gate Driver Supply. Place a 47nF or larger ceramic capacitor between this pin and CF2P.                                                                                                                                                                                                    |

| E6, F6, F7                | CF2P   | Р        | Channel-2 Flying Capacitor Positive Node. Connect three parallel 22µF capacitors between CF2P and CF2N pins as close as possible to these pins.                                                                                                                                                                                                |

NOTE:

1. P = Power, AO = Analog Output, AIO = Analog Input/Output, DI = Digital Input, DO = Digital Output, DIO = Digital Input/Output.

## **ELECTRICAL CHARACTERISTICS**

$(V_{V2X} = 7.6V, V_{V1X} = 3.8V, f_{SW} = 0.5MHz, T_J = -40^{\circ}C$  to +85°C, typical values are at  $T_J = +25^{\circ}C$ , unless otherwise specified.)

| PARAMETER                                       | SYMBOL                 | CONDITIONS                                                                                                                                                                                                             | MIN                 | TYP  | MAX                  | UNITS |  |

|-------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|----------------------|-------|--|

|                                                 | STIVIBUL               | CONDITIONS                                                                                                                                                                                                             | IVIIIN              | IIF  | IVIAA                | UNITS |  |

| Global Input Supply                             |                        | 0.0                                                                                                                                                                                                                    |                     | 44   | 40                   |       |  |

|                                                 | I <sub>SHDN_V2X</sub>  | Ship mode, V <sub>V2X</sub> = 8.4V, T <sub>J</sub> = +25°C                                                                                                                                                             |                     | 11   | 18                   |       |  |

| Shutdown Supply Current                         |                        | EN = low, SCC_EN = 0, V <sub>V2X</sub> = 8.4V                                                                                                                                                                          |                     | 11   |                      | μA    |  |

|                                                 | I <sub>SHDN_V1X</sub>  | EN = low, SCC_EN = 0, V <sub>V1X</sub> = 4.2V                                                                                                                                                                          |                     | 11   |                      |       |  |

|                                                 | I <sub>Q_V2X</sub>     | V <sub>V2X</sub> = 8.4V, automatic mode                                                                                                                                                                                | 50                  |      | μA                   |       |  |

| Quiescent Current                               | I <sub>Q_V2X_OOA</sub> | V <sub>V2X</sub> = 8.4V, Out-of-Audio mode                                                                                                                                                                             |                     | 760  |                      | · ·   |  |

| <b>4</b>                                        | I <sub>Q_V1X</sub>     | $V_{V1X}$ = 4.2V, automatic mode                                                                                                                                                                                       |                     | 100  |                      | μA    |  |

|                                                 | I <sub>Q_V1X_OOA</sub> | $V_{V1X}$ = 4.2V, Out-of-Audio mode                                                                                                                                                                                    |                     | 1550 |                      | μ, τ  |  |

| V1X Leakage Current                             | I <sub>LK_V1X</sub>    | $V_{V2X} = 4.2V$ , $V1X_AD_EN = 0$ , $EN = low$                                                                                                                                                                        |                     | 0.1  |                      | μΑ    |  |

| Input Under-Voltage Lockout                     |                        |                                                                                                                                                                                                                        |                     |      |                      |       |  |

|                                                 | V2X <sub>UVLO_R</sub>  | V <sub>V2X</sub> rising                                                                                                                                                                                                |                     | 3.20 | 3.55                 |       |  |

|                                                 | V2X <sub>UVLO_F</sub>  | V <sub>V2X</sub> falling                                                                                                                                                                                               |                     | 2.90 |                      |       |  |

| Under-Voltage Lockout Threshold                 | V1X <sub>UVLO_R</sub>  | V <sub>V1X</sub> rising                                                                                                                                                                                                |                     | 2.77 | 2.97                 | V     |  |

|                                                 | V1X <sub>UVLO_F</sub>  | V <sub>V1X</sub> falling                                                                                                                                                                                               |                     | 2.47 |                      |       |  |

|                                                 | VX <sub>UVLO_HYS</sub> | V1X, V2X UVLO hysteresis                                                                                                                                                                                               |                     | 0.3  |                      |       |  |

| Enable Inputs and Logic                         |                        |                                                                                                                                                                                                                        |                     |      |                      | •     |  |

| EN Deglitch Time                                | t <sub>EN_DEG</sub>    | Deglitch between $V_{EN}$ rising over $V_{IH}$ and starting soft-start action, when $t_{EN\_DEG} = 0.125 ms$ ( $I^2C$ programmable from 0.125ms to 64ms, default 0.125ms)                                              |                     |      |                      | ms    |  |

| Logic Input Low Level                           | V <sub>IL</sub>        | EN pin                                                                                                                                                                                                                 |                     |      | 0.4                  | V     |  |

| Logic Input High Level                          | V <sub>IH</sub>        | EN pin                                                                                                                                                                                                                 | 1.1                 |      |                      | V     |  |

| EN Pull-Down Resistance                         | R <sub>EN_PD</sub>     | Pulled down to AGND                                                                                                                                                                                                    |                     | 1.5  |                      | ΜΩ    |  |

| EN Input Leakage Current                        | I <sub>LK_EN</sub>     | EN pin connected to 3.3V, RPUPD_EN = 0                                                                                                                                                                                 |                     | 0.1  |                      | μA    |  |

| IRQB Pin Output High Leakage                    | I <sub>LK_IRQB</sub>   | IRQB pin, V <sub>IRQB</sub> = 5.5V                                                                                                                                                                                     |                     | 0.1  |                      | μA    |  |

| Switched-Capacitor Converter                    |                        |                                                                                                                                                                                                                        |                     |      |                      | •     |  |

|                                                 | V2X <sub>SW_R</sub>    | Rising, when V2X <sub>SW_F</sub> = 3.8V                                                                                                                                                                                |                     | 4.0  |                      |       |  |

|                                                 | V2X <sub>SW_F</sub>    | Falling, when $V2X_{SW\_F} = 3.8V$ ( $I^2C$ programmable from 3.8V to 4.4V, 0.2V per step, default 3.8V)                                                                                                               |                     | 3.8  |                      |       |  |

| Thresholds for Switching                        | V1X <sub>SW_R</sub>    | Rising, when V1X <sub>SW_F</sub> = 2.6V                                                                                                                                                                                |                     | 2.8  |                      | V     |  |

|                                                 | V1X <sub>SW_F</sub>    | Falling, when V1X <sub>SW_F</sub> = 2.6V ( $I^2$ C programmable from 2.6V to 2.7V, 0.1V per step, default 2.6V)                                                                                                        |                     | 2.6  |                      |       |  |

|                                                 | VX <sub>SW_HYS</sub>   | V1X, V2X switching threshold hysteresis                                                                                                                                                                                |                     | 0.2  |                      |       |  |

| Switching Stop Deglitch Time                    | t <sub>SW_F_DEG</sub>  | Deglitch time between the time of $V_{V1X}$ or $V_{V2X}$ falling below its switching threshold and stopping the switching action, when $t_{SW\_F\_DEG} = 108\mu s$ ( $I^2C$ programmable from 0ms to 1ms, default 0ms) |                     | 108  |                      |       |  |

| Input Operating Valters Desire                  | $V_{V2X}$              |                                                                                                                                                                                                                        | V2X <sub>SW_F</sub> |      | V2X <sub>OVP_R</sub> | V     |  |

| Input Operating Voltage Range                   | V <sub>V1X</sub>       |                                                                                                                                                                                                                        | V1X <sub>SW_F</sub> |      | V1X <sub>OVP_R</sub> | V     |  |

| Forward Mode Soft-Start<br>Current (all at V1X) | I <sub>SS_FWD</sub>    |                                                                                                                                                                                                                        |                     | 30   |                      | mA    |  |

## ELECTRICAL CHARACTERISTICS (continued) (Vyzy = 7.6V, Vyzy = 3.8V, f<sub>SW</sub> = 0.5MHz, T<sub>1</sub> = -40°C to +85°C, typical values are at T<sub>1</sub> = +25°C, unless otherwise specified.)

| PARAMETER                                                  | SYMBOL                    | CONDITIONS                                                                                                                                   | MIN  | TYP  | MAX  | UNITS |  |

|------------------------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|--|

| Valid V2X Voltage During<br>Soft-Start                     | V2X <sub>VALID</sub>      | $V_{VZX}$ rising, threshold for enabling skip mode at light load, when $V2X_{VALID} = 6V$ ( $I^2C$ programmable from 5.6V to 6V, default 6V) |      | 6    |      | V     |  |

| Light Load Efficiency                                      | η <sub>LIGHT1_FWD</sub>   | I <sub>V1X</sub> = 1mA, V <sub>V2X</sub> = 7.4V                                                                                              |      | 90.8 |      | %     |  |

| Light Load Efficiency                                      | η <sub>LIGHT2_FWD</sub>   | I <sub>V1X</sub> = 30mA, V <sub>V2X</sub> = 7.4V                                                                                             |      | 99.1 |      | %     |  |

| Light Load Efficiency                                      | η <sub>LIGHT3_FWD</sub>   | I <sub>V1X</sub> = 100mA, V <sub>V2X</sub> = 7.4V                                                                                            |      | 99.3 |      | %     |  |

| Light Load Efficiency                                      | η <sub>LIGHT4_FWD</sub>   | I <sub>V1X</sub> = 1A, V <sub>V2X</sub> = 7.4V                                                                                               |      | 99.1 |      | %     |  |

| Heavy Load Efficiency                                      | η <sub>HEAVY_FWD</sub>    | I <sub>V1X</sub> = 10A, V <sub>V2X</sub> = 9V                                                                                                |      | 96.4 |      | %     |  |

| Light Load Efficiency (Reverse)                            | η <sub>LIGHT1_RVS</sub>   | I <sub>V2X</sub> = 1mA, V <sub>V1X</sub> = 3.7V                                                                                              |      | 94.3 |      | %     |  |

| Heavy Load Efficiency (Reverse)                            | η <sub>HEAVY_RVS</sub>    | I <sub>V2X</sub> = 5A, V <sub>V1X</sub> = 4.5V                                                                                               |      | 96.3 |      | %     |  |

| R <sub>DSON</sub> of Q <sub>CH1</sub> and Q <sub>CH2</sub> | R <sub>DS_QCH</sub>       | V <sub>V2X</sub> = 7.6V, V <sub>V1X</sub> = 3.8V, I <sub>V1X</sub> = 0.5A                                                                    |      | 13   |      |       |  |

| R <sub>DSON</sub> of Q <sub>DH1</sub> and Q <sub>DH2</sub> | R <sub>DS_QDH</sub>       | V <sub>V2X</sub> = 7.6V, V <sub>V1X</sub> = 3.8V, I <sub>V1X</sub> = 0.5A                                                                    |      | 11   |      | 0     |  |

| R <sub>DSON</sub> of Q <sub>CL1</sub> and Q <sub>CL2</sub> | R <sub>DS_QCL</sub>       | V <sub>V2X</sub> = 7.6V, V <sub>V1X</sub> = 3.8V, I <sub>V1X</sub> = 0.5A                                                                    |      | 10   |      | mΩ    |  |

| R <sub>DSON</sub> of Q <sub>DL1</sub> and Q <sub>DL2</sub> | R <sub>DS_QDL</sub>       | V <sub>V2X</sub> = 7.6V, V <sub>V1X</sub> = 3.8V, I <sub>V1X</sub> = 0.5A                                                                    |      | 10   |      |       |  |

| Switching Frequency                                        | f <sub>sw</sub>           | When $f_{SW}$ = 500kHz ( $I^2$ C programmable from 250kHz to 1.5MHz, default 500kHz)                                                         | 440  | 500  | 560  | kHz   |  |

| Switching Frequency Dither<br>Rate                         | f <sub>SW_DTHR</sub>      | When $f_{SW\_DTHR} = 3\%$ ( $I^2C$ programmable from 3% to 12% or OFF, default OFF)                                                          |      | ±3   |      | %     |  |

| Active Discharge Desistance                                | R <sub>AD_V2X</sub>       | Active discharge is analysed SCC is dischlad                                                                                                 |      | 10   |      | 1.0   |  |

| Active Discharge Resistance R <sub>AD_V13</sub>            |                           | Active discharge is enabled, SCC is disabled                                                                                                 |      | 1    |      | kΩ    |  |

| Protections                                                |                           |                                                                                                                                              |      |      |      |       |  |

|                                                            | V2X <sub>OVP_R</sub>      | Rising, when V2X <sub>OVP_R</sub> = 8.7V<br>(I <sup>2</sup> C programmable from 8.3V to 11V, default 10.5V)                                  | 8.48 | 8.7  | 8.92 |       |  |

| Over-Voltage Protection                                    | V2X <sub>OVP_HYS</sub>    | V2X OVP Hysteresis                                                                                                                           |      | 0.2  |      |       |  |

| Threshold                                                  | V1X <sub>OVP_R</sub>      | Rising, when V1X <sub>OVP,R</sub> = 4.35V (I <sup>2</sup> C programmable from 4.15V to 5.5V, default 5.3V)                                   | 4.3  | 4.35 | 4.4  | V     |  |

|                                                            | V1X <sub>OVP_HYS</sub>    | V1X OVP Hysteresis                                                                                                                           |      | 0.1  |      |       |  |

| V1X OCP1 Threshold<br>(Bidirectional)                      | I <sub>V1X_OCP1</sub>     | When $I_{V1X\_OCP1}$ = 16.5A ( $I^2C$ programmable from 13.2A to 20.9A, default 16.5A)                                                       |      | 16.5 |      | А     |  |

| V1X OCP1 Accuracy                                          | I <sub>V1X_OCP1_ACC</sub> | In the entire I <sub>V1X_OCP1</sub> range, T <sub>J</sub> = +25°C                                                                            | -12  |      | 12   | %     |  |

| 0000 05                                                    | V1X <sub>OCP2</sub>       | When V1X <sub>OCP2</sub> = 340mV<br>(I <sup>2</sup> C programmable from 100mV to 660mV, default 340mV)                                       |      | 340  |      |       |  |

| OCP2 Offset                                                | V2X <sub>OCP2</sub>       | When V2X <sub>OCP2</sub> = 580mV<br>(I <sup>2</sup> C programmable from 300mV to 860mV,<br>40mV per step, default 580mV)                     |      | 580  |      | mV    |  |

| Thermal Alarms and Shutdown                                | I                         | , , , , , , , , , , , , , , , , , , , ,                                                                                                      |      | •    |      |       |  |

| Thermal Alarm at +100°C                                    | T <sub>DIE_ALM_100</sub>  | T <sub>J</sub> rising, +15°C hysteresis                                                                                                      |      | 100  |      | °C    |  |

| Thermal Alarm at +120°C                                    | T <sub>DIE_ALM_120</sub>  | T <sub>J</sub> rising, +15°C hysteresis                                                                                                      |      | 120  |      | °C    |  |

| Thermal Shutdown Rising                                    | -                         |                                                                                                                                              |      | 455  |      |       |  |

| Threshold Thermal Shutdown Rising                          | T <sub>DIE_OTP_R</sub>    |                                                                                                                                              |      | 155  |      | °C    |  |

## **ELECTRICAL CHARACTERISTICS (continued)** $(V_{V2X} = 7.6V, V_{V1X} = 3.8V, f_{SW} = 0.5MHz, T_J = -40^{\circ}C$ to +85°C, typical values are at $T_J = +25^{\circ}C$ , unless otherwise specified.)

| $\begin{array}{c} (V_{V2X} = 7.6V, V_{V1X} = 3.8V, I_{SW}) \\ \hline \textbf{PARAMETER} \end{array}$ | SYMBOL                      | J = -40°C to +85°C, typical values are at T <sub>J</sub> =                                                              | +25 C, un<br>MIN | TYP     | MAX   | UNITS |

|------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------|---------|-------|-------|

| SDA and SCL I/O Stage                                                                                | OTHIDOL                     | CONDITIONS                                                                                                              | IIIII            | • • • • | IIIAX | ONTO  |

| Input Logic Low Level                                                                                | $V_{\text{IL\_I2C}}$        |                                                                                                                         |                  |         | 0.36  | V     |

| Input Logic High Level                                                                               | V <sub>IL_I2C</sub>         |                                                                                                                         | 0.92             |         | 0.00  | V     |

| SCL, SDA Logic Input Leakage Current                                                                 | I <sub>IN_LK</sub>          | V <sub>SCL</sub> = V <sub>SDA</sub> = 1.8V                                                                              | -1               |         | 1     | μA    |

| SCL, SDA Input Capacitance                                                                           | C <sub>IN_I2C</sub>         |                                                                                                                         |                  | 10      |       | pF    |

| Output Low Voltage (SDA only)                                                                        | V <sub>OL_SDA</sub>         | Sinking 5mA                                                                                                             |                  |         | 0.4   | V     |

|                                                                                                      |                             | d, Fast, and Fast-Mode Plus Speeds                                                                                      |                  |         |       |       |

| Clock Frequency                                                                                      | f <sub>SCL</sub>            |                                                                                                                         |                  |         | 1000  | kHz   |

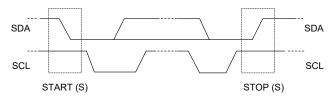

| Hold Time (Repeated) START Condition                                                                 | t <sub>HD;STA</sub>         |                                                                                                                         | 0.26             |         |       | μs    |

| CLK Low Period                                                                                       | t <sub>LOW</sub>            |                                                                                                                         | 0.5              |         |       | μs    |

| CLK High Period                                                                                      | t <sub>HIGH</sub>           |                                                                                                                         | 0.26             |         |       | μs    |

| Setup Time Repeated START Condition                                                                  | t <sub>SU;STA</sub>         |                                                                                                                         | 0.26             |         |       | μs    |

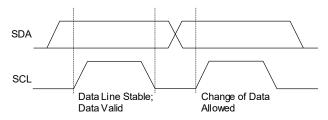

| DATA Hold Time                                                                                       | t <sub>HD:DAT</sub>         |                                                                                                                         | 0                |         |       | μs    |

| DATA Valid Time                                                                                      | t <sub>VD:DAT</sub>         |                                                                                                                         |                  |         | 0.45  | μs    |

| DATA Valid Acknowledge Time                                                                          | t <sub>VD:ACK</sub>         |                                                                                                                         |                  |         | 0.45  | μs    |

| DATA Setup time                                                                                      | t <sub>SU;DAT</sub>         |                                                                                                                         | 50               |         |       | ns    |

| Setup Time for STOP Condition                                                                        | t <sub>su;sto</sub>         |                                                                                                                         | 0.26             |         |       | μs    |

| Bus-Free Time Between STOP and START                                                                 | t <sub>BUF</sub>            |                                                                                                                         | 0.5              |         |       | μs    |

| Pulse Width of Spikes that Must<br>be Suppressed by the Input<br>Filter                              | t <sub>SP</sub>             |                                                                                                                         |                  | 50      |       | ns    |

| Ship Mode and System Reset                                                                           |                             |                                                                                                                         |                  |         |       |       |

| System Reset Time                                                                                    | t <sub>sys_PD</sub>         | DISCHG pin pulling down time                                                                                            |                  | 0.5     |       | s     |

| System Reset Confirmation Time                                                                       | t <sub>sys_rst</sub>        | By pulling down both RST0 and RST1                                                                                      |                  | 10      |       | s     |

| Exit Shipping Mode Time                                                                              | t <sub>SHIPMODE</sub>       | By pulling down RST0                                                                                                    |                  | 2       |       | s     |

| Delay Time for Entering Ship Mode                                                                    | t <sub>SHIPMODE_DELAY</sub> | I <sup>2</sup> C programmable from 20s to 30s, 10s per step, default 20s                                                |                  | 20      |       | s     |

| VAC Threshold and Related Fu                                                                         | nction                      |                                                                                                                         |                  |         |       |       |

| VAC Present                                                                                          | V                           | Rising Threshold                                                                                                        |                  | 3.75    |       | V     |

| VAC Fleseni                                                                                          | V <sub>VAC_PRESENT</sub>    | Hysteresis                                                                                                              |                  | 100     |       | mV    |

| VAC UVLO                                                                                             | V                           | Rising Threshold                                                                                                        |                  | 3.20    | 3.55  | V     |

| VAO OVEO                                                                                             | V <sub>VAC_UVLO</sub>       | Hysteresis                                                                                                              |                  | 300     |       | mV    |

| Linear Charging Current to V2X                                                                       | I <sub>SRC_V2X</sub>        | $V_{VAC}$ = 5V, $V_{V2X}$ = 3V, from VAC to V2X ( $I^2C$ programmable from 50mA to 200mA, 50mA per step, default 100mA) |                  | 100     |       | mA    |

| VAC OVP                                                                                              | $V_{VAC\_OVP\_R}$           | Rising threshold for V <sub>VAC_OVP</sub> = 14V                                                                         |                  | 14      |       | V     |

| V/10 OVI                                                                                             | $V_{\text{VAC\_OVP\_HYS}}$  | Hysteresis                                                                                                              |                  | 100     |       | mV    |

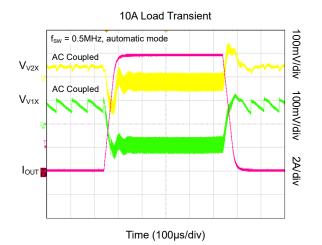

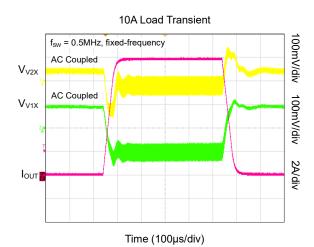

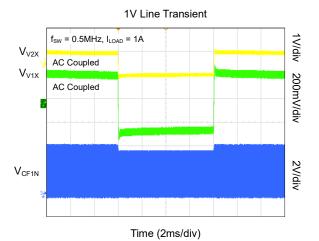

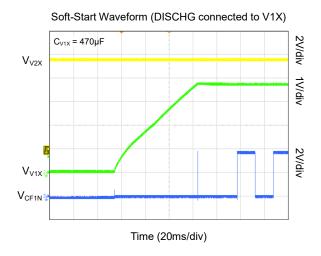

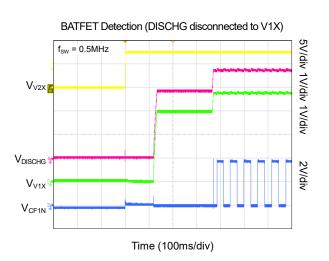

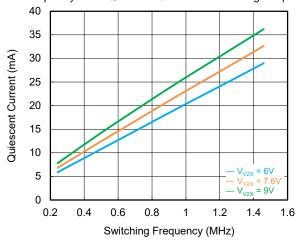

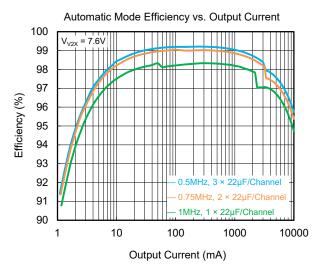

## TYPICAL PERFORMANCE CHARACTERISTICS

$V_{V2X}$  = 7.6V,  $C_{FLY}$ /channel = 3 × 22 $\mu$ F,  $f_{SW}$  = 0.5MHz, unless otherwise specified.

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$V_{V2X}$  = 7.6V,  $C_{FLY}$ /channel = 3 × 22 $\mu$ F,  $f_{SW}$  = 0.5MHz, unless otherwise specified.

500kHz Center, 10kHz/div

Fixed-Frequency Mode Quiescent Current vs. Switching Frequency

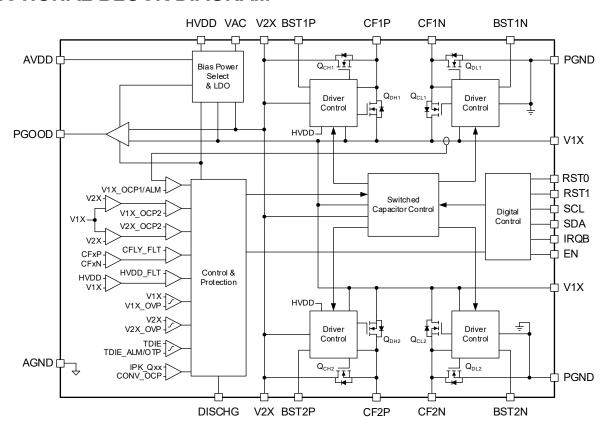

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. SGM41603B Block Diagram

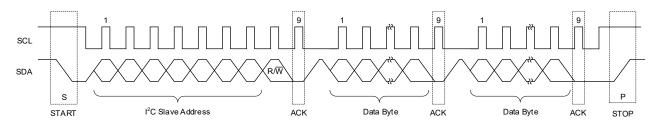

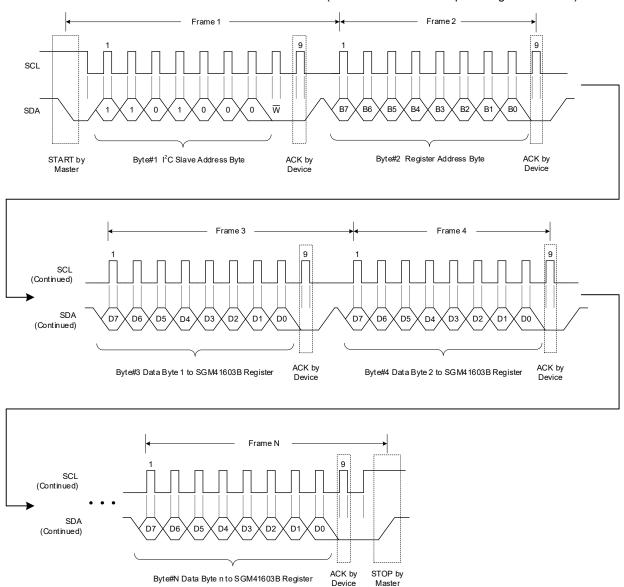

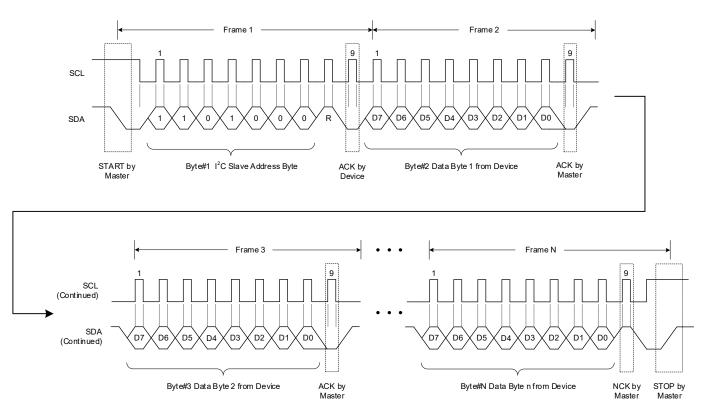

## I<sup>2</sup>C REGISTERS ADDRESS MAP

7-Bit I<sup>2</sup>C Slave Device Address: 0b1101 000 + W/R

| FUNCTION         | FLAG    | MASK    | STATUS  | THRESHOLD SETTING     | ENABLE                                          | DEGLITCH            |

|------------------|---------|---------|---------|-----------------------|-------------------------------------------------|---------------------|

| REG_RST          | I LAG   |         |         |                       | 0x05[6]                                         | DEGETTOT!           |

| WDT TIMEOUT      | 0x12[3] |         |         | 0x12[2:0]             | 0x12[2:0]                                       |                     |

| VAC OVP          |         |         | 0x15[6] | 0x15[5]               | 0x12[2.0]                                       |                     |

| V2X OVP          | 0x00[7] | 0x01[7] | 0x15[0] | 0x08[7:3]             | 0x08[7:3]                                       |                     |

| V1X_OVP          | 0x00[7] | 0x01[7] | 0x02[7] | 0x09[4:0]             | 0x09[4:0]                                       |                     |

| V1X_OC_ALM       | 0x00[6] | 0x01[6] | 0x02[0] | 0x09[4.0]             | 0.09[4.0]                                       |                     |

|                  |         |         |         | V1X_OCP1: 0x0A[2:0]   | V1X_OCP1: 0x07[7]                               | V1X_OCP1: 0x0A[4:3] |

| V1X_OCP          | 0x00[4] | 0x01[4] |         | V1X_OCP2: 0x0B[3:0]   | V1X_OCP2: 0x0B[3:0]                             | V1X_OCP2: 0x0C[7:6] |

| T_ALM1           | 0x00[3] | 0x01[3] | 0x02[3] | -                     |                                                 |                     |

| T_ALM2           | 0x00[2] | 0x01[2] | 0x02[2] |                       |                                                 |                     |

| T_SHDN           | 0x00[1] | 0x01[1] | 0x02[1] |                       |                                                 |                     |

| FSS_FLT          | 0x00[0] | 0x01[0] |         | FWD_SS_TMO: 0x0C[2:0] |                                                 |                     |

| CONV_OCP_INT     | 0x03[3] | 0x04[3] |         | -                     |                                                 |                     |

| LIN_CHG          |         |         | 0x10[4] | 0x11[1:0]             |                                                 |                     |

| LIN_CHG_TMO_INT  | 0x10[0] | 0x10[2] | 0x10[6] |                       |                                                 |                     |

| LIN_CHARGE_DELAY |         | -       | 0x15[1] | 0x11[3:2]             |                                                 |                     |

| VFWD_SS_VOLT     | 1       | ı       | I       | 0x11[6:4]             |                                                 |                     |

| SHIP_MODE        | 0x10[1] | 0x10[3] | 0x10[5] | -                     | EN_SHIP_MODE: 0x05[4]<br>SHIP MODE KEY: 0x06[6] |                     |

| SHIP_MODE_DELAY  |         |         |         | 0x0E[2]               |                                                 |                     |

| V2X_VALID_INT    | 0x03[7] | 0x04[7] | 0x02[0] | 0x0D[0]               |                                                 |                     |

| CFLY_FLT         | 0x03[6] | 0x04[6] |         |                       |                                                 |                     |

| HVDD_FLT         | 0x03[5] | 0x04[5] |         |                       |                                                 |                     |

| SW_DIR_INT       | 0x03[4] | 0x04[4] | 0x02[4] |                       |                                                 |                     |

| V2X_OCP          | 0x03[1] | 0x04[1] |         | V2X_OCP2: 0x0B[7:4]   | V2X_OCP2: 0x0B[7:4]                             |                     |

| PWRON_INT        | 0x03[0] |         |         | -                     |                                                 |                     |

| RPUPD_EN         |         |         |         |                       | 0x05[7]                                         |                     |

| EN_HARD_RST      |         |         |         | -                     | 0x05[5]                                         |                     |

| EN_DEG           |         |         |         |                       |                                                 | 0x05[3:1]           |

| SCC_EN           |         |         |         |                       | 0x05[0]                                         |                     |

| PGOOD_DELAY      |         |         |         | 0x06[7]               |                                                 |                     |

| SFT_DISCHG_T     |         |         |         | 0x06[5:4]             |                                                 |                     |

| OOA_EN           |         |         |         |                       | 0x06[3]                                         |                     |

| V2X_AD_EN        |         | -       |         |                       | 0x06[2]                                         |                     |

| V1X_AD_EN        |         | -       |         |                       | 0x06[1]                                         |                     |

| V2X_PDN_EN       |         | -       |         |                       | 0x0A[5]                                         |                     |

| V1X_PDN_EN       |         | -       |         |                       | 0x0A[6]                                         |                     |

| VAC_PDN_EN       |         |         |         |                       | 0x0D[7]                                         |                     |

| FIX_FREQ         |         |         |         |                       | 0x06[0]                                         |                     |

| DTHR             |         |         |         | 0x07[5:4]             | 0x07[5:4]                                       |                     |

| FREQ             |         |         |         | 0x07[2:0]             |                                                 |                     |

| V2X_SW_F         |         |         |         | 0x08[1:0]             |                                                 | 0x09[6:5]           |

| V1X_SW_F         |         |         |         | 0x09[7]               |                                                 | 0x09[6:5]           |

## I<sup>2</sup>C REGISTERS ADDRESS MAP (continued)

| FUNCTION       | FLAG | MASK | STATUS  | THRESHOLD SETTING                              | ENABLE  | DEGLITCH |

|----------------|------|------|---------|------------------------------------------------|---------|----------|

| DEEP_SKIP      |      |      |         | 0x0E[5:4]                                      | -       |          |

| RESTART_EN     |      |      |         | -                                              | 0x0E[3] |          |

| WAIT_T         |      |      |         | 0x0E[1:0]                                      | -       |          |

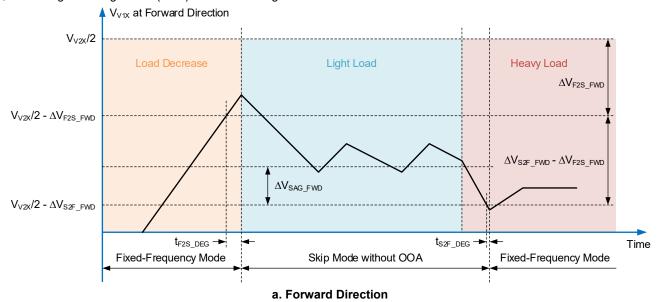

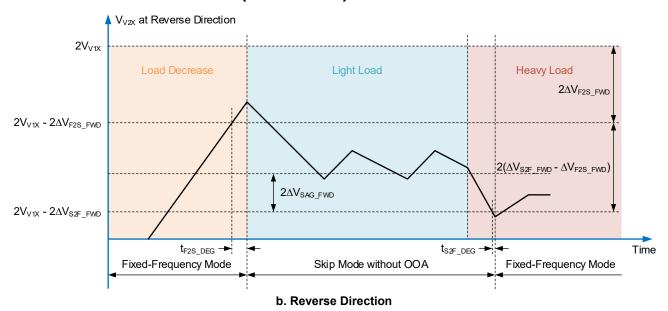

| F2S_DROP       |      |      |         | F2S_DROP: 0x0F[7:6]<br>F2S_FWD_OFFSET: 0x15[2] |         |          |

| S2F_DROP       |      |      |         | 0x0F[5:4]                                      | -       |          |

| SAG_FWD        |      | -    | -       | 0x0F[3:2]                                      | -       |          |

| LO_V2X_SW      |      | -    | 0x10[7] |                                                |         |          |

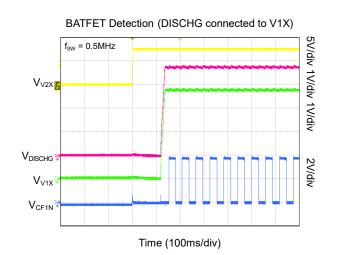

| BATFET_DET     |      |      |         |                                                | 0x11[7] |          |

| OTP_VER        |      |      |         | 0x13[7:4]                                      | -       |          |

| CHIP_VER       | 1    | ı    | -       | 0x13[3:0]                                      | ı       |          |

| DEVICE_ID      | 1    | -    |         | 0x14[7:0] (0x09)                               | -       |          |

| LO_V2X_SKIP_EN | -    | 1    |         | -                                              | 0x15[7] |          |

## **REGISTER AND DATA**

**REG0x00: INT\_SRC Register [reset = 0x00]**

| BITS | BIT NAME       | RESET | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                          | RESET BY |

|------|----------------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| D[7] | V2X_OVP_INT    | 0     | RC   | V2X_OVP Fault Flag Bit 0 = No V2X_OVP fault (default) 1 = V2X_OVP fault has occurred, or the V2X_OVP status bit is reset from '1' to '0' when the fault is cleared. Generates an interrupt on IRQB pin if unmasked. Read this bit to reset it to 0.                                                                                  | N/A      |

| D[6] | V1X_OVP_INT    | 0     | RC   | V1X_OVP Fault Flag Bit 0 = No V1X_OVP fault (default) 1 = V1X_OVP fault has occurred, or the V1X_OVP status bit is reset from '1' to '0' when the fault is cleared. Generates an interrupt on IRQB pin if unmasked. Read this bit to reset it to 0.                                                                                  | N/A      |

| D[5] | V1X_OC_ALM_INT | 0     | RC   | V1X Over-Current Alarm Flag Bit (including forward mode and reverse mode)  0 = No V1X over-current alarm (default)  1 = V1X over-current alarm has occurred, or the V1X_OCP_ALM status bit has been reset from '1' to '0' when the alarm is cleared. Generates an interrupt on IRQB pin if unmasked. Read this bit to reset it to 0. | N/A      |

| D[4] | V1X_OCP_INT    | 0     | RC   | V1X Over-Current Fault Flag Bit (including V1X_OCP1 and V1X_OCP2) 0 = No V1X over-current fault (default) 1 = V1X over-current fault has occurred. Generates an interrupt on IRQB pin if unmasked. Read this bit to reset it to 0.                                                                                                   | N/A      |

| D[3] | T_ALM1_INT     | 0     | RC   | T <sub>DIE</sub> Over 100°C Alarm Flag Bit 0 = No T <sub>DIE</sub> over 100°C alarm (default) 1 = T <sub>DIE</sub> over 100°C alarm has occurred, or the T_ALM1 status bit is reset from '1' to '0' when the alarm is cleared. Generates an interrupt on IRQB pin if unmasked. Read this bit to reset it to 0.                       | N/A      |

| D[2] | T_ALM2_INT     | 0     | RC   | T <sub>DIE</sub> Over 120°C Alarm Flag Bit 0 = No T <sub>DIE</sub> over 120°C alarm (default) 1 = T <sub>DIE</sub> over 120°C alarm has occurred, or the T_ALM2 status bit is reset from '1' to '0' when the alarm is cleared. Generates an interrupt on IRQB pin if unmasked. Read this bit to reset it to 0.                       | N/A      |

| D[1] | T_SHDN_INT     | 0     | RC   | $T_{\text{DIE}}$ Thermal Shutdown Fault Flag Bit 0 = No $T_{\text{DIE}}$ thermal shutdown fault (default) 1 = $T_{\text{DIE}}$ thermal shutdown fault has occurred, or the T_SHDN status bit is reset from '1' to '0' when the fault is cleared. Generates an interrupt on IRQB pin if unmasked. Read this bit to reset it to 0.     | N/A      |

| D[0] | FSS_FLT_INT    | 0     | RC   | Forward Mode Soft-Start Fault Flag Bit 0 = No soft-start fault (default) 1 = Forward mode soft-start fault has occurred. Generates an interrupt on IRQB pin if unmasked. Read this bit to reset it to 0.                                                                                                                             | N/A      |

REG0x01: INT\_SRC\_M Register [reset = 0x00]

| BITS | BIT NAME     | RESET | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                            | RESET BY                           |

|------|--------------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| D[7] | V2X_OVP_M    | 0     | R/W  | Mask Bit for the V2X_OVP Fault Interrupt 0 = V2X_OVP fault interrupt can work (default) 1 = Mask V2X_OVP fault interrupt. V2X_OVP_INT bit sets after the fault occurs or is cleared, but no interrupt signal is sent on IRQB pin.                                                                                      | Hard-reset or<br>REG_RST or<br>WDT |

| D[6] | V1X_OVP_M    | 0     | R/W  | Mask Bit for the V1X_OVP Fault Interrupt 0 = V1X_OVP fault interrupt can work (default) 1 = Mask V1X_OVP fault interrupt. V1X_OVP_INT bit sets after the fault occurs or is cleared, but no interrupt signal is sent on IRQB pin.                                                                                      | Hard-reset or<br>REG_RST or<br>WDT |

| D[5] | V1X_OC_ALM_M | 0     | R/W  | Mask Bit for the V1X Over-Current Alarm Interrupt 0 = V1X over-current alarm interrupt can work (default) 1 = Mask V1X over-current alarm interrupt. V1X_OC_ALM_INT bit sets after the alarm occurs or is cleared, but no interrupt signal is sent on IRQB pin.                                                        | Hard-reset or<br>REG_RST or<br>WDT |

| D[4] | V1X_OCP_M    | 0     | R/W  | Mask Bit for the V1X Over-Current Fault Interrupt 0 = V1X over-current fault interrupt can work (default) 1 = Mask V1X over-current fault interrupt. V1X_OCP_INT bit sets after the fault, but no interrupt signal is sent on IRQB pin.                                                                                | Hard-reset or<br>REG_RST or<br>WDT |

| D[3] | T_ALM1_M     | 0     | R/W  | Mask Bit for the $T_{\text{DIE}}$ Over 100°C Alarm Interrupt $0 = T_{\text{DIE}}$ over 100°C alarm interrupt can work (default) $1 = \text{Mask } T_{\text{DIE}}$ over 100°C alarm interrupt. $T_{\text{ALM1\_INT}}$ bit sets after the alarm occurs or is cleared, but no interrupt signal is sent on IRQB pin.       | Hard-reset or<br>REG_RST or<br>WDT |

| D[2] | T_ALM2_M     | 0     | R/W  | Mask Bit for the T <sub>DIE</sub> Over 120°C Alarm Interrupt 0 = T <sub>DIE</sub> over 120°C alarm interrupt can work (default) 1 = Mask T <sub>DIE</sub> over 120°C alarm interrupt. T_ALM2_INT bit sets after the alarm occurs or is cleared, but no interrupt signal is sent on IRQB pin.                           | Hard-reset or<br>REG_RST or<br>WDT |

| D[1] | T_SHDN_M     | 0     | R/W  | Mask Bit for the $T_{\text{DIE}}$ Thermal Shutdown Fault Interrupt $0 = T_{\text{DIE}}$ thermal shutdown fault interrupt can work (default) $1 = \text{Mask } T_{\text{DIE}}$ thermal shutdown fault interrupt. T_SHDN_INT bit sets after the fault occurs or is cleared, but no interrupt signal is sent on IRQB pin. | Hard-reset or<br>REG_RST or<br>WDT |

| D[0] | FSS_FLT_M    | 0     | R/W  | Mask Bit for the Forward Mode Soft-Start Fault Interrupt 0 = Soft-start fault interrupt can work (default) 1 = Mask forward mode soft-start fault interrupt. FSS_FLT_INT bit sets after the fault, but no interrupt signal is sent on IRQB pin.                                                                        | Hard-reset or<br>REG_RST or<br>WDT |

**REG0x02: STATUS Register [reset = 0x00]**

| BITS | BIT NAME   | RESET | TYPE | DESCRIPTION                                                                                                                                                                      | RESET BY |

|------|------------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| D[7] | V2X_OVP    | 0     | R    | V2X_OVP Fault Status Bit<br>0 = No V2X_OVP fault (default)<br>1 = Device is in V2X_OVP fault status.                                                                             | N/A      |

| D[6] | V1X_OVP    | 0     | R    | V1X_OVP Fault Status Bit<br>0 = No V1X_OVP fault (default)<br>1 = Device is in V1X_OVP fault status.                                                                             | N/A      |

| D[5] | V1X_OC_ALM | 0     | R    | Bidirectional V1X Over-Current Alarm Status Bit 0 = No V1X over-current alarm (default) 1 = Device is in V1X over-current alarm status.                                          | N/A      |

| D[4] | SW_DIR     | 0     | R    | SCC Switching Direction Status Bits 0 = Forward direction (default) 1 = Reverse direction                                                                                        | N/A      |

| D[3] | T_ALM1     | 0     | R    | T <sub>DIE</sub> Over 100°C Alarm Status Bit<br>0 = No T <sub>DIE</sub> over 100°C alarm (default)<br>1 = Device is in T <sub>DIE</sub> over 100°C alarm status.                 | N/A      |

| D[2] | T_ALM2     | 0     | R    | T <sub>DIE</sub> Over 120°C Alarm Status Bit<br>0 = No T <sub>DIE</sub> over 120°C alarm (default)<br>1 = Device is in T <sub>DIE</sub> over 120°C alarm status.                 | N/A      |

| D[1] | T_SHDN     | 0     | R    | $T_{\text{DIE}}$ Thermal Shutdown Fault Status Bit $0$ = No $T_{\text{DIE}}$ thermal shutdown fault (default) $1$ = Device is in $T_{\text{DIE}}$ thermal shutdown fault status. | N/A      |

| D[0] | V2X_VALID  | 0     | R    | $V_{V2X}$ above V2X <sub>VALID</sub> Threshold Status Bit $0 = V_{V2X} < V2X_{VALID}$ (default) $1 = V_{V2X} > V2X_{VALID}$ .                                                    | N/A      |

## REG0x03: INT\_SRC2 Register [reset = 0x00]

| BITS | BIT NAME      | RESET | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                          | RESET BY |

|------|---------------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| D[7] | V2X_VALID_INT | 0     | RC   | V2X_VALID Status Change Event Flag Bits 0 = No V2X_VALID status change event (default) 1 = V2X_VALID status change event has occurred. When the V2X_VALID status bit has changed, generates an interrupt on IRQB pin if unmasked. Read this bit to reset it to 0.                                    | N/A      |

| D[6] | CFLY_FLT_INT  | 0     | RC   | $C_{FLY}$ Charging Fault Flag Bit 0 = No $C_{FLY}$ charging fault (default) 1 = $C_{FLY}$ charging fault has occurred. Generates an interrupt on IRQB pin. Read this bit to reset it to 0.                                                                                                           | N/A      |

| D[5] | HVDD_FLT_INT  | 0     | RC   | HVDD Charging Fault Flag Bit 0 = No HVDD charging fault (default) 1 = HVDD charging fault has occurred. Generates an interrupt on IRQB pin. Read this bit to reset it to 0.                                                                                                                          | N/A      |

| D[4] | SW_DIR_INT    | 0     | RC   | SCC Switching Direction Transition Event Flag Bit 0 = No SCC switching direction transition event (default) 1 = SCC switching direction transition event has occurred. When the SW_DIR status bit is changed, generates an interrupt on IRQB pin if unmasked. Read this bit to reset it to 0.        | N/A      |

| D[3] | CONV_OCP_INT  | 0     | RC   | SCC Real-Time Converting Over-Current Event Flag Bit 0 = No SCC converting over-current event (default) 1 = SCC converting over-current event has occurred. When the CONV_OCP_INT status bit has changed, it generates an interrupt on IRQB pin if unmasked. Read this bit to reset it to 0.         | N/A      |

| D[2] | Reserved      | 0     | R    | Reserved                                                                                                                                                                                                                                                                                             | N/A      |

| D[1] | V2X_OCP_INT   | 0     | RC   | V2X Over-Current Fault Flag Bit (including V1X_OCP1 during reverse mode and V2X_OCP2) 0 = No V2X over-current fault (default) 1 = V2X over-current fault has occurred. Generates an interrupt on IRQB pin if unmasked. Read this bit to reset it to 0.                                               | N/A      |

| D[0] | PWRON_INT     | 0     | RC   | Device Power-on Event Flag Bit (1. V1X or V2X rising above its UVLO threshold and the chip is enabled; 2. VAC rising above its present threshold) 0 = No device power-on event (default) 1 = Device power-on event has occurred. Generates an interrupt on IRQB pin. Read this bit to reset it to 0. | N/A      |

REG0x04: INT\_SRC2\_M Register [reset = 0x00]

| BITS | BIT NAME       | RESET | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                         | RESET BY                           |

|------|----------------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| D[7] | V2X_VALID_M    | 0     | R/W  | Mask Bit for the V2X_VALID Status Change Event Interrupt 0 = V2X_VALID status change event interrupt can work (default) 1 = Mask V2X_VALID status change event interrupt. V2X_VALID_INT bit sets after the event occurs, but no interrupt signal is sent on IRQB pin.                               | Hard-reset<br>or REG_RST<br>or WDT |

| D[6] | CFLY_FLT_M     | 0     | R/W  | Mask Bit for the $C_{FLY}$ Charging Fault Interrupt $0 = C_{FLY}$ charging fault interrupt can work (default) $1 = Mask C_{FLY}$ charging fault interrupt. $CFLY_FLT_INT$ bit sets after the fault occurs, but no interrupt signal is sent on IRQB pin.                                             | Hard-reset<br>or REG_RST<br>or WDT |

| D[5] | HVDD_FLT_M     | 0     | R/W  | Mask Bit for the HVDD Charging Fault Interrupt 0 = HVDD charging fault interrupt can work (default) 1 = Mask HVDD charging fault interrupt. HVDD_FLT_INT bit sets after the fault occurs, but no interrupt signal is sent on IRQB pin.                                                              | Hard-reset<br>or REG_RST<br>or WDT |

| D[4] | SW_DIR_M       | 0     | R/W  | Mask Bit for the SCC Switching Direction Transition Event Interrupt 0 = SCC switching direction transition event interrupt can work (default) 1 = Mask SCC switching direction transition event interrupt. SW_DIR_INT bit sets after the event occurs, but no interrupt signal is sent on IRQB pin. | Hard-reset<br>or REG_RST<br>or WDT |

| D[3] | CONV_OCP_INT_M | 0     | R/W  | Mask Bit for the SCC Converting Over-Current Event Interrupt 0 = SCC converting over-current event interrupt can work (default). 1 = Mask SCC converting over-current event interrupt. CONV_OCP_INT bit sets after the event occurs, but no interrupt signal is sent on IRQB pin.                   | Hard-reset<br>or REG_RST<br>or WDT |

| D[2] | Reserved       | 0     | R    | Reserved                                                                                                                                                                                                                                                                                            | N/A                                |

| D[1] | V2X_OCP_M      | 0     | R/W  | Mask Bit for the V2X Over-Current Fault Interrupt 0 = V2X over-current fault interrupt can work (default) 1 = Mask V2X over-current fault interrupt. V2X_OCP_INT bit sets after the fault, but no interrupt signal is sent on IRQB pin.                                                             | Hard-reset<br>or REG_RST<br>or WDT |

| D[0] | Reserved       | 0     | R    | Reserved                                                                                                                                                                                                                                                                                            | N/A                                |

## REG0x05: EN\_CFG0 Register [reset = 0x80]

| BITS   | BIT NAME     | RESET | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                       | RESET BY                           |

|--------|--------------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| D[7]   | RPUPD_EN     | 1     | R/W  | Enable Bit of EN Pin Input Pull-Down Resistor Activation 0 = Disabled 1 = Enabled (default)                                                                                                                                                                                       | Hard-reset<br>or REG_RST<br>or WDT |

| D[6]   | REG_RST      | 0     | R/W  | Reset all the registers (this bit returns to 0 when the reset action is done) 0 = No Registers Reset (default) 1 = Reset Registers                                                                                                                                                | Hard-reset<br>or REG_RST<br>or WDT |

| D[5]   | EN_HARD_RST  | 0     | R/W  | Enable Bit of Hard Reset 0 = Disabled (default) 1 = Enabled If host performs the system reset, at the end of system reset period, all the registers will be reset to the default values.                                                                                          | Hard-reset<br>or REG_RST<br>or WDT |