## SGM31360 36-Channel LED Driver with Selectable PWM Frequency

## **GENERAL DESCRIPTION**

SGM31360 consists of 36 constant current channels each with independent PWM control, designed for driving LEDs. PWM frequency can be programmed to the corresponding value according to 8/10/12/16-bit PWM resolution setting and oscillator frequency setting via  $l^2C$  interface. The output current of each channel can be set to 20mA via a  $4k\Omega$  external resistor and an internal register. SGM31360 has a current limit function to avoid over-current, which is configured by register bit. The average LED current of each channel can be changed in maximum 65535 steps by changing the PWM duty cycle via an  $l^2C$  interface.

Pulling SDB low or using the software shutdown feature can turn off the SGM31360 to reduce power consumption.

SGM31360 is available in a Green TQFN-5×5-44L package. It operates from 2.7V to 5.5V over the temperature range of -40°C to +85°C.

## **APPLICATIONS**

Mobile Phones and Other Hand-Held Devices for LED Display LED in Home Appliances

## FEATURES

- 2.7V to 5.5V Supply

- I<sup>2</sup>C Interface, Automatic Address Increment Function

- Four Selectable I<sup>2</sup>C Addresses and a Broadcast Address

- SDB Reset I<sup>2</sup>C Module and Internal Reset Register

- ECO Mode for Auto Power Saving

- High Precision Current Sinking

- Device to Device Error: ±5%

- Channel to Channel Error: ±5%

- Adjustable PWM Frequency:

- 125kHz; 62.5kHz; 31kHz; 488Hz; 244Hz; 122Hz

@ 8-Bit PWM Resolution

- 31kHz; 15.6kHz; 7.8kHz; 122Hz

@ 10-Bit PWM Resolution

- 7.8kHz, 3.9kHz, 2kHz @ 12-Bit PWM Resolution

- 488Hz, 244Hz, 122Hz @ 16-Bit PWM Resolution

- 36-Channel RGB LED Driver

- 256-Level Global Current Configuration

- 256-Level Green/Red/Blue Light Current Setting

- 256-Level LED Module Current Setting

- Max 65535-Level Individual PWM Modulation

- EMI and Audible Noise Reduction

- Phase Shifting and Inverting Function

- Spread Spectrum Function

- PWM Scatter Method

- -40°C to +85°C Operating Temperature Range

- Available in a Green TQFN-5×5-44L Package

## **36-Channel LED Driver with Selectable PWM Frequency**

## **PACKAGE/ORDERING INFORMATION**

| MODEL    | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING          | PACKING<br>OPTION   |

|----------|------------------------|-----------------------------------|--------------------|-----------------------------|---------------------|

| SGM31360 | TQFN-5×5-44L           | -40°C to +85°C                    | SGM31360YTVO44G/TR | SGM31360<br>YTVO44<br>XXXXX | Tape and Reel, 3000 |

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

### XXXXX

Vendor Code

—— Trace Code

— Date Code - Year

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, V <sub>CC</sub>       | 0.3V to 6.0V                    |

|---------------------------------------|---------------------------------|

| Voltage at SCL, SDA, SDB, OUT1 to OU  | T36                             |

|                                       | -0.3V to V <sub>CC</sub> + 0.3V |

| Package Thermal Resistance            |                                 |

| TQFN-5×5-44L, θ <sub>JA</sub>         | 39.1°C/W                        |

| TQFN-5×5-44L, θ <sub>JB</sub>         | 20.1°C/W                        |

| TQFN-5×5-44L, θ <sub>JC (TOP)</sub>   | 23.9°C/W                        |

| TQFN-5×5-44L, θ <sub>JC (BOT)</sub>   | 5.9°C/W                         |

| Junction Temperature                  | +150°C                          |

| Storage Temperature Range             | 65°C to +150°C                  |

| Lead Temperature (Soldering, 10s)     | +260°C                          |

| ESD Susceptibility <sup>(1) (2)</sup> |                                 |

| НВМ                                   | ±4000V                          |

| CDM                                   | ±1000V                          |

|                                       |                                 |

#### NOTES:

1. For human body model (HBM), all pins comply with ANSI/ESDA/JEDEC JS-001 specifications.

2. For charged device model (CDM), all pins comply with ANSI/ESDA/JEDEC JS-002 specifications.

### **RECOMMENDED OPERATING CONDITIONS**

Operating Temperature Range .....-40°C to +85°C

### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

### DISCLAIMER

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

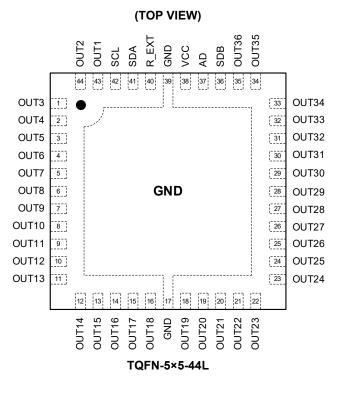

## **PIN CONFIGURATION**

## **PIN DESCRIPTION**

| PIN         | NAME          | FUNCTION                                                                                       |

|-------------|---------------|------------------------------------------------------------------------------------------------|

| 1 ~ 16      | OUT3 ~ OUT18  | Output Channel 3 ~ 18 for LEDs.                                                                |

| 17, 39      | GND           | Ground.                                                                                        |

| 18 ~ 35     | OUT19 ~ OUT36 | Output Channel 19 ~ 36 for LEDs.                                                               |

| 36          | SDB           | Shutdown the chip when pulled low.                                                             |

| 37          | AD            | I <sup>2</sup> C Address Setting.                                                              |

| 38          | VCC           | Power Supply.                                                                                  |

| 40          | R_EXT         | Input Terminal Used to Connect an External Resistor. This regulates the global output current. |

| 41          | SDA           | I <sup>2</sup> C Serial Data.                                                                  |

| 42          | SCL           | I <sup>2</sup> C Serial Clock.                                                                 |

| 43, 44      | OUT1, OUT2    | Output Channel 1, 2 for LEDs.                                                                  |

| Exposed Pad | GND           | Connect to GND.                                                                                |

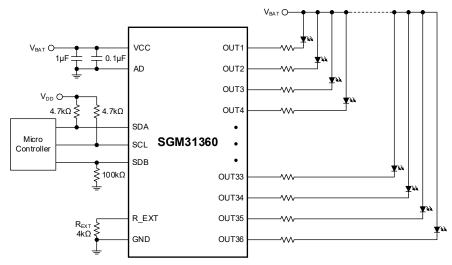

## **TYPICAL APPLICATION**

NOTE: 1. The maximum global output current is set to 20mA when  $R_{EXT} = 4k\Omega$ . Please see Page 9 for setting LED current.

Figure 1. Typical Application Circuit

## **ELECTRICAL CHARACTERISTICS**

(V<sub>CC</sub> = 3.6V,  $R_{EXT}$  = 4k $\Omega$ ,  $T_A$  = +25°C, unless otherwise noted.)

| PARAMETER                                | SYMBOL                       | CONDITIONS                                                                                                | MIN  | TYP  | MAX  | UNITS |

|------------------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Supply Voltage                           | Vcc                          |                                                                                                           | 2.7  |      | 5.5  | V     |

| VCC UVLO Falling Threshold               | $V_{\text{UVLO}\_\text{FL}}$ |                                                                                                           |      | 2.35 |      | V     |

| Maximum Sink Current per Channel         | I <sub>MAX</sub>             | V <sub>OUT</sub> = 0.8V, at 100% PWM and full DC Current                                                  |      | 20   |      | mA    |

| Sink Current Limit per Channel           | I <sub>LIM_L</sub>           | V <sub>REXT</sub> = 0V                                                                                    | 45   | 60   | 80   | mA    |

|                                          | I <sub>LIM_H</sub>           | V <sub>REXT</sub> = 0V                                                                                    | 70   | 95   | 120  | mA    |

| Headroom Voltage per Channel             | $V_{\text{HR}}$              | the voltage when the LED current drops 5%, at 100% PWM and full DC Current                                |      | 160  | 260  | mV    |

| Quiescent Current of VCC                 | Icc                          | $V_{\text{SDB}}$ = $V_{\text{CC}},$ enable CHIP_EN, at 100% PWM and full DC Current                       |      | 11.5 | 14   | mA    |

|                                          | ICC                          | $V_{\text{SDB}}$ = $V_{\text{CC}}$ enable CHIP_EN, at 100% PWM and no DC Current                          |      | 4    | 6    | mA    |

| Standby Current of VCC                   | I <sub>STB</sub>             | V <sub>SDB</sub> = V <sub>CC</sub> , enable CHIP_EN and ECO mode, all<br>output PWM registers = 0h > 32ms |      | 3    |      | μA    |

|                                          | 1516                         | $V_{SDB} = V_{CC}$ , disable CHIP_EN                                                                      |      | 1.6  | 3    | μA    |

| Shutdown Current of VCC                  | I <sub>SD</sub>              | V <sub>SDB</sub> = 0V                                                                                     |      | 0.1  | 1    | μA    |

| PWM Frequency of Output                  | f <sub>оит</sub>             | Set as 8-bit PWM, f <sub>OSC</sub> = 32MHz                                                                |      | 125  |      | kHz   |

|                                          |                              | Set as 8-bit PWM, f <sub>OSC</sub> = 31.25kHz                                                             |      | 122  |      | Hz    |

| Accuracy of PWM Frequency of Output      | f                            | Set as 8-bit PWM, f <sub>OSC</sub> = 32MHz                                                                | -5   |      | 5    | %     |

| Accuracy of FWM Frequency of Output      | f <sub>OUT_ACC</sub>         | Set as 8-bit PWM, f <sub>OSC</sub> = 31.25kHz                                                             | -5   |      | 5    | %     |

| Device to Device Current Error           | I <sub>ERR_DD</sub>          | 100% PWM and full DC Current                                                                              | -5   |      | 5    | %     |

| Channel to Channel Current Error         | I <sub>ERR_CC</sub>          | 100% PWM and full DC Current                                                                              | -5   |      | 5    | %     |

| Output Leakage Current                   | I <sub>oz</sub>              | $V_{OUT}$ = 5.5V, $V_{SDB}$ = 0V                                                                          |      | 0.1  | 1    | μA    |

| Thermal Shutdown                         | T <sub>SD</sub>              |                                                                                                           |      | 160  |      | °C    |

| Output Voltage of R_EXT Pin              | V <sub>EXT</sub>             |                                                                                                           | 0.38 | 0.4  | 0.42 | V     |

| Reference Current Ratio                  | K <sub>EXT</sub>             |                                                                                                           |      | 200  |      |       |

| Logic Electrical Characteristics (SDA, S | CL, SDB, A                   | AD)                                                                                                       |      |      |      |       |

| SDA, SCL, SDB, AD Logic Low Voltage      | V <sub>IL</sub>              | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$                                                           |      |      | 0.4  | V     |

| SDA, SCL, SDB, AD Logic High Voltage     | V <sub>IH</sub>              | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$                                                           | 1.0  |      |      | V     |

| Logic "0" Input Current                  | IIL                          | V <sub>INPUT</sub> = 0V                                                                                   |      | 5    |      | nA    |

| Logic "1" Input Current                  | l <sub>iH</sub>              | $V_{\text{INPUT}} = V_{\text{CC}}$                                                                        |      | 5    |      | nA    |

# I<sup>2</sup>C INTERFACE TIMING CHARACTERISTICS<sup>(1)</sup>

| DADAMETED                                          |                      | CONDITIONS | FAST N                      | IODE |     |

|----------------------------------------------------|----------------------|------------|-----------------------------|------|-----|

| PARAMETER                                          | SYMBOL               | CONDITIONS | MIN                         | MAX  |     |

| SCL Clock Frequency                                | f <sub>SCL</sub>     |            | 0                           | 400  | kHz |

| Hold Time (Repeated) START Condition               | t <sub>HD;STA</sub>  |            | 0.6                         |      | μs  |

| Low Period of the SCL Clock                        | t <sub>LOW</sub>     |            | 1.3                         |      | μs  |

| High Period of the SCL Clock                       | t <sub>HIGH</sub>    |            | 0.6                         |      | μs  |

| Setup Time for a Repeated START Condition          | t <sub>su;sta</sub>  |            | 0.6                         |      | μs  |

| Data Hold Time                                     | t <sub>HD;DATA</sub> |            | 0                           |      | μs  |

| Data Setup Time                                    | t <sub>SU;DATA</sub> |            | 100                         |      | ns  |

| Rise Time of Both SDA and SCL Signals              | t <sub>R</sub>       |            | 20                          | 300  | ns  |

| Fall Time of Both SDA and SCL Signals              | t <sub>F</sub>       |            | 20 × (V <sub>DD</sub> /5.5) | 300  | ns  |

| Setup Time for STOP Condition                      | t <sub>su;sto</sub>  |            | 0.6                         |      | μs  |

| Bus Free Time between a STOP and a START Condition | t <sub>BUF</sub>     |            | 1.3                         |      | μs  |

| Capacitive Load for Each Bus Line                  | C <sub>B</sub>       |            |                             | 400  | pF  |

| Data Valid Time                                    | t <sub>VD_DAT</sub>  |            |                             | 0.9  | μs  |

| Data Valid Acknowledge Time                        | $t_{VD\_ACK}$        |            |                             | 0.9  | μs  |

NOTE:

1. Industry standard I<sup>2</sup>C timing characteristics are according to I<sup>2</sup>C-Bus Specification.

## **36-Channel LED Driver with Selectable PWM Frequency**

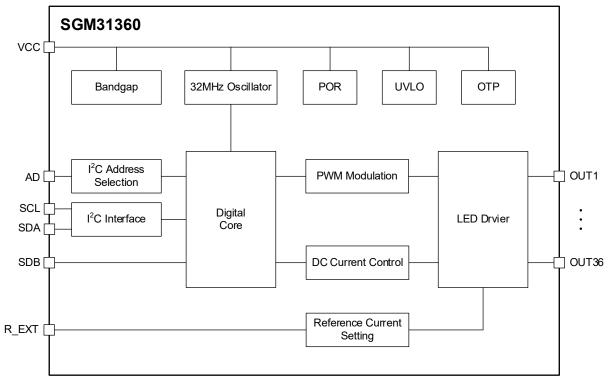

## FUNCTIONAL BLOCK DIAGRAM

Figure 2. Functional Block Diagram

## **DETAILED DESCRIPTION**

### **Operation Description**

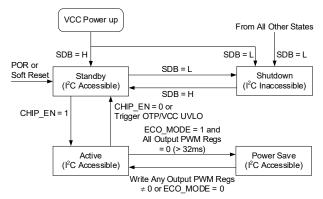

Figure 3. SGM31360 Operation State Diagram

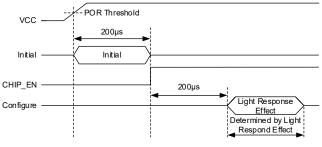

### **Power-On Reset**

Upon initial VCC power-up, SGM31360 is reset. All registers are reset to default values, and the LED driver is shut down. Once  $V_{CC}$  falls below the threshold voltage of POR (2V), SGM31360 will be reset again.

It is required to wait for at least 200 $\mu$ s before I<sup>2</sup>C write or read operation when V<sub>CC</sub> rises above the POR threshold and to wait for another 200 $\mu$ s before LED lighting effects are enabled.

Figure 4. Power-up Timing

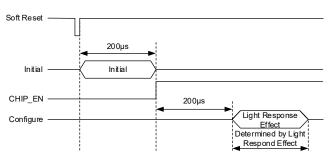

#### **Register Reset**

By writing 0x00 to REG0x5D reset register, the software reset is triggered. After software reset, all registers are reset to the default value and enter standby mode.

After the software reset command is acknowledged via  $I^2C$  bus, it is required to wait for at least 200µs before LED lighting effects are enabled.

Figure 5. Software Reset Timing

#### **Shutdown Mode**

SGM31360 enters shutdown mode automatically when SDB is pulled to low level. In this situation,  $l^2C$  interface is not accessible, and all registers cannot be configured and will be reset.

#### **Standby Mode**

SGM31360 enters standby mode when SDB is pulled from low to high, or CHIP\_EN bit is set from 1 to 0, or VCC under-voltage lockout or over-temperature protection occurs in active mode. Meanwhile, all registers will not be reset. In standby mode, all analog blocks are powered down. However, I<sup>2</sup>C interface is accessible, and all registers can be configured.

#### **Active Mode**

When SDB pin is high and CHIP\_EN bit is set to 1, SGM31360 enters the active mode.

### ECO Mode

When ECO\_MODE is set to 1, the auto ECO mode is enabled. If ECO\_MODE = 1 and the values of registers from REG0x01 to REG0x48 are 00H for longer than 32ms, the chip automatically enters ECO mode. Once writing a non-zero value into any register from REG0x01 to REG0x48, the device exits ECO mode and enters active mode immediately.

### **Over-Temperature Protection**

Over-temperature protection is only enabled in active mode. The SGM31360 will shut down all output channels when the temperature rises above +160°C.

### VCC Under-Voltage Lockdown Protection

UVLO protection operates in active mode. It prevents abnormal operation in case of VCC under voltage and will shut down the lighting effects. The UVLO falling threshold is 2.35V.

### **Current Configuration**

The average output current of each green/red/blue LED can be expressed as:

$$I_{OUTn} = K \times \frac{V_{REXT}}{R_{EXT}} \times \frac{I_{GLB}}{255} \times \frac{I_{COLz}}{255} \times \frac{I_{LEDy}}{255} \times \frac{PWMx}{256 \times 256}$$

(1)

#### where

K is the voltage ratio of 200;

$V_{REXT}$  is the reference voltage on  $R_{EXT}$  pin, 0.4V;

R<sub>EXT</sub> is the hardware resistor on R<sub>EXT</sub> pin;

I<sub>GLB</sub> is the 8-bit global current register;

I<sub>COLz</sub> is the 8-bit single color current register;

z is the number of the single color, from 1 to 3. For specific controlled output pins, please refer to the register description;

ILEDv is 8-bit LED module current register;

y is the number of the LED modules, from 1 to 12. For specific controlled output pins, please refer to the register description;

PWMx is 16-bit PWM register of each LEDs, consisting of the PWMx\_LSB and the PWMx\_MSB;

x is the number of the output pins, from 1 to 36.

The maximum output current for one green/red/blue LED is decided by  $R_{EXT}$ ,  $I_{GLB}$ ,  $I_{COLz}$ ,  $I_{LEDy}$ , and PWMx, which is 20mA at  $R_{EXT} = 4k\Omega$ . The recommended minimum value of  $R_{EXT}$  is  $2k\Omega$ . The current limit is set by ILIM bit, even if  $R_{EXT}$  is shorted.

### **PWM Modulation**

The PWM frequency is decided by three bits of oscillator frequency setting and two bits of PWM resolution setting. Table 1 shows the relationship of PWM frequency and related bits. To avoid the MLCC audible noise, it is recommended to use PWM frequency lower than 500Hz or higher than 20kHz.

If PWM is set to FFFFH, the output duty cycle is forced to full duty cycle (100%).

|                                      | PWM Frequency        |         |               |       |       |               |  |  |  |  |  |  |

|--------------------------------------|----------------------|---------|---------------|-------|-------|---------------|--|--|--|--|--|--|

| OSC_<br>FRQ[2:0]<br>PWM_<br>RES[1:0] | FRQ[2:0]<br>WM_ 000b |         | 010b/<br>011b | 100b  | 101b  | 110b/<br>111b |  |  |  |  |  |  |

| 00b: 8-Bit                           | 125kHz               | 62.5kHz | 31kHz         | 488Hz | 244Hz | 122Hz         |  |  |  |  |  |  |

| 01b: 10-Bit                          | 31kHz                | 15.6kHz | 7.8kHz        | 122Hz | Х     | Х             |  |  |  |  |  |  |

| 10b: 12-Bit                          | 7.8kHz               | 3.9kHz  | 2kHz          | Х     | Х     | Х             |  |  |  |  |  |  |

| 11b: 16-Bit                          | 488Hz                | 244Hz   | 122Hz         | Х     | Х     | Х             |  |  |  |  |  |  |

Table 1. PWM Frequency Setting

# NOTE: X is configured with 8-bit PWM resolution and 122Hz PWM frequency.

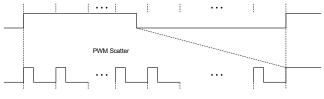

#### **Output PWM Scatter Method**

The PWM scatter function is controlled by REG0x5B[7], which can scatter the positive pulse width to negative pulse width (see Figure 6). The scatter function keeps the total energy of pulse width modulation, but increases the output frequency.

Figure 6. PWM Scatter Timing Diagram

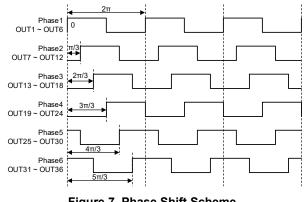

#### **Output PWM Phase Delay Method**

The PWM phase control is decided by REG0x5A register PHASE\_DELAY\_EN bit. The output is divided into six groups, OUT1 to OUT6, OUT7 to OUT12, OUT13 to OUT18, OUT19 to OUT24, OUT25 to OUT30 and OUT31 to OUT36. Each group has its own phase and these phases are shifted in sequence, so that the total current sink powering on the  $V_{LED}$  line can be averaged to each phase (see Figure 7). However, this method cannot ease the current sink in one phase.

Figure 7. Phase Shift Scheme

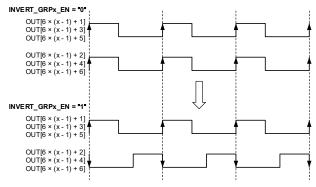

### **Output PWM Inverting Method**

The PWM inverting control is decided by REG0x5A[5:0] bits. The enable function also consists of six independent controls, followed by phase delay groups. By using PWM inverting method, the current ripple in one group can be reduced since each rising edge of the odd number PWM and the falling edge of the even number PWM are triggered simultaneously. (see Figure 8).

Figure 8. Phase Invert Scheme

### **Output PWM Spread Spectrum Function**

PWM is a troublesome for some application which takes EMI into consideration. This chip has spread spectrum function to optimize the EMI performance. If SPREAD\_EN bit (REG0x5B[4]) is set to "1", spead spectrum function is enabled. By setting SPREAD\_ RANGE[1:0] bits (REG0x5B[3:2]), four spread spectrum range of 4%/8%/16%/32% can be selected. The total electromagnetic emitting energy can spread into a wider range of frequency band which degrades the peak energy of EMI significantly. This function works on settings only when PWM frequency is larger than 7.8kHz.

### I<sup>2</sup>C Serial Interface and Data Communication

Standard I<sup>2</sup>C interface is used to program SGM31360 parameters and get status reports. I<sup>2</sup>C is well known 2-wire serial communication interface that can connect one (or more) master device(s) to some slave devices for two-way communication. The bus lines are named serial data (SDA) and serial clock (SCL). The device that initiates a data transfer is a master. A master generates the SCL signal. Slave devices have unique addresses to identify. A master is typically a micro controller or a digital signal processor.

The SGM31360 supports write and read operations, and it has four  $I^2C$  address options that depend on the connection of AD pin. See Table 2 for more detailed information.

#### Table 2. 7-Bit Slave Address

| AD Pin    | A[6:2] | A[1:0] | HEX | DEC |

|-----------|--------|--------|-----|-----|

| GND       | 01100  | 00     | 30H | 48D |

| VCC       |        | 01     | 31H | 49D |

| SDA       |        | 10     | 32H | 50D |

| SCL       |        | 11     | 33H | 51D |

| Broadcast | 0011   | 1100   | 1CH | 28D |

It has ninety four 8-bit registers, numbered from REG0x00 to REG0x5D.

#### Physical Layer

The standard  $I^2C$  interface of SGM31360 supports standard mode and fast mode communication speeds. The frequency of stand mode is up to 100kbits/s, while the fast mode is up to 400kbits/s. Bus lines are pulled high by weak current source or pull-up resistors and in logic high state with no clocking when the bus is free. The SDA pin is open-drain.

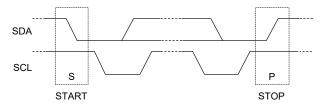

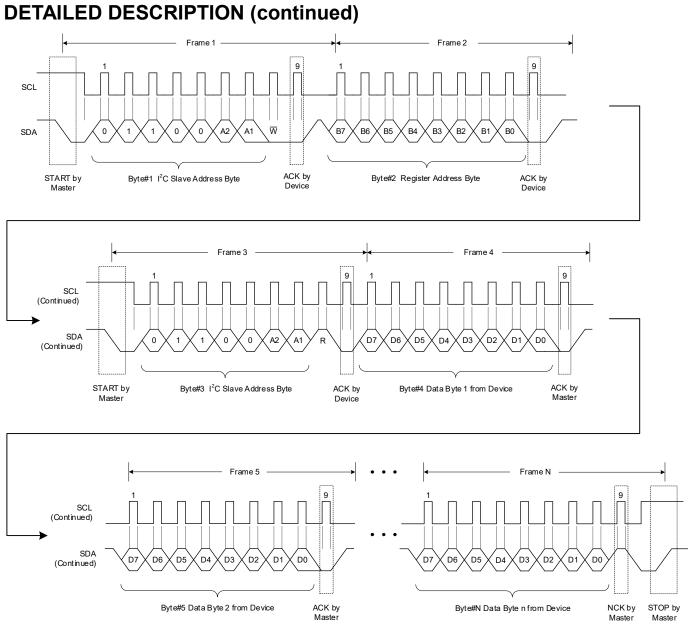

### I<sup>2</sup>C Data Communication START and STOP Conditions

A transaction is started by taking control of the bus by master if the bus is free. The transaction is terminated by releasing the bus when the data transfer job is done as shown in Figure 9. All transactions begin by master which applies a START condition on the bus lines to take over the bus and exchange data. At the end, the master terminates the transaction by applying one (or more) STOP condition. START condition is defined when SCL is high and a high to low transition on the SDA is generated by master. Similarly, a STOP is defined when SCL is high and SDA goes from low to high. START and STOP are always generated by a master. After a START and before a STOP the bus is considered busy.

Figure 9. I<sup>2</sup>C Bus in START and STOP Conditions

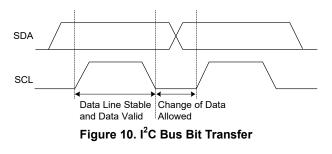

#### **Data Bit Transmission and Validity**

The data bit (high or low) must remain stable during clock high period. The state of SDA can only change when SCL is low. For each data bit transmission, one clock pulse is generated by master. Bit transfer in  $I^2C$  is shown in Figure 10.

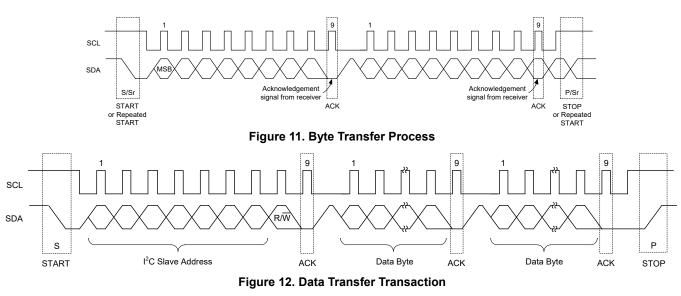

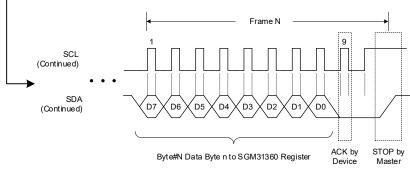

#### Byte Format

Data is transmitted in 8-bit packets (one byte at a time). The number of bytes in one transaction is not limited. In each packet, the 8 bits are sent successively with the Most Significant Bit (MSB) first. An acknowledge (or not-acknowledge) bit must come after the 8 data bits. This bit informs the transmitter whether the receiver is ready to proceed for the next byte or not. When the slave is ready for another byte of data, it releases the clock line and data transfer can continue with clocks generated by master. Figure 11 shows the byte transfer process with  $I^2C$  interface.

#### Acknowledge (ACK) and Not Acknowledge (NCK)

After transmission of each byte by transmitter, an acknowledge bit is replied by the receiver as the ninth bit. With the acknowledge bit, the receiver informs the transmitter that the byte is received, and another byte is expected or can be sent (ACK) or it is not expected (NCK = not ACK). Clock (SCL) is always generated by master, including the acknowledge clock pulse, no matter who is acting as transmitter or receiver. SDA line is released for receiver control during the acknowledge clock pulse. And the receiver can pull the SDA line low as ACK (reply a 0 bit) or let it be high as NCK during the SCL high pulse. After that, the master can either apply a STOP (P) condition to end the transaction or send a new START (S) condition to start a new transfer (called repeated start). For example, when master wants to read a register in slave, one start is needed to send the slave address and register address, and then, without a STOP condition, another start is sent by master to initiate the receiving transaction from slave. Master then sends the STOP condition and releases the bus.

#### **Data Direction Bit and Addressing Slaves**

The first byte sent by master after the START is always the target slave address (7 bits) and an eighth data-direction bit (R/W). R/W bit is 0 for a WRITE transaction and 1 for READ (when master is asking for data). Data direction is the same for all next bytes of the transaction. To reverse it, a new START or repeated START condition must be sent by master (STOP will end the transaction). Usually the second byte is a WRITE sending the register address that is supposed to be accessed in the next byte(s). The data transfer transaction is shown in Figure 12.

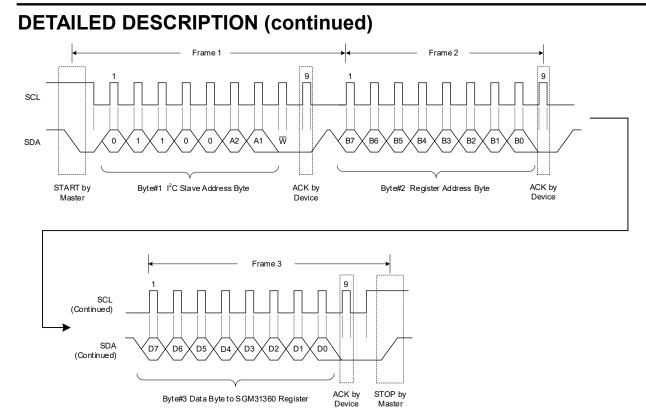

**WRITE:** If the master wants to write in the register, the third byte can be written directly as shown in Figure 13 for a single write data transfer. After receiving the ACK, master may issue a STOP condition to end the transaction or send the next register data, which will be written to the next address in a slave as multi-write. A STOP is needed after sending the last data.

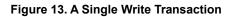

**READ**: If the master wants to read a single register (Figure 14), it sends a new START condition along with device address with  $R/\overline{W}$  bit = 1. After ACK is received, master reads the SDA line to receive the content of the register. Master replies with NCK to inform slave that no more data is needed (single read) or it can send an ACK to request for sending the next register content (multi-read). This can continue until an NCK is sent by master. A STOP must be sent by master in any case to end the transaction.

SG Micro Corp

## **36-Channel LED Driver with Selectable PWM Frequency**

Figure 14. A Single Read Transaction

#### Data Transactions with Multi-Read or Multi-Write

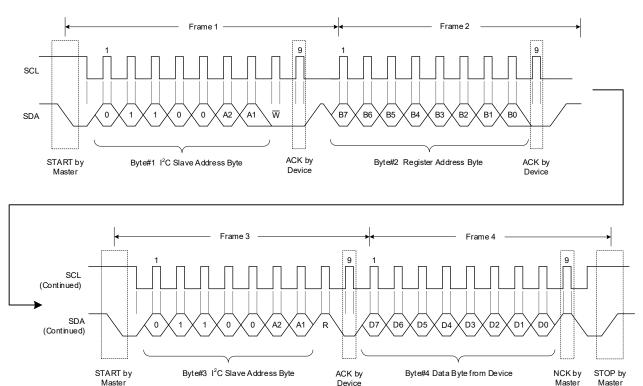

Multi-write is supported by SGM31360 for REG0x00 through REG0x5D registers, as explained in Figure 15 and Figure 16. In the multi-write, every new data byte sent by master is written to the next register of the device. A STOP is sent whenever master is done with writing into device registers.

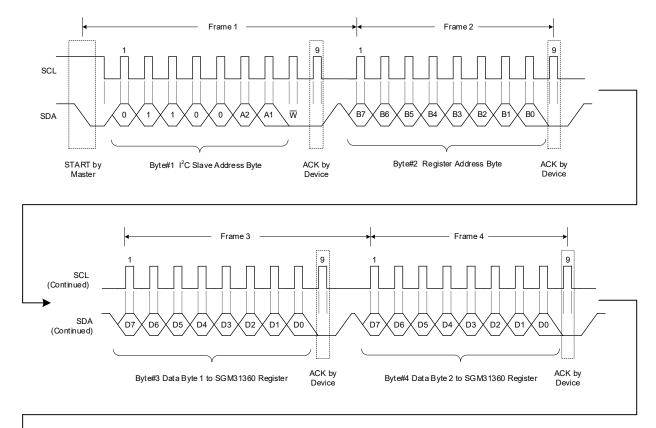

In a multi-read transaction, after receiving the first register data (its address is already written to the slave), the master replies with an ACK to ask the slave to send the next register data. This can continue as much as it is needed by master. Master sends back an NCK after the last received byte and issues a STOP condition.

Figure 15. A Multi-Write Transaction

## **36-Channel LED Driver with Selectable PWM Frequency**

Figure 16. A Multi-Read Transaction

## **REGISTER MAPS**

All registers are 8-bit and individual bits are named from D[0] (LSB) to D[7] (MSB). The device  $I^2C$  address depends on the connection of AD pin, as described in  $I^2C$  Serial Interface and Data Communication section.

## I<sup>2</sup>C Register Address Map

| FUNCTION                                      | STAT | FLAG | MASK | THRESHOLD<br>SETTING                                                         | ENABLE    | DEGLITCH |

|-----------------------------------------------|------|------|------|------------------------------------------------------------------------------|-----------|----------|

| DEVICE_ID                                     |      | -    | -    | 0x5C[7:0]                                                                    | -         | -        |

| Soft Reset                                    | -    | -    | -    | -                                                                            | 0x5D[7:0] | -        |

| CHIP Enable                                   | -    | -    | _    | -                                                                            | 0x00[0]   | _        |

| ECO Mode Enable                               | -    | -    | -    | -                                                                            | 0x00[7]   | -        |

| PWM Resolution Setting                        | -    | -    | -    | 0x00[2:1]                                                                    | _         | -        |

| Oscillator Frequency Setting                  | -    | -    | -    | 0x00[6:4]                                                                    | -         | -        |

| Output Current Limit Setting                  | -    | -    | -    | 0x00[3]                                                                      | _         | -        |

| Output Phase Shift                            | -    | -    | -    | -                                                                            | 0x5A[7]   | -        |

| Output Inverting                              | _    | -    | _    | -                                                                            | 0x5A[0:5] | -        |

| Output Scatter                                | -    | -    | -    | -                                                                            | 0x5B[7]   | -        |

| Output Frequency Spread<br>in Spectrum        | -    | _    | _    | 0x5B[3:2] &<br>0x5B[1:0]                                                     | 0x5B[4]   | _        |

| PWM_x Output Setting<br>(x = 1 to 36)         | -    | -    | -    | LSB: 0x01[7:0],<br>MSB: 0x02[7:0]<br>to<br>LSB: 0x47[7:0],<br>MSB: 0x48[7:0] | -         | -        |

| PWM Update                                    | -    | -    | -    | -                                                                            | 0x49[7:0] | _        |

| LED Module_y Current Setting<br>(y = 1 to 12) | -    | -    | -    | 0x4A[7:0]<br>to 0x55[7:0]                                                    | -         | -        |

| Color1 Current Setting                        | _    | -    | _    | 0x56[7:0]                                                                    | -         | -        |

| Color2 Current Setting                        | _    | _    | _    | 0x57[7:0]                                                                    | _         | -        |

| Color3 Current Setting                        | _    | _    | _    | 0x58[7:0]                                                                    | _         | -        |

| Global Current Setting                        | -    | _    | _    | 0x59[7:0]                                                                    | _         | _        |

## **REGISTER MAPS (continued)**

Bit Types: R: Read only R/W: Read/Write WCLR: Write clears the bit

### **REG0x00: Control Register [Reset = 0x00]**

| BITS   | BIT NAME     | DEFAULT | TYPE | DESCRIPTION                                                                                                                                                                                                                      | RESET BY   |

|--------|--------------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| D[7]   | ECO_MODE     | 0       | R/W  | ECO Mode<br>0 = Disable ECO mode. The chip will always work in<br>standby mode, even if no LED outputs. (default)<br>1 = Enable ECO mode. Then the chip enters ECO mode<br>when all output PWM registers set to zero after 32ms. | SOFT_RESET |

| D[6:4] | OSC_FRQ[2:0] | 000     | R/W  | Oscillator Frequency (f <sub>osc</sub> ) Setting<br>000 = 32MHz (default)<br>001 = 16MHz<br>010/011 = 8MHz<br>100 = 125kHz<br>101 = 62.5kHz<br>110/111 = 31.25kHz                                                                | SOFT_RESET |

| D[3]   | ILIM         | 0       | R/W  | Current Limit<br>0 = 60mA per channel (default)<br>1 = 95mA per channel                                                                                                                                                          | SOFT_RESET |

| D[2:1] | PWM_RES[1:0] | 00      | R/W  | PWM Resolution<br>00 = 8-bit (default)<br>01 = 10-bit<br>10 = 12-bit<br>11 = 16-bit                                                                                                                                              | SOFT_RESET |

| D[0]   | CHIP_EN      | 0       | R/W  | Chip Enable<br>0 = Disable chip (default)<br>1 = Enable chip                                                                                                                                                                     | SOFT_RESET |

### REG0x01 to REG0x48: Output1 ~ 36 PWM Register [Reset = 0x0000]

| BITS   | BIT NAME       | DEFAULT  | TYPE | DESCRIPTION                                                             | RESET BY   |

|--------|----------------|----------|------|-------------------------------------------------------------------------|------------|

| D[7:0] | PWMx_LSB[7:0]  | 00000000 |      | PWM LSB Value of OUT1-36 placed at REG0x01, REG0x03, REG0x05,, REG0x47. |            |

| D[7:0] | PWMx_MSB[15:8] | 0000000  | R/W  | PWM MSB Value of OUT1-36 placed at REG0x02, REG0x04, REG0x06,, REG0x48. | SOFT_RESET |

NOTE: x = 1 to 36.

### REG0x49: PWM Update Register [Reset = 0x00]

| BITS   | BIT NAME        | DEFAULT  | TYPE | DESCRIPTION                                                              | RESET BY   |

|--------|-----------------|----------|------|--------------------------------------------------------------------------|------------|

| D[7:0] | PWM_UPDATE[7:0] | 00000000 | WCLR | Write 00H to this register to update REG0x01-REG0x48 PWM data to output. | SOFT_RESET |

## **REGISTER MAPS (continued)**

### REG0x4A ~ REG0x55: LED Module1 ~ 12 Current Ratio Register [Reset = 0x00]

| BITS   | BIT NAME    | DEFAULT | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RESET BY   |

|--------|-------------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| D[7:0] | I_LEDy[7:0] | 0000000 | R/W  | DC Current Ratio Setting on Each RGB LED Modules. It will<br>control the current of OUT1, OUT2 and OUT3 for $y = 1$ ;<br>OUT4, OUT5 and OUT6 for $y = 2$ ;<br>OUT7, OUT8 and OUT9 for $y = 3$ ;<br>OUT10, OUT11 and OUT12 for $y = 4$ ;<br>OUT13, OUT14 and OUT15 for $y = 5$ ;<br>OUT16, OUT17 and OUT16 for $y = 6$ ;<br>OUT19, OUT20 and OUT21 for $y = 7$ ;<br>OUT22, OUT23 and OUT24 for $y = 8$ ;<br>OUT25, OUT26 and OUT27 for $y = 9$ ;<br>OUT28, OUT29 and OUT27 for $y = 10$ ;<br>OUT31, OUT32 and OUT33 for $y = 11$ ;<br>OUT34, OUT35 and OUT36 for $y = 12$ . | SOFT_RESET |

NOTE: y = 1 to 12.

### **REG0x56: Color1 DC Current Ratio Register [Reset = 0x00]**

| BITS   | BIT NAME    | DEFAULT  | TYPE | DESCRIPTION                                                                                                                                                                     | RESET BY   |

|--------|-------------|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| D[7:0] | I_COL1[7:0] | 00000000 | R/W  | DC Current Ratio Setting on One Single Color1. It will control the current of the OUT1, OUT4, OUT7, OUT10, OUT13, OUT16, OUT19, OUT22, OUT25, OUT28, OUT31, and OUT34 channels. | SOFT_RESET |

### REG0x57: Color2 DC Current Register [Reset = 0x00]

| BITS   | BIT NAME    | DEFAULT  | TYPE | DESCRIPTION                                                                                                                                                                     | RESET BY |

|--------|-------------|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| D[7:0] | I_COL2[7:0] | 00000000 |      | DC Current Ratio Setting on One Single Color2. It will control the current of the OUT2, OUT5, OUT8, OUT11, OUT14, OUT17, OUT20, OUT23, OUT26, OUT29, OUT32, and OUT35 channels. |          |

### **REG0x58: Color3 DC Current Register [Reset = 0x00]**

| BITS   | BIT NAME    | DEFAULT | TYPE | DESCRIPTION                                                                                                                                                                     | RESET BY   |

|--------|-------------|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| D[7:0] | I_COL3[7:0] | 0000000 | R/W  | DC Current Ratio Setting on One Single Color3. It will control the current of the OUT3, OUT6, OUT9, OUT12, OUT15, OUT18, OUT21, OUT24, OUT27, OUT30, OUT33, and OUT36 channels. | SOFT_RESET |

### REG0x59: Global Current Register [Reset = 0x00]

| BITS   | BIT NAME   | DEFAULT  | TYPE | DESCRIPTION                              | RESET BY   |

|--------|------------|----------|------|------------------------------------------|------------|

| D[7:0] | I_GLB[7:0] | 00000000 | R/W  | DC Current Ratio Setting on All Channels | SOFT_RESET |

## **REGISTER MAPS (continued)**

### REG0x5A: Inverting Group Enable Register [Reset = 0x00]

| BITS | BIT NAME       | DEFAULT | TYPE | DESCRIPTION                                                                                                                                                                                                                                                 | RESET BY   |

|------|----------------|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| D[7] | PHASE_DELAY_EN | 0       | R/W  | Phase Delay Function Enable<br>0 = Disable the phase delay function (default)<br>1 = Enable the phase delay function.<br>The phases of output channel groups from OUT1-6,<br>OUT7-12, OUT13-18, OUT19-24, OUT25-30 and<br>OUT31-36 are shifted in sequence. | SOFT_RESET |

| D[6] | Reserved       | 0       | R    | Reserved                                                                                                                                                                                                                                                    | N/A        |

| D[5] | INVERT_GRP6_EN | 0       | R/W  | Invert Group6 Function Enable<br>0 = Disable the Inverting function (default)<br>1 = Enable the Inverting function of OUT31 to OUT36                                                                                                                        | SOFT_RESET |

| D[4] | INVERT_GRP5_EN | 0       | R/W  | Invert Group5 Function Enable<br>0 = Disable the Inverting function (default)<br>1 = Enable the Inverting function of OUT25 to OUT30                                                                                                                        | SOFT_RESET |

| D[3] | INVERT_GRP4_EN | 0       | R/W  | Invert Group4 Function Enable<br>0 = Disable the Inverting function (default)<br>1 = Enable the Inverting function of OUT19 to OUT24                                                                                                                        | SOFT_RESET |

| D[2] | INVERT_GRP3_EN | 0       | R/W  | Invert Group3 Function Enable<br>0 = Disable the Inverting function (default)<br>1 = Enable the Inverting function of OUT13 to OUT18                                                                                                                        | SOFT_RESET |

| D[1] | INVERT_GRP2_EN | 0       | R/W  | Invert Group2 Function Enable<br>0 = Disable the Inverting function (default)<br>1 = Enable the Inverting function of OUT7 to OUT12                                                                                                                         | SOFT_RESET |

| D[0] | INVERT_GRP1_EN | 0       | R/W  | Invert Group1-6 Function Enable<br>0 = Disable the Inverting function (default)<br>1 = Enable the Inverting function of OUT1 to OUT6                                                                                                                        | SOFT_RESET |

### REG0x5B: Spread Spectrum Register [Reset = 0x00]

| BITS   | BIT NAME          | DEFAULT | TYPE | DESCRIPTION                                                                                                  | RESET BY   |

|--------|-------------------|---------|------|--------------------------------------------------------------------------------------------------------------|------------|

| D[7]   | SCATTER_EN        | 0       | R/W  | PWM Scatter Function Enable<br>0 = Disable PWM Scatter Function (default)<br>1 = Enable PWM Scatter Function | SOFT_RESET |

| D[6:5] | Reserved          | 00      | R    | Reserved                                                                                                     | N/A        |

| D[4]   | SPREAD_EN         | 0       | R/W  | Spread Spectrum Enable<br>0 = Disable (default)<br>1 = Enable                                                | SOFT_RESET |

| D[3:2] | SPREAD_RANGE[1:0] | 00      | R/W  | Spread Range Setting<br>$00 = \pm 4\%$ (default)<br>$01 = \pm 8\%$<br>$10 = \pm 16\%$<br>$11 = \pm 32\%$     | SOFT_RESET |

| D[1:0] | SPREAD_CYCLE[1:0] | 00      | R/W  | Spread Cycle Setting<br>00 = 2048µs (default)<br>01 = 1024µs<br>10 = 512µs<br>11 = 256µs                     | SOFT_RESET |

### REG0x5C: DEVICE\_ID Register [Reset = 0x30]

| BITS   | BIT NAME       | DEFAULT  | TYPE | DESCRIPTION                      | RESET BY |

|--------|----------------|----------|------|----------------------------------|----------|

| D[7:0] | DEVICE_ID[7:0] | 00110000 | R    | Device ID<br>00110000 = SGM31360 | N/A      |

### REG0x5D: Reset Register [Reset = 0x00]

| BITS   | BIT NAME        | DEFAULT  | TYPE | DESCRIPTION                      | RESET BY   |

|--------|-----------------|----------|------|----------------------------------|------------|

| D[7:0] | SOFT_RESET[7:0] | 00000000 | WCLR | Write 00H to reset all register. | SOFT_RESET |

Page

## **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Original (JUNE 2025) to REV.A

| Changed from product preview to production data | All |

|-------------------------------------------------|-----|

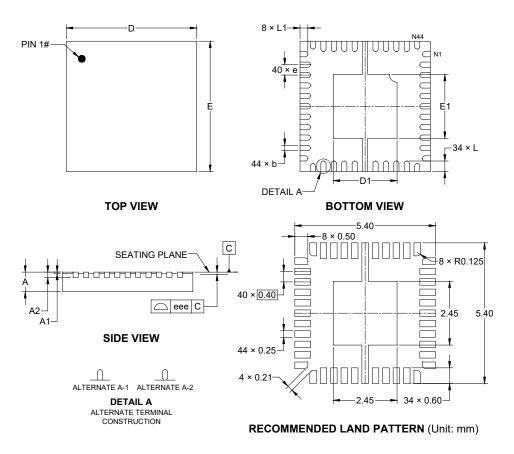

## PACKAGE OUTLINE DIMENSIONS TQFN-5×5-44L

| Symbol | Dir       | nensions In Millimet | ers   |  |  |  |  |  |

|--------|-----------|----------------------|-------|--|--|--|--|--|

| Symbol | MIN       | NOM                  | MAX   |  |  |  |  |  |

| A      | 0.700     | -                    | 0.800 |  |  |  |  |  |

| A1     | 0.000     | -                    | 0.050 |  |  |  |  |  |

| A2     | 0.200 REF |                      |       |  |  |  |  |  |

| b      | 0.150     | -                    | 0.250 |  |  |  |  |  |

| D      | 4.900     | -                    | 5.100 |  |  |  |  |  |

| E      | 4.900     | -                    | 5.100 |  |  |  |  |  |

| D1     | 2.350     | -                    | 2.550 |  |  |  |  |  |

| E1     | 2.350     | -                    | 2.550 |  |  |  |  |  |

| е      |           | 0.400 BSC            |       |  |  |  |  |  |

| L      | 0.300     | -                    | 0.500 |  |  |  |  |  |

| L1     | 0.200     | -                    | 0.400 |  |  |  |  |  |

| eee    |           | 0.080                |       |  |  |  |  |  |

NOTE: This drawing is subject to change without notice.

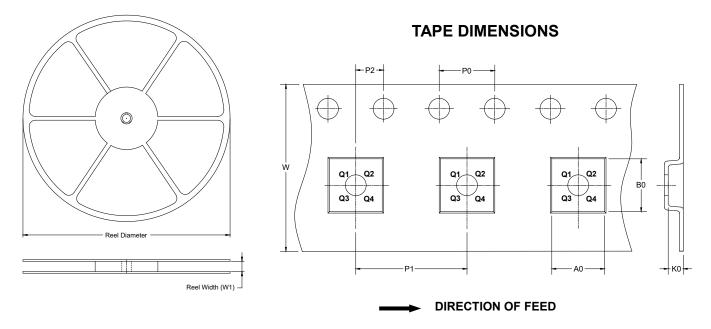

## TAPE AND REEL INFORMATION

### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

### KEY PARAMETER LIST OF TAPE AND REEL

| Package Type | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| TQFN-5×5-44L | 13"              | 12.4                     | 5.30       | 5.30       | 1.10       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

### **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

### **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |        |

|-----------|----------------|---------------|----------------|--------------|--------|

| 13″       | 386            | 280           | 370            | 5            | DD0002 |