## SGM41526A/SGM41527A 1.6MHz Synchronous Li-Ion and Li-Polymer Stand-Alone Battery Chargers with Automatic Power Path Selector

## FEATURES

- 4A Synchronous 1.6MHz PWM Charger

- Cycle-by-Cycle Current Limit

- Integrated 24V Switching MOSFETs

- Integrated Bootstrap Diode

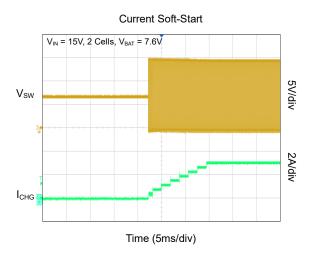

- Digital Soft-Start

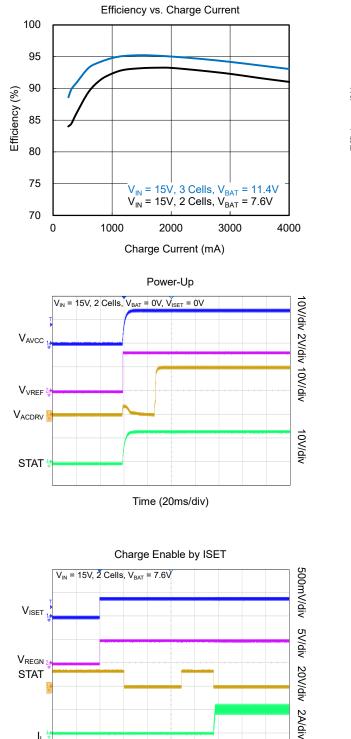

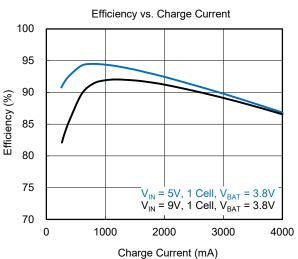

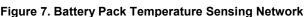

- Up to 95.2% Charge Efficiency

- 30V Absolute Maximum Input Voltage Rating with Adjustable Over-Voltage Threshold

- 4.5V to 22V Input Operating Voltage Range

- Automatic Power Path Selector (Battery/Adapter)

- Dynamic Power Management (DPM)

- Battery Charge Voltage

- + SGM41526A: Select 2-, 3-, or 4-Cell with 4.2V/Cell

- SGM41527A: Adjustable Charge Voltage

- 18µA Battery Current (No Adapter)

- 1.3mA Input Current (Charge Disabled)

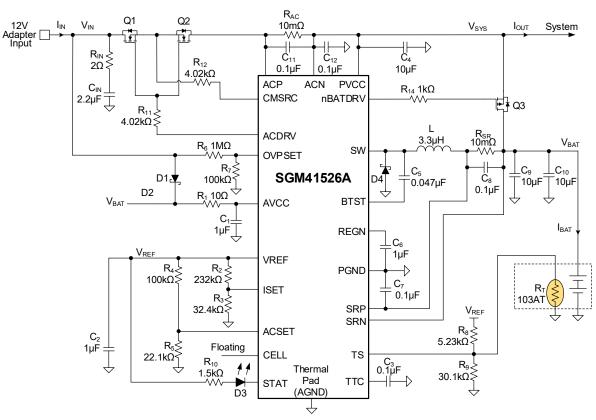

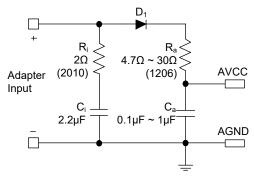

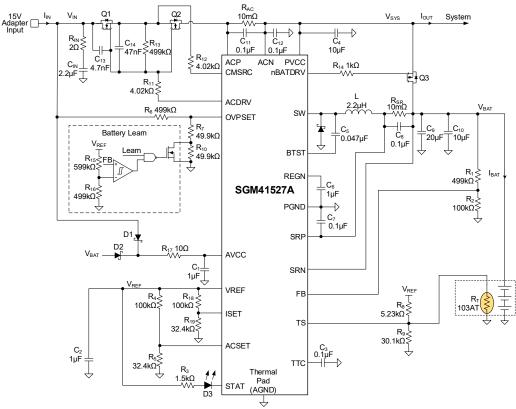

TYPICAL APPLICATION

- High Accuracy

- ±0.4% Charge Voltage Regulation

- ±5% Charge Current Regulation

- + ±4% Input Current Regulation

- Safety

- Thermal Regulation (Current Limit for T<sub>J</sub> = +120°C)

- Thermal Shutdown

- Battery Thermistor Sense Hot/Cold Charge Suspend

- Input Under-Voltage Lockout (UVLO)

- Input Over-Voltage (ACOV) Protection

## APPLICATIONS

Tablet PCs

Portable Terminals and Printers Portable Medical Equipment Battery Backup Systems

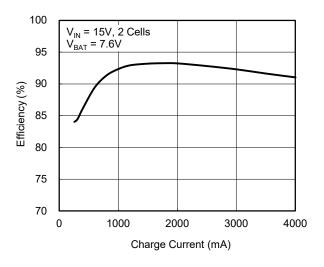

Figure 1. SGM41526A Typical Application Circuit (with a 2-Cell Battery)

## **GENERAL DESCRIPTION**

The SGM41526A and SGM41527A are stand-alone Li-Ion and Li-polymer battery chargers. The PWM switches are integrated inside and they can automatically select the power path. They also include gate drivers for external power path selector MOSFETs. The synchronous PWM controller runs at a fixed frequency (1.6MHz) and is capable of providing accurate regulation of charge voltage, charge current and input current. They are capable of providing continuous battery pack temperature monitoring in which the charge is only allowed when the temperature is within the desired range. The SGM41526A can charge 2-, 3- or 4-cell (selected by CELL pin); while the SGM41527A has an adjustable charge voltage for up to 4 cells. In the SGM41527A, the FB pin is used for charge voltage regulation (feedback) using an internal 2.1V reference and comparator.

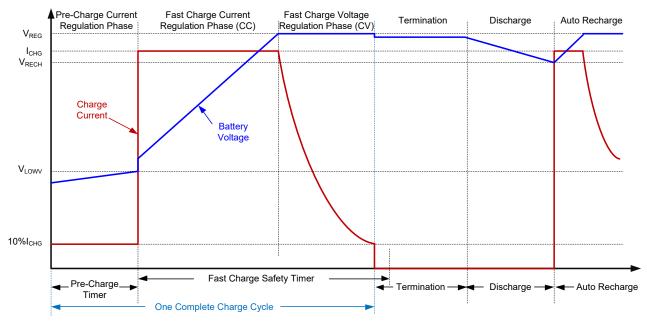

Typically, a full battery charging cycle has three consequent phases: pre-conditioning, constant current and constant voltage. The charge current is small during the pre-conditioning phase in which battery is heavily depleted. When the battery voltage exceeds a threshold voltage, the charge current increases to its maximum (fast charge current) until the battery voltage reaches its regulation level. Then the voltage is regulated and charge current drops. The starting phase is determined by the initial battery voltage. In constant voltage condition, the charge current drops automatically. When it decreases below 10% of the fast charge value, charging is terminated. A programmable safety charge timer is provided to prevent prolonged charging if it is not naturally terminated for any reason. When the battery voltage falls below recharge threshold, charge cycle is automatically started (or restarted).

If the input voltage falls below the battery voltage, the device enters sleep mode. In sleep mode, the quiescent current is very low. The SGM41526A and SGM41527A use dynamic power management (DPM) to prevent overload of the input source (AC adaptor). With DPM, the output charge current is reduced if the input power limit is reached. The input current is sensed and controlled by a precision current-sense amplifier to limit the input power.

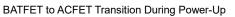

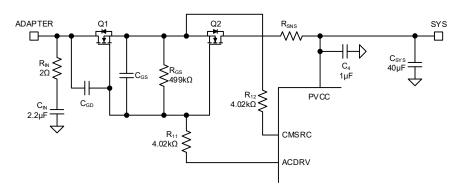

Gate driver outputs are provided for power path selection that can be achieved by three external switches. Two N-type back-to-back MOSFETs (Q1, Q2) are used as input pair (adapter power in and reverse blocking control) along with a P-type (Q3) that is used to control the battery connection to the system bus. The system is powered from adapter by Q1 and Q2 on if a qualified adapter is present. Otherwise, the system is connected to the battery by Q3. And with power path control, the battery cannot feed back to the input.

The SGM41526A and SGM41527A can charge the battery from a DC source with a voltage up to 22V. This range covers common adapter voltages and the car battery voltage. The qualified adapter range is adjustable by OVPSET pin. If the input voltage is out of the range, Q1 and Q2 will not be turned on.

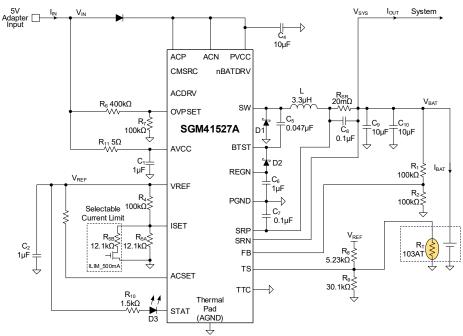

For 1-cell applications (only applicable to SGM41527A), when the battery is not removable, the design can be simplified by direct connection of the battery to the system. Therefore, when the input source is overloaded, the battery can help power the system automatically.

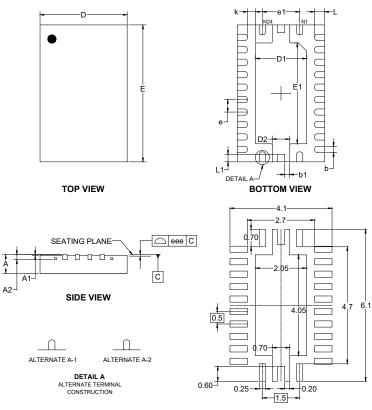

The SGM41526A and SGM41527A are available in a Green TQFN-5.5×3.5-24L package. It can operate over an ambient temperature range of -40 $^{\circ}$ C to +85 $^{\circ}$ C.

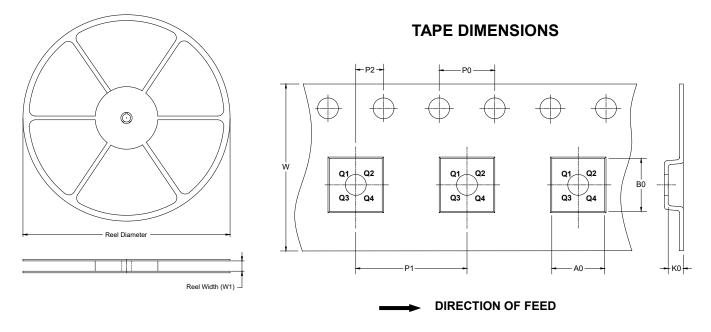

## **PACKAGE/ORDERING INFORMATION**

| MODEL     | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER  | PACKAGE<br>MARKING         | PACKING<br>OPTION   |

|-----------|------------------------|-----------------------------------|---------------------|----------------------------|---------------------|

| SGM41526A | TQFN-5.5×3.5-24L       | -40°C to +85°C                    | SGM41526AYTQQ24G/TR | SGM41526A<br>YTQQ<br>XXXXX | Tape and Reel, 3000 |

| SGM41527A | TQFN-5.5×3.5-24L       | -40°C to +85°C                    | SGM41527AYTQQ24G/TR | SGM41527A<br>YTQQ<br>XXXXX | Tape and Reel, 3000 |

### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

Vendor Code

- Trace Code

- Date Code Year

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

### **ABSOLUTE MAXIMUM RATINGS**

AGND Referenced Voltages

| PVCC                                  | 0.3V to 24V   |

|---------------------------------------|---------------|

| AVCC, ACP, ACN, ACDRV, CMSRC, STAT    | 0.3V to 30V   |

| BTST                                  | -0.3V to 30V  |

| nBATDRV, SRP, SRN                     | 0.3V to 24V   |

| SW                                    |               |

| FB (SGM41527A)                        | 0.3V to 24V   |

| CELL (SGM41526A), OVPSET, REGN, TS    | S, TTC        |

|                                       |               |

| VREF, ISET, ACSET                     |               |

| PGND                                  | -0.3V to 0.3V |

| Differential Voltages                 |               |

| SRP-SRN, ACP-ACN                      | 0.5V to 0.5V  |

| Package Thermal Resistance            |               |

| TQFN-5.5×3.5-24L, θ <sub>JA</sub>     |               |

| TQFN-5.5×3.5-24L, θ <sub>JB</sub>     | 6.9°C/W       |

| TQFN-5.5×3.5-24L, $\theta_{JC (TOP)}$ |               |

| TQFN-5.5×3.5-24L, $\theta_{JC (BOT)}$ | 2.3°C/W       |

| Junction Temperature                  |               |

| Storage Temperature Range             |               |

| Lead Temperature (Soldering, 10s)     | +260°C        |

| ESD Susceptibility                    |               |

| HBM                                   | 2000V         |

| CDM                                   | 1000V         |

### **RECOMMENDED OPERATING CONDITIONS**

| Input Voltage Range, V <sub>IN</sub>                               | 4.5V to 22V   |

|--------------------------------------------------------------------|---------------|

| Output Voltage, V <sub>BAT</sub>                                   | 18V (MAX)     |

| Output Current Range ( $R_{SR}$ = 10m $\Omega$ ), I <sub>OUT</sub> | 0.6A to 4A    |

| Maximum Differential Voltage                                       |               |

| SRP-SRN, ACP-ACN2                                                  | 00mV to 200mV |

| Operating Temperature Range                                        | 40°C to +85°C |

### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

### DISCLAIMER

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

SGM41526A SGM41527A

## 1.6MHz Synchronous Li-Ion/Li-Polymer Stand-Alone Battery Chargers with Automatic Power Path Selector

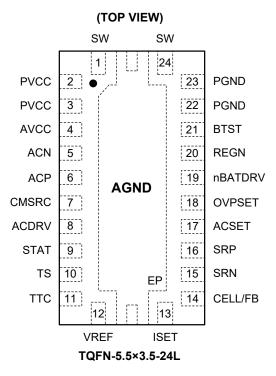

## **PIN CONFIGURATION**

## **PIN DESCRIPTION**

| PIN   | NAME  | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 24 | SW    | Р    | Switching Node. Connect SW pin to the output inductor and also to a bootstrap capacitor from BTST pin.                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2, 3  | PVCC  | Р    | Charger Input Voltage. Decouple with at least $10\mu$ F ceramic capacitor from PVCC pin to PGND as close to IC as possible.                                                                                                                                                                                                                                                                                                                                                                                |

| 4     | AVCC  | Р    | IC Supply Power. Place an RC filter $(10\Omega-1\mu F)$ with ceramic capacitor from input power to AVCC pin to AGND and place capacitor close to the IC. For 5V input, a minimum 5 $\Omega$ resistor is recommended. The device under-voltage lockout (UVLO) is sensed on AVCC pin (typically 3.3V rising with 0.21V hysteresis).                                                                                                                                                                          |

| 5     | ACN   | I    | Input Current Sense Resistor Negative Input. Connect a 100nF ceramic capacitor from ACN to ACP for differential-mode filtering. Connect a 100nF ceramic capacitor from ACN to AGND for common-mode filtering.                                                                                                                                                                                                                                                                                              |

| 6     | ACP   | I/P  | Input Current Sense Resistor Positive Input. Connect a 100nF ceramic capacitor from ACN to ACP for differential-mode filtering. Connect an optional 100nF ceramic capacitor from ACP to AGND for common-mode filtering.                                                                                                                                                                                                                                                                                    |

| 7     | CMSRC | 0    | Common Source of the ACFET and RBFET. Connect with a $4.02k\Omega$ resistor to the common source of the input MOSFET ACFET (Q1) and RBFET (Q2) to control the turn-on speed and limit inrush current. An external minimum 500k $\Omega$ resistor between ACDRV pin and CMSRC pin is essential.                                                                                                                                                                                                             |

| 8     | ACDRV | 0    | Gate Driver Output for Input Switches. A $4.02k\Omega$ resistor is placed to the common gate of the external N-channel ACFET and RBFET power MOSFETs. Connect both FETs as common source. It has break-before-make logic with respect to the nBATDRV and acts asymmetrical, allowing quick turn-off and slow turn-on.                                                                                                                                                                                      |

| 9     | STAT  | 0    | Open-Drain Charge Status Output Pin with 10kΩ External Pull-Up to the Power Rail. It can be connected to LED to show the charging status or it can directly communicate with the host. The STAT pin acts as follows:<br>During charge: low (LED ON).<br>Charge completed, charger in sleep mode or charge disabled: high (LED OFF).<br>Charge suspend (in response to a fault): 1Hz, including battery detection, charge suspend, input over-voltage, battery over-voltage, and timer fault. (LED BLINKS). |

## **PIN DESCRIPTION (continued)**

| PIN    | NAME                | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------|---------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

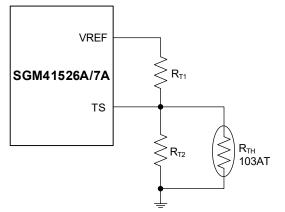

| 10     | TS                  | I    | Temperature Sense Voltage Input. Connect to a negative temperature coefficient (NTC) thermistor that can sense the battery temperature. The actual hot and cold temperature can be set by a resistor divider from VREF to TS to AGND. It is recommended to use a 103AT type thermistor for battery pack temperature sensing.                                                                                                                                                                                                                                                                                  |

| 11     | ттс                 | I    | Safety Timer (Fast Charge) and Termination Control. Pre-charge timer is fixed inside the device (30min typically). Fast charge safety timer is determined by the capacitor from this pin to AGND (5.6min/nF). Safety timer is disabled by pulling this pin low or high, but charge termination is disabled only when it is pulled low. The safety timer can be reset by charge termination (charge termination, charge disabled, input over-voltage protection, battery over-voltage protection, charge suspend, battery absent, etc.).                                                                       |

| 12     | VREF                | Ρ    | 3.3V Voltage Reference Output Internally Powered from AVCC Pin. Connect a 1µF ceramic capacitor to AGND as close to IC as possible. It is usually connected to the resistor divider of ISET, ACSET and TS pins. It can also be connected to STAT and CELL pins as pull-up rail.                                                                                                                                                                                                                                                                                                                               |

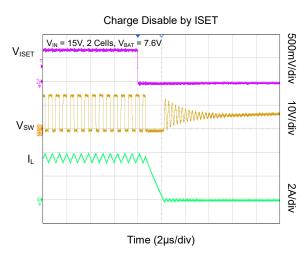

| 13     | ISET                | I    | Program Pin for Charge Current Settings. The voltage on this pin and the charge shunt resistor $R_{SR}$ determine the fast charge current. $V_{ISET}$ voltage can be set by a resistor divider (VREF-ISET-AGND).<br>$I_{CHG} = \frac{V_{ISET}}{20 \times R_{SR}}$ The pre-charge and termination currents are equal and determined by $I_{CHG}$ as a ratio of 10%.<br>The charger disables when ISET voltage is pulled below 30mV and enables if it exceeds 120mV.                                                                                                                                            |

|        | CELL<br>(SGM41526A) |      | Cell Selection Pin for SGM41526A. Set it low for 4-cell battery, floating for 2-cell, and set it high for 3-cell battery. Cell voltage regulation is fixed at 4.2V per cell.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 14     | FB<br>(SGM41527A)   | I    | Feedback Pin for Regulating the Charge Voltage in SGM41527A in the Constant-Voltage Mode. A resistor divider from battery terminal ( $V_{BAT}$ ) to FB ( $V_{FB}$ ) to AGND sets the charge voltage. And the internal voltage reference is 2.1V.                                                                                                                                                                                                                                                                                                                                                              |

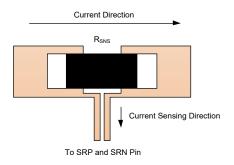

| 15     | SRN                 | I    | Charge Current Sense Resistor, Negative Input. A shunt resistor is connected between SRN pin and SRP pin to sense charge current. Connect a 100nF ceramic capacitor between SRN pin and SRP pin for differential-mode filtering. Connect an optional 100nF capacitor between SRN and AGND for common-mode filtering.                                                                                                                                                                                                                                                                                          |

| 16     | SRP                 | I/P  | Charge Current Sense Resistor, Positive Input. Connect a 100nF ceramic capacitor between SRN pin and SRP pin for differential-mode filtering. Connect another 100nF ceramic capacitor between SRP pin and AGND for common-mode filtering.                                                                                                                                                                                                                                                                                                                                                                     |

| 17     | ACSET               | I    | Program Pin to Set Input Current Limit for Dynamic Power Management. A voltage divider from VREF to ACSET to AGND can be used to set this parameter along with the input shunt resistor $R_{AC}$ :<br>$I_{DPM} = \frac{V_{ACSET}}{20 \times R_{AC}}$                                                                                                                                                                                                                                                                                                                                                          |

| 18     | OVPSET              | I    | Program Pin for Input Over-Voltage Detection. The input voltage can be sensed by a resistor voltage divider from input to OVPSET to AGND so that the ACOV and ACUV can be realized by setting proper resistor. An input over-voltage (ACOV) is detected if OVPSET voltage exceeds the internal 1.6V reference. A voltage below 0.494V indicates an input under-voltage (ACUV). If either of the two cases happens, both of the ACFET and RBFET will be turned off. If it is in charging process, the charge will terminate. Then the LED that is connected to STAT pin will blink at 1Hz to indicate a fault. |

| 19     | nBATDRV             | 0    | Gate Driver Output for External P-Type Power MOSFET (Battery Discharge Path). Use a $1k\Omega$ resistor to connect this pin to the gate of the BATFET (Q3) to control the turn-on speed. The source of the BATFET connects to the system and the drain connects to the battery positive terminal. In order to decrease inrush current, the internal gate driver is designed with quick turn-off and slow turn-on functions.<br>This gate driver has break-before-make logic with respect to the ACDRV gate driver (input switch).                                                                             |

| 20     | REGN                | Ρ    | 5V Internal Supply for the PWM Low-side Switch Driver. Decouple with a 1µF ceramic capacitor from REGN pin to PGND pin close to the IC. Anode of integrated bootstrap diode is connected to this pin.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 21     | BTST                | Р    | High-side Power MOSFET Driver Power Supply. Connect a 47nF bootstrap capacitor from SW to BTST.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

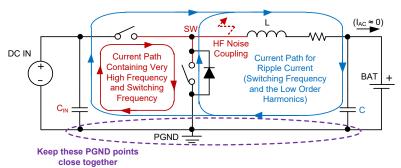

| 22, 23 | PGND                | Р    | Device Power Ground. On the PCB layout, connect this pin directly to ground points of the input and output capacitors of the charger. PGND connects to AGND only through in one point on thermal pad under the IC.                                                                                                                                                                                                                                                                                                                                                                                            |

| EP     | AGND                | Р    | Exposed Pad Beneath the IC. Always solder thermal pad to the board. Use vias to transfer heat to the back side and other layers of PCB. Thermal pad acts as AGND and only connects to PGND at one single point.                                                                                                                                                                                                                                                                                                                                                                                               |

NOTE:

<sup>1.</sup> I = Input, O = Output, P = Power.

## **ELECTRICAL CHARACTERISTICS**

| PARAMETER                                                                    | PARAMETER SYMBOL CONDITIONS   |                                                                                                                            | MIN  | TYP               | MAX   | UNITS |

|------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------|------|-------------------|-------|-------|

| Operating Conditions                                                         |                               |                                                                                                                            |      |                   |       |       |

| AVCC Input Voltage Operating Range during Charging                           | $V_{\text{AVCC\_OP}}$         |                                                                                                                            | 4.5  |                   | 22    | V     |

| Quiescent Currents                                                           |                               |                                                                                                                            |      |                   |       |       |

|                                                                              |                               | $V_{AVCC} > V_{UVLO}, V_{SRN} > V_{AVCC}$ (Sleep),<br>T <sub>J</sub> = 0°C to +85°C                                        |      | 7.4               | 15    |       |

| Battery Discharge Current<br>(Sum of Currents into AVCC, PVCC,<br>ACP, ACN)  | I <sub>BAT</sub>              | BTST, SW, SRP, SRN, $V_{AVCC} > V_{UVLO}$ , $V_{AVCC} > V_{SRN}$ , $V_{ISET} < 30mV$ , $V_{BAT} = 12.6V$ , charge disabled |      | 18                | 30 µA |       |

| ,                                                                            |                               | BTST, SW, SRP, SRN, $V_{AVCC} > V_{UVLO}$ , $V_{AVCC} > V_{SRN}$ , $V_{ISET} > 120mV$ , $V_{BAT} = 12.6V$ , charge done    |      | 18                | 30    |       |

|                                                                              |                               | $V_{AVCC} > V_{UVLO}, V_{AVCC} > V_{SRN}, V_{ISET} < 30mV, V_{BAT} = 12.6V, charge disabled$                               |      | 1.3               | 2.0   |       |

| Adapter Supply Current<br>(Sum of Currents into AVCC, ACP, ACN)              | I <sub>AC</sub>               | $V_{AVCC} > V_{UVLO}$ , $V_{AVCC} > V_{SRN}$ , $V_{ISET} > 120mV$ , charge enabled, no switching                           |      | 1.4               | 2.0   | mA    |

|                                                                              |                               | $V_{AVCC} > V_{UVLO}$ , $V_{AVCC} > V_{SRN}$ , $V_{ISET} > 120mV$ , charge enabled, switching                              |      | 15 <sup>(1)</sup> |       |       |

| Charge Voltage Regulation                                                    |                               |                                                                                                                            |      |                   |       |       |

|                                                                              |                               | CELL floating, 2-cell, measured on SRN                                                                                     |      | 8.4               |       |       |

| SRN Regulation Voltage (SGM41526A)                                           | $V_{BAT\_REG}$                | CELL to VREF, 3-cell, measured on SRN                                                                                      |      | 12.6              | V     |       |

|                                                                              |                               | CELL to AGND, 4-cell, measured on SRN                                                                                      |      | 16.8              |       |       |

| SRN Regulation Voltage (SGM41527A)                                           | $V_{\text{FB}\_\text{REG}}$   | Measure on FB                                                                                                              |      | 2.1               |       | V     |

| Charge Voltage Regulation Initial Accuracy                                   |                               |                                                                                                                            | -0.4 |                   | 0.4   | %     |

| Current Regulation - Fast Charge                                             |                               |                                                                                                                            |      |                   |       |       |

| ISET Voltage Range                                                           | VISET                         | R <sub>SENSE</sub> = 10mΩ                                                                                                  | 0.12 |                   | 0.8   | V     |

| Charge Current Set Factor (Amps of<br>Charge Current per Volt on ISET Pin)   | K <sub>ISET</sub>             | R <sub>SENSE</sub> = 10mΩ                                                                                                  |      | 5                 |       | A/V   |

|                                                                              |                               | V <sub>SRP-SRN</sub> = 40mV                                                                                                | 39.0 | 41.0              | 43.1  |       |

| Charge Current Regulation Initial Accuracy (with Schottky Diode on SW)       |                               | V <sub>SRP-SRN</sub> = 20mV                                                                                                | 19.1 |                   | 22.4  | mV    |

|                                                                              |                               | V <sub>SRP-SRN</sub> = 5mV                                                                                                 | 3.8  | 5.4               | 7.1   |       |

| Charge Disable Threshold                                                     | $V_{\text{ISET}\_\text{CD}}$  | V <sub>ISET</sub> falling                                                                                                  | 30   | 50                |       | mV    |

| Charge Enable Threshold                                                      | $V_{\text{ISET}_{\text{CE}}}$ | V <sub>ISET</sub> rising                                                                                                   |      | 100               | 120   | mV    |

| Leakage Current into ISET                                                    | I <sub>ISET</sub>             | V <sub>ISET</sub> = 2V                                                                                                     |      |                   | 100   | nA    |

| Input Current Regulation                                                     |                               |                                                                                                                            |      | -                 |       | -     |

| Input DPM Current Set Factor (Amps of<br>Input Current per Voltage on ACSET) | K <sub>DPM</sub>              | R <sub>SENSE</sub> = 10mΩ                                                                                                  |      | 5                 |       | A/V   |

|                                                                              |                               | V <sub>ACP-ACN</sub> = 80mV                                                                                                | 78.3 | 81.6              | 84.8  |       |

| Innut DDM Current Do and sting built is                                      |                               | V <sub>ACP-ACN</sub> = 40mV                                                                                                | 37.3 | 41.0              | 44.7  |       |

| Input DPM Current Regulation Initial<br>Accuracy (with Schottky Diode on SW) |                               | V <sub>ACP-ACN</sub> = 20mV                                                                                                | 17.6 | 20.7              | 23.8  | mV    |

| - · · · · · ·                                                                |                               | V <sub>ACP-ACN</sub> = 5mV                                                                                                 | 4.2  | 5.5               | 6.9   |       |

|                                                                              |                               | V <sub>ACP-ACN</sub> = 2.5mV                                                                                               | 1.5  | 3.0               | 4.5   |       |

| Leakage Current into ACSET Pin                                               | IACSET                        | V <sub>ACSET</sub> = 2V                                                                                                    |      |                   | 100   | nA    |

| PARAMETER                                                               | SYMBOL                          | CC                                           | NDITIONS                             | MIN  | TYP    | MAX  | UNITS |  |

|-------------------------------------------------------------------------|---------------------------------|----------------------------------------------|--------------------------------------|------|--------|------|-------|--|

| Current Regulation - Pre-Charge                                         |                                 |                                              |                                      |      |        |      |       |  |

| Pre-Charge Current Set Factor                                           | KIPRECHG                        | Percentage of fas                            | t charge current                     |      | 10 (2) |      | %     |  |

|                                                                         |                                 | $V_{SRP-SRN} = 4mV$                          |                                      | 3.4  | 4.6    | 5.7  | .,    |  |

| Pre-Charge Current Regulation Initial Accuracy                          |                                 | V <sub>SRP-SRN</sub> = 2mV                   |                                      | 1.3  | 2.5    | 3.8  | mV    |  |

| Charge Termination                                                      | •                               |                                              |                                      |      |        |      |       |  |

| Termination Current Set Factor                                          | K <sub>TERM</sub>               | Percentage of fast charge current            |                                      |      | 10 (2) |      | %     |  |

|                                                                         |                                 | $V_{SRP-SRN} = 4mV$                          |                                      | 2.9  | 3.9    | 4.8  |       |  |

| Termination Current Regulation Initial Accuracy                         |                                 | V <sub>SRP-SRN</sub> = 2mV                   |                                      | 0.9  | 1.8    | 2.7  | mV    |  |

| Deglitch Time for Termination (Both Edges)                              | t <sub>TERM_DEG</sub>           |                                              |                                      |      | 100    |      | ms    |  |

| Termination Qualification Time                                          | t <sub>QUAL</sub>               | $V_{SRN} > V_{RECH}$ and                     | I <sub>CHG</sub> < I <sub>TERM</sub> |      | 250    |      | ms    |  |

| Termination Qualification Current                                       | I <sub>QUAL</sub>               | Discharge curren<br>detected                 | t once termination is                |      | 2      |      | mA    |  |

| Input Under-Voltage Lockout Comparator                                  | (UVLO)                          |                                              |                                      |      |        |      |       |  |

| AC Under-Voltage Rising Threshold                                       | V <sub>UVLO</sub>               | Measure on AVC                               | C                                    | 2.9  | 3.3    | 3.8  | V     |  |

| AC Under-Voltage Hysteresis, Falling                                    | V <sub>UVLO_HYS</sub>           | Measure on AVC                               | C                                    |      | 210    |      | mV    |  |

| Sleep Comparator (Reverse Discharging P                                 | rotection)                      |                                              |                                      |      |        |      |       |  |

| Sleep Mode Threshold                                                    | V <sub>SLEEP</sub>              | V <sub>AVCC</sub> - V <sub>SRN</sub> falling |                                      |      | 90     | 280  | mV    |  |

| Sleep Mode Hysteresis                                                   | $V_{\text{SLEEP}_{\text{HYS}}}$ | V <sub>AVCC</sub> - V <sub>SRN</sub> rising  |                                      |      | 210    |      | mV    |  |

| Sleep Deglitch to Disable Charge                                        | t <sub>SLEEP_FALL_CD</sub>      | V <sub>AVCC</sub> - V <sub>SRN</sub> falling |                                      |      | 1      |      | ms    |  |

| Sleep Deglitch to Turn Off Input FETs                                   | t <sub>SLEEP_FALL_FETOFF</sub>  | V <sub>AVCC</sub> - V <sub>SRN</sub> falling |                                      |      | 5      |      | ms    |  |

| Deglitch to Enter Sleep Mode, Disable VREF and Enter Low Quiescent Mode | t <sub>sleep_fall</sub>         | V <sub>AVCC</sub> - V <sub>SRN</sub> falling |                                      |      | 100    |      | ms    |  |

| Deglitch to Exit SLEEP Mode, and Enable<br>VREF                         | t <sub>sleep_pwrup</sub>        | V <sub>AVCC</sub> - V <sub>SRN</sub> rising  | ]                                    |      | 30     |      | ms    |  |

| ACN-SRN Comparator                                                      |                                 |                                              |                                      |      |        |      |       |  |

| Threshold to Turn On BATFET                                             | V <sub>ACN-SRN</sub>            | $V_{ACN-SRN}$ falling                        |                                      |      | 180    | 400  | mV    |  |

| Hysteresis to Turn Off BATFET                                           | $V_{\text{ACN-SRN}_\text{HYS}}$ | $V_{ACN-SRN}$ rising                         |                                      |      | 110    |      | mV    |  |

| Deglitch to Turn On BATFET                                              | t <sub>BATFETOFF_DEG</sub>      | V <sub>ACN-SRN</sub> falling                 |                                      |      | 2      |      | ms    |  |

| Deglitch to Turn Off BATFET                                             | t <sub>BATFETON_DEG</sub>       | $V_{ACN-SRN}$ rising                         |                                      |      | 50     |      | μs    |  |

| Battery LOWV Comparator                                                 |                                 |                                              |                                      |      |        |      |       |  |

|                                                                         |                                 |                                              | CELL floating, 2-cell                | 5.7  | 5.8    | 6.1  |       |  |

| Dre Charge to Feet Charge Transition                                    | M                               | Measure on SRN<br>(SGM41526A)                | CELL to VREF, 3-cell                 | 8.4  | 8.7    | 9.1  |       |  |

| Pre-Charge to Fast Charge Transition                                    | V <sub>LOWV</sub>               | (00000000000000000000000000000000000000      | CELL to AGND, 4-cell                 | 11.1 | 11.7   | 12.2 | V     |  |

|                                                                         |                                 | Measure on FB (                              | SGM41527A)                           | 1.42 | 1.46   | 1.50 |       |  |

|                                                                         |                                 |                                              | CELL floating, 2-cell                |      | 400    |      |       |  |

|                                                                         | N                               | Measure on SRN<br>(SGM41526A)                | CELL to VREF, 3-cell                 |      | 600    |      |       |  |

| Fast Charge to Pre-Charge Hysteresis                                    | $V_{LOWV_HYS}$                  |                                              | CELL to AGND, 4-cell                 |      | 800    |      | mV    |  |

|                                                                         |                                 | Measure on FB (SGM41527A)                    |                                      |      | 100    |      | 1     |  |

| V <sub>LOWV</sub> Rising Deglitch                                       | t <sub>PRE2FAS</sub>            | Delay to start fast                          | charge current                       |      | 25     |      | ms    |  |

| V <sub>LOWV</sub> Falling Deglitch                                      | t <sub>FAST2PRE</sub>           | Delay to start pre                           | -charge current                      |      | 25     |      | ms    |  |

| PARAMETER                                                                                                        | SYMBOL                                     | CON                                                       | DITIONS                                             | MIN  | TYP   | MAX  | UNITS |

|------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------|------|-------|------|-------|

| Recharge Comparator                                                                                              |                                            |                                                           |                                                     |      |       |      |       |

|                                                                                                                  |                                            |                                                           | CELL floating, 2-cell                               | 110  | 200   | 290  |       |

| Recharge Threshold, below Regulation<br>Voltage Limit,                                                           |                                            | Measure on SRN<br>(SGM41526A)                             | CELL to VREF, 3-cell                                | 190  | 300   | 430  | -     |

| V <sub>BAT_REG</sub> - V <sub>SRN</sub> (SGM41526A),                                                             | V <sub>RECHG</sub>                         |                                                           | CELL to AGND, 4-cell                                | 280  | 400   | 540  | mV    |

| or $V_{FB_{REG}}$ - $V_{FB}$ (SGM41527A)                                                                         |                                            | Measure on FB (Se                                         | GM41527A)                                           | 50   | 70    | 90   |       |

| V <sub>RECHG</sub> Rising Deglitch                                                                               | t <sub>RECH_RISE_DEG</sub>                 | V <sub>FB</sub> decreasing bel                            | V <sub>FB</sub> decreasing below V <sub>RECHG</sub> |      | 10    |      | ms    |

| V <sub>RECHG</sub> Falling Deglitch                                                                              | t <sub>RECH_FALL_DEG</sub>                 | V <sub>FB</sub> increasing abo                            | $V_{FB}$ increasing above $V_{RECHG}$               |      | 10    |      | ms    |

| Battery Over-Voltage Comparator                                                                                  |                                            |                                                           |                                                     |      |       |      |       |

| Over-Voltage Rising Threshold                                                                                    | V <sub>OV_RISE</sub>                       | As percentage of V<br>or V <sub>FB_REG</sub> (SGM41       | ′ <sub>BAT_REG</sub> (SGM41526A)<br>527A)           |      | 104   |      | %     |

| Over-Voltage Falling Threshold                                                                                   | $V_{\text{OV}\_\text{FALL}}$               | As percentage of V<br>or V <sub>FB_REG</sub> (SGM41       |                                                     |      | 102   |      | %     |

| Input Over-Voltage Comparator (ACOV)                                                                             |                                            |                                                           |                                                     |      |       |      |       |

| AC Over-Voltage Rising Threshold to<br>Turn Off ACFET                                                            | V <sub>ACOV</sub>                          | OVPSET rising                                             |                                                     | 1.53 | 1.6   | 1.69 | V     |

| AC Over-Voltage Falling Hysteresis                                                                               | V <sub>ACOV_HYS</sub>                      | OVPSET falling                                            |                                                     |      | 40    |      | mV    |

| AC Over-Voltage Rising Deglitch to<br>Turn Off ACFET and Disable Charge                                          | t <sub>ACOV_RISE_DEG</sub>                 | OVPSET rising                                             |                                                     |      | 1     |      | μs    |

| AC Over-Voltage Falling Deglitch to<br>Turn On ACFET                                                             | $t_{ACOV\_FALL\_DEG}$                      | OVPSET falling                                            |                                                     |      | 30    |      | ms    |

| Input Under-Voltage Comparator (ACUV                                                                             | )                                          |                                                           |                                                     |      |       |      |       |

| AC Under-Voltage Falling Threshold to<br>Turn Off ACFET                                                          | V <sub>ACUV</sub>                          | OVPSET falling                                            |                                                     | 0.44 | 0.494 | 0.55 | V     |

| AC Under-Voltage Rising Hysteresis                                                                               | V <sub>ACUV_HYS</sub>                      | OVPSET rising                                             |                                                     |      | 80    |      | mV    |

| AC Under-Voltage Falling Deglitch to<br>Turn Off ACFET and Disable Charge<br>AC Under-Voltage Rising Deglitch to | t <sub>ACOV_FALL_DEG</sub>                 | OVPSET falling                                            |                                                     |      | 1     |      | μs    |

| Turn On ACFET                                                                                                    | $t_{\text{ACOV}\_\text{RISE}\_\text{DEG}}$ | OVPSET rising                                             |                                                     |      | 30    |      | ms    |

| Thermal Regulation                                                                                               |                                            |                                                           |                                                     |      |       |      |       |

| Junction Temperature Regulation Accuracy                                                                         | T <sub>A_REG</sub>                         | V <sub>ISET</sub> > 120mV, cha                            | irging                                              |      | 120   |      | °C    |

| Thermal Shutdown Comparator                                                                                      |                                            |                                                           |                                                     |      |       |      |       |

| Thermal Shutdown Rising Temperature                                                                              | T <sub>SHUT</sub>                          | Temperature rising                                        |                                                     |      | 150   |      | °C    |

| Thermal Shutdown Hysteresis                                                                                      | T <sub>SHUT_HYS</sub>                      | Temperature falling                                       | 1                                                   |      | 20    |      | °C    |

| Thermal Shutdown Rising Deglitch                                                                                 | T <sub>SHUT_RISE_DEG</sub>                 | Temperature rising                                        |                                                     |      | 100   |      | μs    |

| Thermal Shutdown Falling Deglitch                                                                                | T <sub>SHUT_FALL_DEG</sub>                 | Temperature falling                                       | 1                                                   |      | 10    |      | ms    |

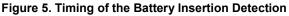

| Thermistor Comparator                                                                                            |                                            |                                                           |                                                     |      |       |      |       |

| Cold Temperature Threshold, TS Pin<br>Voltage Rising Threshold                                                   | VLTF                                       | Charger suspends as percentage of V                       |                                                     | 72.1 | 73.6  | 75.2 | %     |

| Cold Temperature Hysteresis, TS Pin<br>Voltage Falling                                                           | V <sub>LTF_HYS</sub>                       | As percentage of V <sub>VREF</sub>                        |                                                     |      | 0.68  | 1.45 | %     |

| Hot Temperature TS Pin Voltage Rising<br>Threshold                                                               | V <sub>HTF</sub>                           | As percentage of V <sub>VREF</sub>                        |                                                     | 45.8 | 47.3  | 48.8 | %     |

| Cut-Off Temperature TS Pin Voltage<br>Falling Threshold                                                          | V <sub>TCO</sub>                           | As percentage of V                                        | VREF                                                | 43.2 | 44.6  | 45.7 | %     |

| Deglitch Time for Temperature out of<br>Range Detection                                                          | t <sub>TS_CHG_SUS</sub>                    | $V_{TS}$ > $V_{LTF}$ , or $V_{TS}$ <                      | $V_{TCO}$ , or $V_{TS} < V_{HTF}$                   |      | 20    |      | ms    |

| Deglitch Time for Temperature in Valid<br>Range Detection                                                        | t <sub>TS_CHG_RESUME</sub>                 | $V_{TS} < V_{LTF} - V_{LTF_HYS}$<br>or $V_{TS} > V_{HTF}$ | $_{\rm S}$ or V <sub>TS</sub> > V <sub>TCO</sub> ,  |      | 400   |      | ms    |

| PARAMETER                                                             | SYMBOL                        | CONDITIONS                                                                      | MIN  | TYP               | MAX  | UNITS  |

|-----------------------------------------------------------------------|-------------------------------|---------------------------------------------------------------------------------|------|-------------------|------|--------|

| Charge Over-Current Comparator (Cycle-b                               | y-Cycle)                      |                                                                                 |      |                   |      |        |

| Charge Over-Current Rising Threshold,<br>V <sub>SRP</sub> > 2.2V      | V <sub>OCP_CHRG</sub>         | Current as percentage of fast charge current                                    |      | 180               |      | %      |

| Charge Over-Current Limit Min, $V_{SRP}$ < 2.2V                       | $V_{\text{OCP}_{\text{MIN}}}$ | Measure V <sub>SRP-SRN</sub>                                                    |      | 46                |      | mV     |

| Charge Over-Current Limit Max, $V_{SRP} > 2.2V$                       | V <sub>OCP_MAX</sub>          | Measure V <sub>SRP-SRN</sub>                                                    |      | 77                |      | mV     |

| HSFET Over-Current Comparator (Cycle-b                                | y-Cycle)                      |                                                                                 |      |                   |      |        |

| Current Limit on HSFET                                                | I <sub>OCP_HSFET</sub>        | Measure on HSFET                                                                |      | 10                |      | Α      |

| Charge Under-Current Comparator (Cycle-                               | by-Cycle)                     |                                                                                 |      |                   |      |        |

| Charge Under-Current Falling Threshold                                | V <sub>UCP</sub>              | Measure on $V_{\text{SRP-SRN}}$                                                 | 1    | 5                 | 12   | mV     |

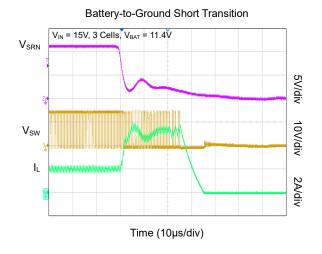

| Battery Short Comparator                                              |                               |                                                                                 |      |                   |      |        |

| Battery Short Falling Threshold                                       | VBATSHT                       | Measure on SRN                                                                  |      | 2                 |      | V      |

| Battery Short Rising Hysteresis                                       | $V_{BATSHT_HYS}$              | Measure on SRN                                                                  |      | 200               |      | mV     |

| Deglitch on Both Edges                                                | t <sub>BATSHT_DEG</sub>       |                                                                                 |      | 1                 |      | μs     |

| Charge Current during BAT_SHORT                                       | VBATSHT                       | Percentage of fast charge current                                               |      | 10 <sup>(2)</sup> |      | %      |

| VREF Regulator                                                        |                               |                                                                                 |      |                   |      |        |

| VREF Regulator Voltage                                                | $V_{VREF\_REG}$               | V <sub>AVCC</sub> > V <sub>UVLO</sub> , no load                                 | 3.24 | 3.3               | 3.36 | V      |

| VREF Current Limit                                                    | I <sub>VREF_LIM</sub>         | $V_{VREF} = 0V, V_{AVCC} > V_{UVLO}$                                            | 20   |                   | 80   | mA     |

| REGN Regulator                                                        |                               |                                                                                 | •    |                   | •    |        |

| REGN Regulator Voltage                                                | $V_{REGN_{REG}}$              | V <sub>AVCC</sub> > 10V, V <sub>ISET</sub> > 120mV                              | 4.8  | 5.0               | 5.2  | V      |

| REGN Current Limit                                                    | I <sub>REGN_LIM</sub>         | $V_{REGN} = 0V, V_{AVCC} > 10V, V_{ISET} > 120mV$                               | 20   |                   | 100  | mA     |

| TTC Input                                                             |                               |                                                                                 |      |                   |      | -      |

| Pre-Charge Safety Timer                                               | t <sub>PRECHRG</sub>          | Pre-charge time before fault occurs                                             |      | 1800              |      | s      |

| Fast Charge Timer Range                                               | t <sub>FASTCHRG</sub>         | $T_{CHG} = C_{TTC} \times K_{TTC}$                                              | 1    |                   | 10   | hr     |

| Fast Charge Timer Accuracy                                            |                               |                                                                                 | -10  |                   | 10   | %      |

| Timer Multiplier                                                      | K <sub>TTC</sub>              |                                                                                 |      | 5.6               |      | min/nF |

| TTC Low Threshold                                                     | V <sub>TTC_LOW</sub>          | TTC falling                                                                     |      | 0.33              |      | V      |

| TTC Source/Sink Current                                               | ITTC                          |                                                                                 | 45   | 50                | 55   | μA     |

| TTC Oscillator High Threshold                                         | V <sub>TTC_OSC_HI</sub>       |                                                                                 |      | 1.5               |      | V      |

| TTC Oscillator Low Threshold                                          | V <sub>TTC_OSC_LO</sub>       |                                                                                 |      | 1.0               |      | V      |

| Battery Switch (BATFET) Driver                                        |                               |                                                                                 |      |                   |      |        |

| BATFET Turn-Off Resistance                                            | $R_{DS\_BAT\_OFF}$            | V <sub>AVCC</sub> > 5V                                                          |      |                   | 200  | Ω      |

| BATFET Turn-On Resistance                                             | $R_{DS\_BAT\_ON}$             | V <sub>AVCC</sub> > 5V                                                          |      |                   | 10   | kΩ     |

| BATFET Drive Voltage                                                  | V <sub>BATDRV_REG</sub>       | $V_{BATDRV_{REG}} = V_{ACN} - V_{BATDRV}$ when $V_{AVCC} > 5V$ and BATFET is on | 5.1  |                   | 6.4  | V      |

| BATFET Power-Up Delay to Turn Off<br>BATFET after Adapter is Detected | t <sub>BATFET_DEG</sub>       |                                                                                 |      | 30                |      | ms     |

| AC Switch (ACFET) Driver                                              |                               |                                                                                 | -    |                   |      |        |

| ACDRV Charge Pump Current Limit                                       | I <sub>ACFET</sub>            | V <sub>ACDRV</sub> - V <sub>CMSRC</sub> = 5V                                    |      | 160               |      | μA     |

| Gate Drive Voltage on ACFET                                           | V <sub>ACDRV_REG</sub>        | $V_{ACDRV}$ - $V_{CMSRC}$ when $V_{AVCC}$ > $V_{UVLO}$                          | 5.4  | 5.6               |      | V      |

| Maximum Load between ACDRV and CMSRC                                  | R <sub>ACDRV_LOAD</sub>       |                                                                                 | 20   |                   |      | kΩ     |

$(T_J = -40^{\circ}C \text{ to } +85^{\circ}C, 4.5V \le V_{PVCC}, V_{AVCC} \le 22V \text{ (referred to AGND), typical values at } T_J = +25^{\circ}C, \text{ unless otherwise noted.)}$

| PARAMETER                                                                    | SYMBOL CONDITIONS             |                                                                                                        | MIN  | TYP  | MAX  | UNITS   |

|------------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------|------|------|------|---------|

| AC/BAT Switch Driver Timing                                                  |                               |                                                                                                        |      |      |      |         |

| Driver Dead Time                                                             | t <sub>DRV_DEAD</sub>         | Dead time when switching between ACFET and BATFET                                                      |      | 10   |      | μs      |

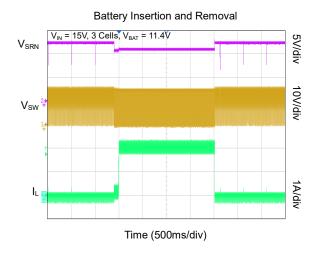

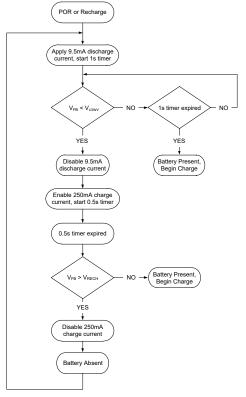

| Battery Detection                                                            |                               |                                                                                                        |      |      |      |         |

| Wake Timer                                                                   | t <sub>WAKE</sub>             | Max time charge is enabled                                                                             |      | 500  |      | ms      |

| Wake Current                                                                 | I <sub>WAKE</sub>             | R <sub>SENSE</sub> = 10mΩ                                                                              | 100  | 250  | 400  | mA      |

| Discharge Timer                                                              | t <sub>DISCH</sub>            | Max time discharge current is applied                                                                  |      | 1    |      | s       |

| Discharge Current                                                            | I <sub>DISCH</sub>            |                                                                                                        |      | 9.5  |      | mA      |

| Fault Current after a Time-Out Fault                                         | I <sub>FAULT</sub>            |                                                                                                        |      | 2    |      | mA      |

| Wake Threshold with Respect to $V_{\text{REG}}$ to Detect Absent during Wake | V <sub>WAKE</sub>             | Measure on SRN (SGM41526A)                                                                             |      | 100  |      | mV/cell |

| Discharge Threshold to Detect Battery<br>Absent during Discharge             | V <sub>DISCH</sub>            | Measure on SRN (SGM41526A)                                                                             |      | 2.9  |      | V/cell  |

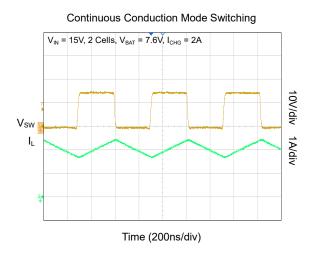

| Internal PWM                                                                 |                               |                                                                                                        |      |      |      |         |

| PWM Switching Frequency                                                      | f <sub>sw</sub>               |                                                                                                        | 1200 | 1600 | 1800 | kHz     |

| Driver Dead Time (1)                                                         | t <sub>SW_DEAD</sub>          | Dead time when switching between LSFET and HSFET no load                                               |      | 30   |      | ns      |

| High-side MOSFET On-Resistance                                               | R <sub>DS_HI</sub>            | V <sub>BTST</sub> - V <sub>SW</sub> = 4.5V                                                             |      | 29   | 55   | mΩ      |

| Low-side MOSFET On-Resistance                                                | R <sub>DS_LO</sub>            |                                                                                                        |      | 33   | 65   | mΩ      |

| Bootstrap Refresh Comparator Threshold                                       | V <sub>BTST_REFRESH</sub>     | $V_{\text{BTST}}$ - $V_{\text{SW}}$ when low-side refresh pulse is requested, $V_{\text{AVCC}}$ = 4.5V | 2.8  |      |      |         |

| Voltage                                                                      |                               | $V_{BTST}$ - $V_{SW}$ when low-side refresh pulse is requested, $V_{AVCC}$ > 6V                        | 2.8  |      |      | - V     |

| Internal Soft-Start (8 Steps to Regulatio                                    | n Current I <sub>CHG</sub> )  | •                                                                                                      |      |      | I    |         |

| Soft-Start Steps                                                             | SS_STEP                       |                                                                                                        |      | 8    |      | step    |

| Soft-Start Step Time                                                         | t <sub>ss_step</sub>          |                                                                                                        |      | 1.6  | 3    | ms      |

| Charger Section Power-Up Sequencing                                          |                               | •                                                                                                      |      | •    |      |         |

| Delay from ISET above 120mV to Start<br>Charging Battery                     | t <sub>CE_DELAY</sub>         |                                                                                                        |      | 1.5  |      | s       |

| Integrated BTST Diode                                                        |                               |                                                                                                        |      |      |      |         |

| Forward Bias Voltage                                                         | V <sub>F</sub>                | I <sub>F</sub> = 120mA at +25°C                                                                        |      | 0.85 |      | V       |

| Reverse Breakdown Voltage                                                    | V <sub>R</sub>                | I <sub>R</sub> = 2μA at +25°C                                                                          | 21   |      |      | V       |

| Logic IO Pin Characteristics (STAT, CEL                                      | .L)                           |                                                                                                        |      |      |      |         |

| STAT Output Low Saturation Voltage                                           | V <sub>OUT_LO</sub>           | Sink current = 5mA                                                                                     |      |      | 0.6  | V       |

| CELL Pin Input Low Threshold, 4-Cell (SGM41526A)                             | V <sub>CELL_LO</sub>          | CELL pin voltage falling edge                                                                          |      | 0.3  |      | V       |

| CELL Pin Input Mid Threshold, 2-Cell (SGM41526A)                             | $V_{\text{CELL}\_\text{MID}}$ | CELL pin middle level voltage                                                                          | 0.7  |      | 2.5  | V       |

| CELL Pin Input High Threshold, 3-Cell                                        | $V_{CELL_{HI}}$               | CELL pin voltage rising edge                                                                           |      | 2.7  |      | V       |

#### NOTES:

1. Specified by design.

2. The minimum current is 250mA on  $10m\Omega$  sense resistor.

SGM41526A SGM41527A

## 1.6MHz Synchronous Li-Ion/Li-Polymer Stand-Alone **Battery Chargers with Automatic Power Path Selector**

## **TYPICAL PERFORMANCE CHARACTERISTICS**

Time (200ms/div)

SG Micro Corp SGMICRO www.sg-micro.com

$\mathsf{I}_{\mathsf{L}}$

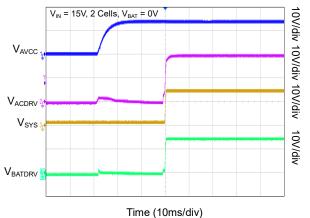

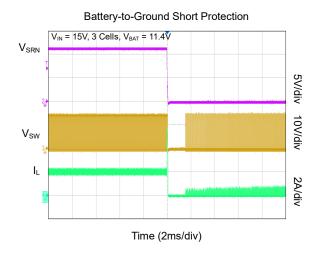

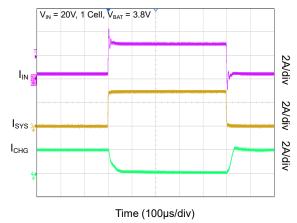

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

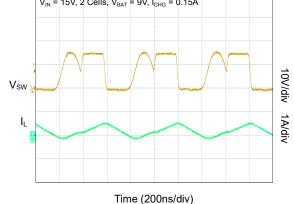

Discontinuous Conduction Mode Switching  $V_{IN} = 15V, 2 \text{ Cells}, V_{BAT} = 9V, I_{CHG} = 0.15A$

System Load Transient (Input Current DPM)

SG Micro Corp

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

SGM41526A SGM41527A

## 1.6MHz Synchronous Li-Ion/Li-Polymer Stand-Alone Battery Chargers with Automatic Power Path Selector

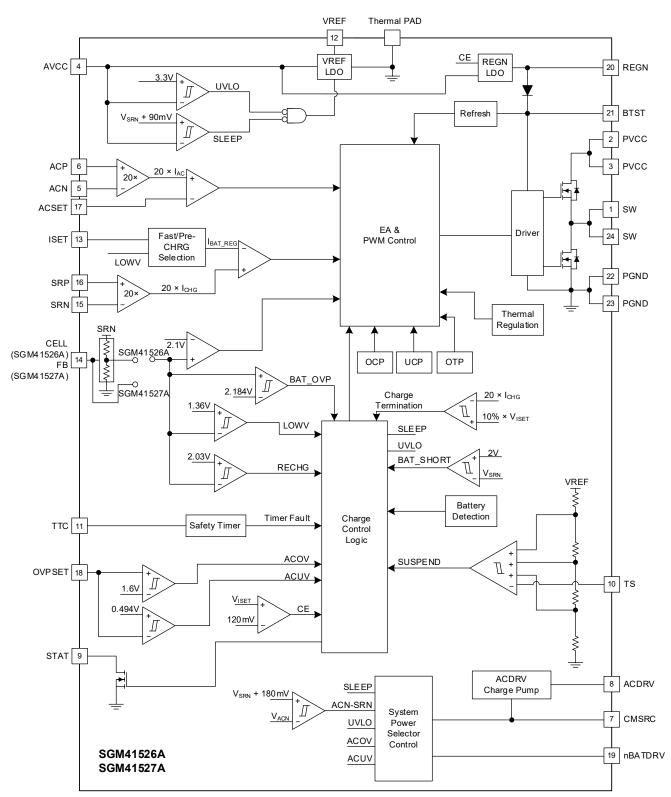

## FUNCTIONAL BLOCK DIAGRAM

Figure 2. Functional Block Diagram

## DETAILED DESCRIPTION

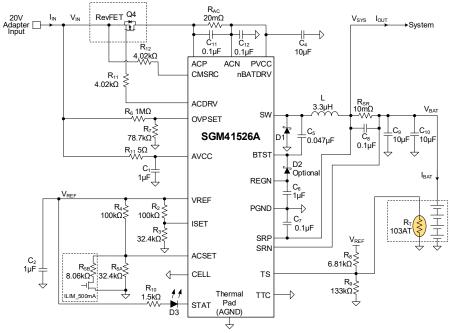

The SGM41526A and SGM41527A are Li-Ion and Li-polymer fixed-frequency synchronous PWM battery chargers with integrated switching power MOSFETs. Using external switches, power path management is provided along with accurate regulation of the input current, charge current and battery voltage. The internal block diagram is given in Figure 2.

### **Battery Voltage Regulation**

An accurate PWM voltage regulator is used for charge voltage regulation. For the SGM41526A, the number of battery cells depends on the CELL pin. Two (CELL = floating), three (CELL = VREF) or four (CELL = AGND) cells can be connected in series with a fixed nominal voltage of 4.2V per cell. Table 1 shows the charge regulation voltage in each case.

Table 1. Defining Number of Battery Cells for SGM41526A

| CELL Pin Voltage | Charge Regulation Voltage |

|------------------|---------------------------|

| Floating         | 8.4V (2 Cells)            |

| VREF             | 12.6V (3 Cells)           |

| AGND             | 16.8V (4 Cells)           |

For the SGM41527A, the regulation voltage is adjustable. The FB voltage is compared to an internal 2.1V voltage reference like a conventional voltage regulator. The regulation voltage can be adjusted by using an external resistor divider on the battery voltage (output voltage). Connect the center point of the resistor divider to the FB pin. The battery regulation voltage (V<sub>BAT</sub>) in the SGM41527A is calculated by Equation 1:

$$V_{BAT} = 2.1V \times \left(1 + \frac{R_1}{R_2}\right)$$

(1)

where

$\bullet$  R1 is connected between the battery positive terminal and FB.

• R<sub>2</sub> is connected between FB and AGND.

### **Battery Current Regulation**

The maximum charging current for fast charge is set by the ISET input. Connect battery current sense resistor ( $R_{SR}$ ) between SRP and SRN. The equation for charge current is given by:

$$I_{CHG} = \frac{V_{ISET}}{20 \times R_{SR}}$$

(2)

The maximum of the full-scale SRP-SRN differential voltage is 40mV, and it determines the maximum charge current selected by ISET. The maximum valid input voltage of ISET is 0.8V. For example, with a  $10m\Omega$  sense resistor, the maximum

adjustable charge current is 4A, and with a 20m $\Omega$  resistor, it is 2A. If V<sub>ISET</sub> = 0.5V and R<sub>SR</sub> = 10m $\Omega$ , the fast charge current is I<sub>CHG</sub> = 2.5A.

Pulling the ISET voltage down to ground (below 30mV) disables the charger. To enable the charger, the ISET voltage should exceed 120mV. The minimum charge current is limited by the 120mV threshold level. For example, when  $R_{SR} = 10m\Omega$ , the minimum fast charge current is no less than 600mA.

As a protective feature, if the device junction temperature exceeds +120 °C, the charge current folds back and is internally reduced to keep the junction temperature below +120 °C.

### **Pre-Charge Phase**

If the battery voltage is lower than  $V_{LOWV}$  when the device is powered up, the charge will start with a small pre-charge current to safely recover the battery from deep discharge state. If the battery voltage still does not exceed the  $V_{LOWV}$ threshold after 30 minutes, charging will stop, and fault status will be declared by the status pins.  $V_{LOWV}$  is typically 2.9V/cell for SGM41526A and 1.46V on FB pin for SGM41527A. The pre-charge current is determined by the fast charge current as a ratio of 10%:

$$I_{PRECHARGE} = \frac{V_{ISET}}{200 \times R_{SR}}$$

(3)

The deglitch time of fast charge and pre-charge transition is 25ms.

### **Typical Charge Cycle**

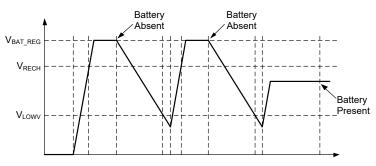

Figure 3 shows a complete charge cycle profile (battery voltage and current versus time) with all the three phases followed by a typical discharge and auto recharge. The charge is started assuming that the battery is in a deep discharge state (low battery voltage). After termination and stopping the charge, the battery is normally discharged by system loads. When the voltage falls below the recharge threshold, another cycle is initiated from fast charge, to bring the battery back to the full charge state. A new charging cycle begins when any of the following conditions is met:

- $\bullet$  The SRN pin voltage falls below the recharge threshold (V\_{RECH}).

- A power-on-reset (POR).

• Disable and enable charge by pulling ISET pin below 30mV and then above 120mV, respectively.

Depending on the battery voltage, the charge is started with the proper phase. Charge sequence details will be explained in the next sections.

## **DETAILED DESCRIPTION (continued)**

Figure 3. Typical Charge and Discharge Profile

### **Regulation of the Input Current**

The input current is used to power the system and to charge the battery. System current may vary from zero to maximum load. With dynamic power management (DPM) capability, the adapter does not need to be designed for maximum power demand for both charge and system at the same time. Otherwise it will lead to a bulky AC adapter and relatively higher cost. With DPM, the charge current is reduced when the system has high demand for power, such that the input current is regulated to a predefined maximum. Therefore, the AC adapter can be designed for lower power that results in smaller adapter size and cost.