# Fully Integrated Switch-Mode Charger with USB Compliance and USB OTG Support

#### GENERAL DESCRIPTION

The SGM41517 is a tiny, high-efficiency, USB supported switch-mode charger, which can be used to charge the single-cell Li-lon and Li-polymer batteries in portable applications.

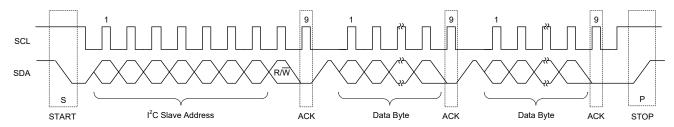

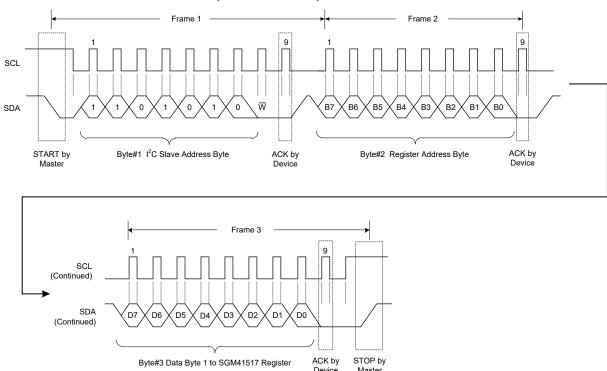

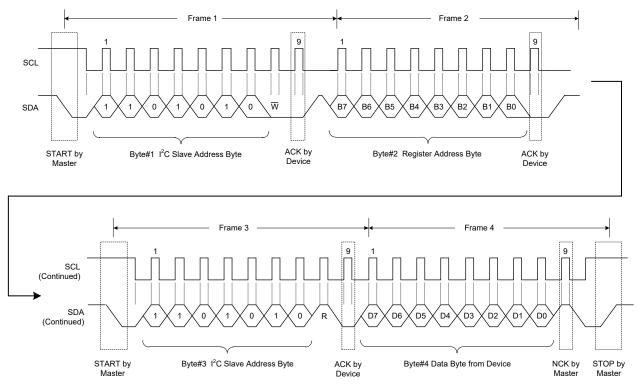

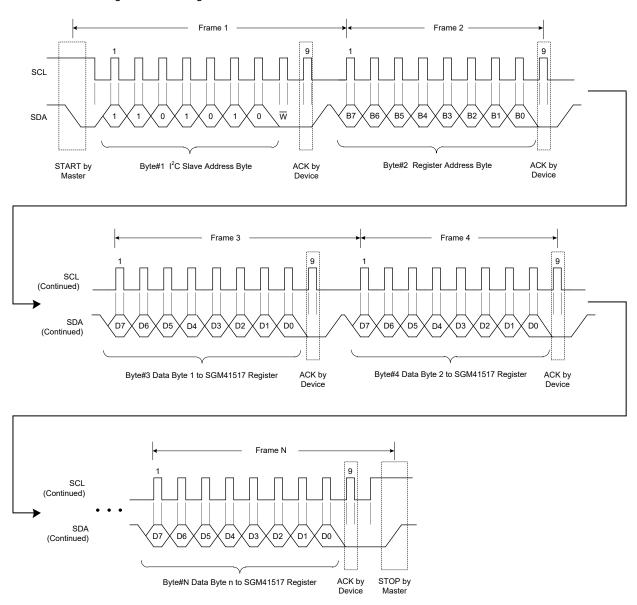

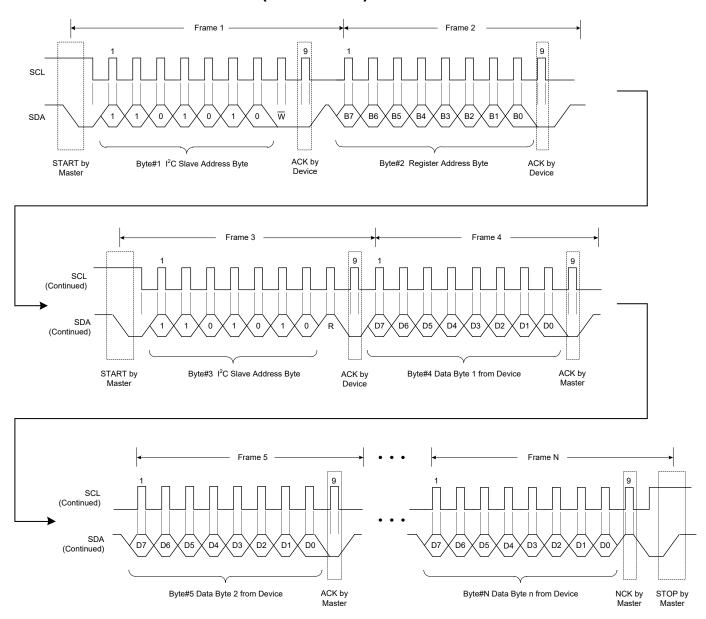

The SGM41517 has the I<sup>2</sup>C interface to program the charging parameters. It integrates a synchronous PWM controller, input and output current sensing, high-accuracy voltage and current regulation, power MOSFETs, and charge termination.

The SGM41517 charges the battery in three stages: short charging current, constant current charging, and constant voltage charging. The input current is automatically limited to the value set by host. The device terminates the charging based on the battery voltage and user selectable minimum current level. The charging safety timer provides the additional protection for the battery. During normal operation, if the battery voltage drops below the internal threshold, the IC will automatically restart the charging cycle and enter the sleep mode or the high-impedance mode when the input power is disconnected. The charging status can be read back to the host by the I<sup>2</sup>C interface. This device also features thermal regulation in which the charge current is reduced if the junction temperature exceeds 120°C.

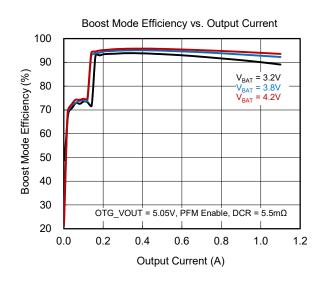

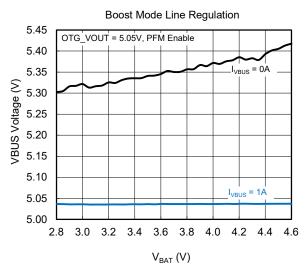

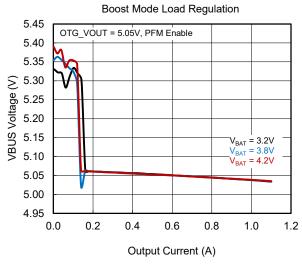

For supporting the USB OTG device, the SGM41517 can boost the battery voltage to 5.05V by default at VBUS node.

The SGM41517 is available in a Green UTQFN-2×2-20L package.

#### **APPLICATIONS**

Portable Audio Speaker Mobile Phone Wearables EPOS

#### **FEATURES**

- 4V to 13.2V Operating Input Voltage Range

- 19V Absolute Maximum Input Voltage Rating

SGM41517

- Instant-On with No Battery

- Maximum Power Tracking by Programmable Input Voltage Limit (VINDPM)

- Bad Adapter Detection and Recognition

- Safety Limit Register for Maximum Charge Voltage and Current Limiting

- Integrated Input Current Sensing and Limiting

- Integrated Power FETs for up to 2A Charge Current

- Programmable Charging Parameters via I<sup>2</sup>C-Compatible Interface (up to 1Mbps):

- VINDPM Threshold

- Input Current Limit

- Fast-Charge/Termination Current

- Charge Regulation Voltage: 3.5V to 4.6V

- Termination Function

- Integrated Charging Current Sensing Resistor

- Operating at 1.5MHz/500kHz in Charger Mode, 1.5MHz in Boost Mode

- Status Indication for Charging and Faults

- USB Friendly Startup Sequence

- JEITA Guideline Compliance

- Optional Charge Current at T1 T2

- Optional Charge Prohibited when > T3

- Boost Mode Range

- Battery Input Voltage Range: 3.2V to 4.6V

- 1.4A Output Current

- High-Accuracy

- ±5% Input Current Regulation at 500mA

- ±0.4% Charge Voltage Regulation at T<sub>J</sub> = +25°C

- ±0.5% Charge Voltage Regulation at T<sub>J</sub> = 0°C to +85°C

- Safety

- Reverse Leakage Protection from BAT to VBUS

- Thermal Regulation and Thermal Shutdown

- VBUS/VBAT Over-Voltage Protection

- Available in a Green UTQFN-2×2-20L Package

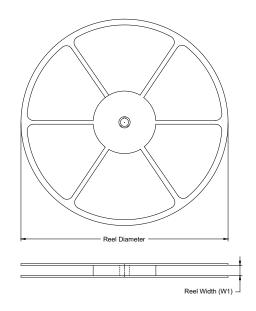

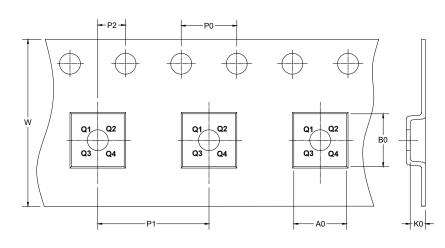

#### PACKAGE/ORDERING INFORMATION

| MODEL    | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING | PACKING<br>OPTION   |

|----------|------------------------|-----------------------------------|--------------------|--------------------|---------------------|

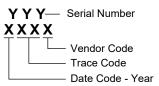

| SGM41517 | UTQFN-2×2-20L          | -40°C to +85°C                    | SGM41517YUVQ20G/TR | 0UI<br>XXXX        | Tape and Reel, 3000 |

#### MARKING INFORMATION

NOTE: XXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range (with Respect to PGND)                            |                          |

|-----------------------------------------------------------------|--------------------------|

| Supply Voltage: VBUS (V <sub>PMID</sub> ≥ V <sub>VBUS</sub> - 0 | 0.3V)                    |

|                                                                 | 2V <sup>(1)</sup> to 19V |

| Input Voltage: SCL, SDA, OTG, BAT, C                            | D_TS                     |

|                                                                 | 0.3V to 6V               |

| Output Voltage:                                                 |                          |

| PMID                                                            | 0.3V to 19V              |

| VREF, STAT                                                      | 6V                       |

| BOOT                                                            | 0.7V to 19V              |

| SW                                                              | 2V <sup>(1)</sup> to 16V |

| Voltage Difference between BOOT and S                           | W Inputs                 |

| V <sub>BOOT</sub> - V <sub>SW</sub>                             | 0.3V to 6V               |

| Voltage Difference between VBUS and PI                          | MID Inputs               |

| V <sub>VBUS</sub> - V <sub>PMID</sub>                           | 6V to 0.7V               |

| Voltage Difference between PMID and SV                          | V Inputs                 |

| V <sub>PMID</sub> - V <sub>SW</sub>                             | 0.7V to 19V              |

| Output Sink, STAT                                               | 10mA                     |

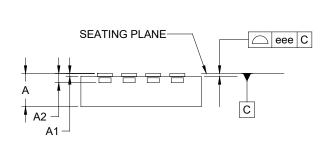

| Package Thermal Resistance                                      |                          |

| UTQFN-2×2-20L, θ <sub>JA</sub>                                  | 74.9°C/W                 |

| UTQFN-2×2-20L, θ <sub>JB</sub>                                  | 22.8°C/W                 |

| UTQFN-2×2-20L, $\theta_{JC}$                                    | 38.5°C/W                 |

| Junction Temperature                                            | +150°C                   |

| Storage Temperature Range                                       | 65°C to +150°C           |

| Lead Temperature (Soldering, 10s)                               | +260°C                   |

| ESD Susceptibility (2) (3)                                      |                          |

| HBM                                                             | ±2000V                   |

|                                                                 |                          |

| CDM                                                             | ±1000V                   |

## NOTES:

1. 20ns duration.

- 2. For human body model (HBM), all pins comply with ANSI/ESDA/JEDEC JS-001 specifications.

- 3. For charged device model (CDM), all pins comply with ANSI/ESDA/JEDEC JS-002 specifications.

#### RECOMMENDED OPERATING CONDITIONS

| Supply Voltage Range                 | 4V to 13.2V     |

|--------------------------------------|-----------------|

| Fast Charging Current, IBATOP        | 2A (MAX)        |

| Operating Ambient Temperature Range  | 40°C to +85°C   |

| Operating Junction Temperature Range | -40°C to +125°C |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

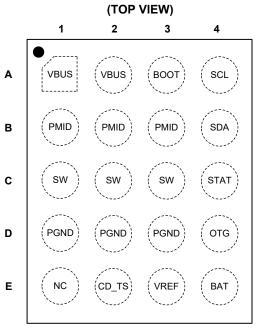

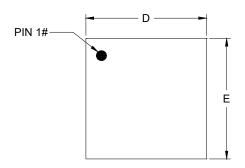

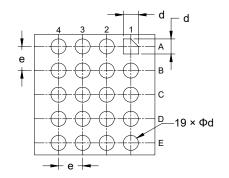

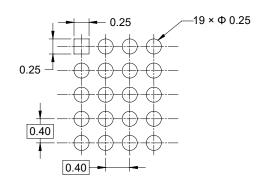

## **PIN CONFIGURATION**

UTQFN-2×2-20L

## **PIN DESCRIPTION**

| PIN        | NAME | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

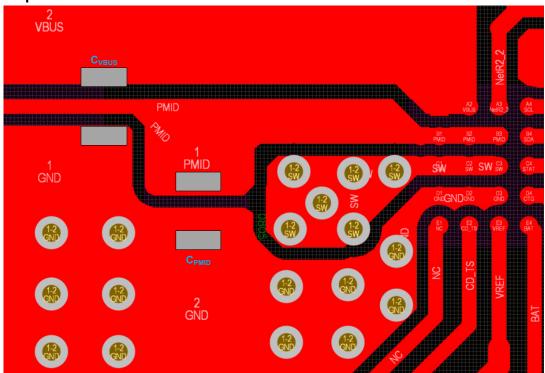

| A1, A2     | VBUS | I/O  | Charger Input (VIN). The internal N-channel reverse blocking MOSFET (RBFET) is connected between VBUS and PMID pins. Place a $1\mu F$ ceramic capacitor from VBUS pin to PGND close to the device.                                                                                                                                                                                                                                                                                                                                                  |

| А3         | воот | I/O  | High-side Driver Positive Supply. It is internally connected to the bootstrap diode cathode. Use a 33nF ceramic capacitor from SW pin to BOOT pin.                                                                                                                                                                                                                                                                                                                                                                                                  |

| A4         | SCL  | I    | $I^2$ C Clock Signal. Use a 10kΩ pull-up to the logic high rail.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| B1, B2, B3 | PMID | I/O  | PMID Pin. PMID is the actual higher voltage port of converter (Buck or Boost) and is connected to the drain of the reverse blocking MOSFET (RBFET) and the drain of HSFET. Connect at least a $4.7\mu F$ ceramic capacitor from PMID pin to PGND. It is the proper point for decoupling of high frequency switching currents.                                                                                                                                                                                                                       |

| B4         | SDA  | I/O  | l <sup>2</sup> C Data Signal. Use a 10kΩ pull-up to the logic high rail.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| C1, C2, C3 | SW   | 0    | Switching Node Output. Connect SW pin to the output inductor. Connect a 33nF bootstrap capacitor from SW pin to BOOT pin.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| C4         | STAT | 0    | Charge Status Indication Pin. This pin is used to drive a LED or communicate with a host processor.  During charge: low Other normal conditions: open-drain During faults: a 128µs low-level pulse is sent out. The function can be disabled via EN_STAT register.                                                                                                                                                                                                                                                                                  |

| D1, D2, D3 | PGND | _    | Power Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| D4         | OTG  | ı    | Input Current Limiting Selection or Boost Mode Enable Control Pin. During power-on reset in default mode, the OTG pin is used as the input current limiting selection pin. When OTG = High, $I_{\text{IN\_LIMIT}}$ = 500mA and when OTG = Low, $I_{\text{IN\_LIMIT}}$ = 100mA. When the $I^2$ C link to the host is established, the host can program a different input current limit value by writing to the IIN_LIMIT_2 and IIN_LIMIT_1 registers. Also, the OTG pin is together with the EN_OTG and OTG_PL bits to activate the Boost regulator. |

## **PIN DESCRIPTION (continued)**

| PIN | NAME  | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E1  | NC    | _    | No Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| E2  | CD_TS | I    | 1. Charge Disable Control Pin when EN_JEITA Bit = 0 (Default). CD_TS = LOW, charge is enabled. CD_TS = HIGH, charge is disabled and VBUS pin is high-impedance to GND.  2. Temperature Qualification Voltage Input (Supports JEITA Profile) when EN_JEITA Bit = 1. Connect to the battery NTC thermistor that is grounded on the other side. To program operating temperature window, it can be biased by a resistor divider between VREF and GND. |

| E3  | VREF  | 0    | LDO Output that Powers LSFET Driver and Internal Circuits. Place at least a $1\mu F$ ceramic capacitor from this output to PGND. It is not recommended to connect the external load on VREF.                                                                                                                                                                                                                                                       |

| E4  | BAT   | I    | Battery Voltage Sense Input. If there is a long wire connection to battery, bypass to PGND with the ceramic capacitors (minimum $0.1\mu F + 22\mu F$ ).                                                                                                                                                                                                                                                                                            |

NOTE: I = input, O = output, I/O = input or output.

## **ELECTRICAL CHARACTERISTICS**

$(V_{VBUS} = 5V, HZ\_MODE = 0, OPA\_MODE = 0 (CD\_TS = LOW), T_J = -40^{\circ}C$  to +125°C, typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                                                          | SYMBOL                     | CONDITIONS                                                                                                                           | MIN   | TYP | MAX  | UNITS |  |

|--------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------|-----|------|-------|--|

| Input Currents                                                     |                            |                                                                                                                                      |       |     |      |       |  |

|                                                                    |                            | VBUS > VBUS (min), PWM switching                                                                                                     |       | 10  |      |       |  |

| VBUS Supply Current Control                                        | I <sub>VBUS</sub>          | VBUS > VBUS (min), PWM not switching                                                                                                 |       |     | 2.5  | mA    |  |

| vace supply sumant control                                         | IVBUS                      | CD_TS = HIGH or HZ_MODE = 1,<br>0°C < T <sub>J</sub> < +85°C                                                                         |       | 15  | 25   | μΑ    |  |

| Leakage Current from Battery to VBUS Pin                           |                            | $V_{BAT}$ = 4.2V, high-impedance mode, $V_{VBUS}$ = 0V                                                                               |       |     | 1    | μΑ    |  |

| Battery Discharge Current in High-Impedance<br>Mode (BAT, SW Pins) | I <sub>LGK</sub>           | $V_{BAT}$ = 4.2V, high-impedance mode,<br>$V_{VBUS}$ = 0V, SCL, SDA, OTG = 0V or 1.8V,<br>$0^{\circ}$ C < $T_{J}$ < +85 $^{\circ}$ C |       |     | 20   | μА    |  |

| Voltage Regulation                                                 |                            |                                                                                                                                      |       |     |      |       |  |

| VBAT Regulation Voltage Programmable Range                         | V <sub>BAT_REG_RANGE</sub> | Operating in voltage regulation, programmable                                                                                        | 3.5   |     | 4.6  | V     |  |

| Voltage Regulation Accuracy                                        | V <sub>BAT_REG_ACC</sub>   | V <sub>BAT_REG</sub> = 4.2V, 0°C < T <sub>J</sub> < +85°C                                                                            | -0.5  |     | 0.5  | %     |  |

| Current Regulation (Fast Charge)                                   |                            |                                                                                                                                      |       |     |      |       |  |

| Fast Charge Current Programmable Range                             | I <sub>CHG_RANGE</sub>     | V <sub>LOWV</sub> ≤ V <sub>BAT</sub> < V <sub>BAT_REG</sub> , V <sub>VBUS</sub> > V <sub>SLP</sub> , programmable by ICHGR[3:0]      | 200   |     | 2000 | mA    |  |

| Foot Change Compat Boundation Catting                              |                            | I <sub>CHG</sub> = 500mA (ICHGR[3:0] = 000)                                                                                          | 475   |     | 625  | A     |  |

| Fast Charge Current Regulation Setting                             | I <sub>CHG</sub>           | I <sub>CHG</sub> = 2A (ICHGR[3:0] = 1111)                                                                                            | 1890  |     | 2110 | mA    |  |

| Weak Battery Detection                                             |                            |                                                                                                                                      |       |     |      |       |  |

| Weak Battery Voltage Threshold Programmable Range <sup>(1)</sup>   | V <sub>LOWV_RANGE</sub>    | Adjustable using I <sup>2</sup> C control                                                                                            | 3.35  |     | 3.65 | V     |  |

| Weak Battery Voltage Accuracy                                      | V <sub>LOWV_ACC</sub>      | V <sub>LOWV</sub> = 3.35V                                                                                                            | -6    |     | 7    | %     |  |

| Treak Battery Veltage / toodrady                                   |                            | V <sub>LOWV</sub> = 3.65V                                                                                                            | -6    |     | 7    |       |  |

| Hysteresis for V <sub>LOWV</sub>                                   | V <sub>LOWV_HYS</sub>      | Battery voltage falling                                                                                                              |       | 150 |      | mV    |  |

| CD_TS, OTG Pin Logic Level                                         |                            |                                                                                                                                      |       |     | ,    |       |  |

| Input Low Threshold Level                                          | V <sub>IL</sub>            |                                                                                                                                      |       |     | 0.5  | V     |  |

| Input High Threshold Level                                         | V <sub>IH</sub>            | 1.2V I/O, I2C_HI_DETC = 1,<br>-40°C < T <sub>J</sub> < +85°C                                                                         | 0.848 |     |      | V     |  |

|                                                                    |                            | 1.8V I/O, I2C_HI_DETC = 0                                                                                                            | 1.1   |     |      |       |  |

| Input Bias Current                                                 | I <sub>BIAS</sub>          | Voltage on control pin is 5V                                                                                                         |       | 0.1 | 1    | μΑ    |  |

| Charge Termination Detection                                       |                            |                                                                                                                                      |       |     |      |       |  |

| Termination Charge Current Programmable Range                      | I <sub>TERM_RANGE</sub>    | $V_{BAT} > V_{BAT\_REG} - V_{RCH}, V_{VBUS} > V_{SLP},$ programmable                                                                 | 50    |     | 400  | mA    |  |

| Termination Current Regulation Setting                             | I <sub>TERM</sub>          | I <sub>TERM</sub> = 100mA, T <sub>J</sub> = +25°C                                                                                    | 35    |     | 190  | mA    |  |

| Bad Adapter Detection                                              |                            |                                                                                                                                      |       |     |      |       |  |

| Input Voltage Lower Limit                                          | $V_{IN(MIN)}$              | Bad adapter detection                                                                                                                | 3.75  | 3.9 | 4.05 | V     |  |

| Hysteresis for V <sub>IN(MIN)</sub>                                | V <sub>IN(MIN)_HYS</sub>   | Input voltage rising                                                                                                                 | 45    | 110 | 175  | mV    |  |

| Current Source to GND                                              | I <sub>BAD_SRC</sub>       | During bad adapter detection                                                                                                         | 15    | 30  | 45   | mA    |  |

| Input Based Dynamic Power Management                               |                            |                                                                                                                                      |       |     |      |       |  |

| Input Voltage DPM Threshold Programmable Range                     | V <sub>IN_DPM_RANGE</sub>  |                                                                                                                                      | 4.2   |     | 4.76 | V     |  |

|                                                                    |                            | V <sub>IN_DPM</sub> = 4.28V, I <sub>CHG</sub> = 200mA                                                                                | -3    |     | 3    |       |  |

| V <sub>IN DPM</sub> Threshold Accuracy                             | V <sub>IN_DPM_ACC</sub>    | V <sub>IN_DPM</sub> = 4.52V, I <sub>CHG</sub> = 200mA                                                                                | -3    |     | 3    | %     |  |

|                                                                    |                            | $V_{IN DPM} = 4.76V, I_{CHG} = 200mA$                                                                                                | -3    |     | 3    |       |  |

NOTE: 1. When plugging in adapter in default mode, the device is in HZ\_MODE if  $V_{BAT} > V_{LOWV}$  (3.65V) and awaits  $I^2C$  commands.

**ELECTRICAL CHARACTERISTICS (continued)**  $(V_{VBUS} = 5V, HZ_MODE = 0, OPA_MODE = 0 (CD_TS = LOW), T_J = -40^{\circ}C to +125^{\circ}C, typical values are at T_A = +25^{\circ}C, unless$ otherwise noted.)

| PARAMETER                                                                                 | SYMBOL                     | CONDITIONS                                                                         | MIN  | TYP   | MAX  | UNITS |  |  |

|-------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------------------------------------|------|-------|------|-------|--|--|

| Input Current Limiting                                                                    |                            |                                                                                    |      |       |      |       |  |  |

| Input Current Limiting Threshold                                                          | I <sub>IN_LIMIT</sub>      | I <sub>IN</sub> = 500mA                                                            | 475  | 500   | 525  | mA    |  |  |

| VREF Bias Regulator                                                                       |                            | ,                                                                                  |      | ı     |      | ı     |  |  |

| Internal Bias Regulator Voltage                                                           | $V_{REF}$                  | $V_{VBUS}$ > UVLO, $I_{VREF}$ = 1mA, $C_{VREF}$ = 1 $\mu$ F                        | 4.75 | 5     | 5.25 | V     |  |  |

| VREF Output Short Current Limit                                                           | I <sub>REF_LMT</sub>       |                                                                                    |      | 30    |      | mA    |  |  |

| Battery Recharge Threshold                                                                | Battery Recharge Threshold |                                                                                    |      |       |      |       |  |  |

| Recharge Threshold Voltage Range                                                          | V <sub>RCH_RANGE</sub>     | Below V <sub>BAT_REG</sub>                                                         | 50   |       | 200  | mV    |  |  |

| Recharge Threshold Voltage                                                                | $V_{RCH}$                  | Below V <sub>BAT_REG</sub> , VRCHG[1:0] = 01                                       |      | 100   |      | mV    |  |  |

| STAT Outputs                                                                              |                            |                                                                                    |      | •     |      | •     |  |  |

| Low-Level Output Saturation Voltage, STAT Pin                                             | V <sub>OL(STAT)</sub>      | 10mA sink current                                                                  |      |       | 0.4  | V     |  |  |

| High-Level Leakage Current for STAT                                                       | I <sub>STAT_LKG</sub>      | Voltage on STAT pin is 5V                                                          |      |       | 1    | μA    |  |  |

| I <sup>2</sup> C Bus Logic Levels and Timing C                                            | haracteristic              | s                                                                                  |      | 1     |      | 1     |  |  |

| Output Low Threshold Level                                                                | V <sub>OL</sub>            | I <sub>O</sub> = 10mA, sink current                                                |      |       | 0.4  | V     |  |  |

| Input Low Threshold Level                                                                 | V <sub>IL</sub>            | V <sub>PULL-UP</sub> = 1.2V, SDA and SCL, I2C_HI_DETC = 0                          |      |       | 0.4  | V     |  |  |

| Input High Threshold Level                                                                | V <sub>IH</sub>            | $V_{PULL-UP}$ = 1.2V, SDA and SCL, I2C_HI_DETC = 1, -40°C < T <sub>J</sub> < +85°C | 0.84 |       |      | V     |  |  |

|                                                                                           |                            | V <sub>PULL-UP</sub> = 1.8V, SDA and SCL, I2C_HI_DETC = 0                          | 1.1  |       |      |       |  |  |

| Input Bias Current                                                                        | I <sub>BIAS</sub>          | V <sub>PULL-UP</sub> = 1.2V, SDA and SCL                                           |      |       | 1    | μA    |  |  |

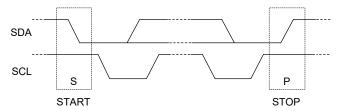

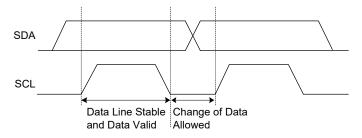

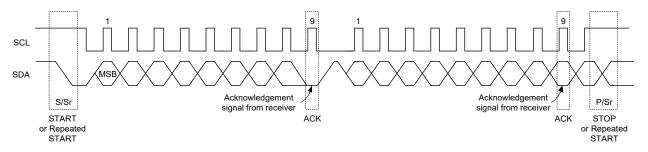

| SCL Clock Frequency                                                                       | f <sub>SCL</sub>           | Range                                                                              | 10   |       | 1000 | kHz   |  |  |

| I <sup>2</sup> C Bus Release Timeout t <sub>I2C_TIMEOUT</sub>                             |                            | When keep low for SCL or SDA                                                       |      | 25    |      | ms    |  |  |

| Battery Detection                                                                         |                            |                                                                                    |      |       |      |       |  |  |

| Battery Detection Current before<br>Charge Done (Sink Current)                            | I <sub>DETECT</sub>        | Begins after termination detected, $V_{BAT} \le V_{BAT\_REG}$                      |      | -0.5  |      | mA    |  |  |

| Sleep Comparator                                                                          |                            |                                                                                    |      |       |      |       |  |  |

| Sleep Mode Entry Threshold,<br>V <sub>VBUS</sub> - V <sub>BAT</sub>                       | $V_{SLP}$                  | 2.3V ≤ V <sub>BAT</sub> ≤ V <sub>BAT_REG</sub> , VBUS falling, internal accuracy   | 15   | 40    | 65   | mV    |  |  |

| Sleep Mode Exit Hysteresis                                                                | V <sub>SLP_HYS</sub>       | 2.3V ≤ V <sub>BAT</sub> ≤ V <sub>BAT_REG</sub> , internal accuracy                 | 120  | 180   | 245  | mV    |  |  |

| Under-Voltage Lockout (UVLO)                                                              |                            |                                                                                    |      | •     |      | •     |  |  |

| V <sub>VBUS</sub> Minimum (as One of the Conditions) to Turn on REGN                      | UVLO                       | VBUS rising - exits UVLO                                                           |      | 3.175 | 3.5  | V     |  |  |

| V <sub>VBUS</sub> Hysteresis (as One of the Conditions) to Turn on REGN                   | UVLO <sub>(HYS)</sub>      | VBUS falling below UVLO - enters UVLO                                              | 20   | 135   |      | mV    |  |  |

| PWM                                                                                       | T                          |                                                                                    |      | 1     |      | 1     |  |  |

| Voltage from BOOT Pin to SW Pin                                                           | $V_{BOOT}$                 | During charge or Boost operation                                                   |      |       | 4    | V     |  |  |

| Internal Top Reverse Blocking<br>MOSFET On-Resistance<br>Internal Top N-Channel Switching | R <sub>Q1</sub>            | I <sub>IN_LIMIT</sub> = 500mA, measured from VBUS to PMID                          |      | 30    |      | mΩ    |  |  |

| MOSFET On-Resistance                                                                      | R <sub>Q2</sub>            | Measured from PMID to SW, $V_{BOOT}$ - $V_{SW}$ = 4V                               |      | 75    |      | mΩ    |  |  |

| Internal Bottom N-Channel MOSFET On-Resistance                                            | R <sub>Q3</sub>            | Measured from SW to PGND                                                           |      | 90    |      | mΩ    |  |  |

| Oscillator Frequency                                                                      | f <sub>osc</sub>           |                                                                                    |      | 1.5   |      | MHz   |  |  |

| Frequency Accuracy                                                                        | f <sub>OSC_ACC</sub>       |                                                                                    | -9.5 |       | 9.5  | %     |  |  |

| Maximum Duty Cycle                                                                        | D <sub>MAX</sub>           |                                                                                    |      | 99.5  |      | %     |  |  |

| Synchronous Mode to<br>Non-Synchronous Mode Transition<br>Current Threshold               | I <sub>SYN_ASYN</sub>      | Low-side MOSFET cycle-by-cycle current sensing                                     |      | 100   |      | mA    |  |  |

**ELECTRICAL CHARACTERISTICS (continued)**  $(V_{VBUS} = 5V, HZ_MODE = 0, OPA_MODE = 0 (CD_TS = LOW), T_J = -40^{\circ}C to +125^{\circ}C, typical values are at T_A = +25^{\circ}C, unless$ otherwise noted.)

| PARAMETER                                                                | SYMBOL                  | CONDITIONS                                                                                                                                                                                            |                                                                  | MIN   | TYP  | MAX   | UNITS                 |  |

|--------------------------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------|------|-------|-----------------------|--|

| Charge Mode Protection                                                   |                         |                                                                                                                                                                                                       |                                                                  |       |      |       |                       |  |

| Input VBUS OVP Threshold Voltage                                         | V <sub>OVP IN USB</sub> | VBUS rising threshold to turn off converter during                                                                                                                                                    | VBUS_OVP = 0                                                     | 6.05  | 6.5  | 6.95  | V                     |  |

| Impat vibee evi Tilleshela veltage                                       | ▲ OAL IN O2R            | charge                                                                                                                                                                                                | VBUS_OVP = 1                                                     | 13.3  | 14   | 14.7  | V                     |  |

| VBAT OVP Threshold Voltage                                               | V <sub>VBAT OVP</sub>   | $V_{\text{BAT}}$ threshold over $V_{\text{BAT\_RE}}$ during charge                                                                                                                                    | <sub>G</sub> to turn off charger                                 | 113.5 | 117  | 120.5 | %V <sub>BAT_REG</sub> |  |

| V <sub>OVP</sub> Hysteresis                                              | ="                      | Lower limit for V <sub>BAT</sub> falling f                                                                                                                                                            | rom above V <sub>BAT_OVP</sub>                                   |       | 12   |       |                       |  |

| Cycle-by-Cycle Current Limit for Charge                                  | I <sub>ICHG_LIMIT</sub> | Charge mode operation                                                                                                                                                                                 |                                                                  |       | 4    |       | Α                     |  |

| Trickle to Fast Charge Threshold                                         | $V_{SHORT}$             | V <sub>BAT</sub> rising                                                                                                                                                                               |                                                                  | 1.95  | 2.1  | 2.25  | V                     |  |

| V <sub>SHORT</sub> Hysteresis                                            | V SHORT                 | V <sub>BAT</sub> falling below V <sub>SHORT</sub>                                                                                                                                                     |                                                                  |       | 100  |       | mV                    |  |

| Trickle Charge Charging Current                                          | I <sub>SHORT</sub>      | V <sub>BAT</sub> ≤ V <sub>SHORT</sub>                                                                                                                                                                 |                                                                  | 15    | 30   | 45    | mA                    |  |

| Boost Mode Operation for VBUS (OP                                        | A_MODE = 1              | , HZ_MODE = 0)                                                                                                                                                                                        |                                                                  |       |      |       |                       |  |

| Boost Output Voltage (to VBUS Pin)                                       | $V_{VBUS\_B}$           | V <sub>BAT</sub> = 3.8V, OTG_VOUT[1                                                                                                                                                                   | :0] = 00                                                         |       | 5.05 |       | V                     |  |

| Boost Output Voltage Accuracy                                            | V <sub>VBUS_B_ACC</sub> | Including line and load reg $V_{VBUS\_B}$ = 5.05V or $V_{VBUS\_B}$                                                                                                                                    |                                                                  | -2.3  |      | 2.3   | %                     |  |

| Maximum Output Current for Boost                                         | I <sub>BO</sub>         | $V_{VBUS_B} = 5.05V, V_{BAT} = 3.8$                                                                                                                                                                   | V                                                                | 945   | 1400 |       | mA                    |  |

| Cycle-by-Cycle Current Limit for Boost                                   | I <sub>BLIMIT</sub>     | $V_{VBUS\_B} = 5.05V, V_{BAT} = 3.8$                                                                                                                                                                  | V                                                                |       | 2.9  |       | Α                     |  |

| Over-Voltage Protection Threshold for Boost (VBUS Pin)                   | $V_{BUSOVP}$            | Threshold over VBUS to tu<br>during boosting                                                                                                                                                          | ırn off converter                                                | 5.7   | 6    | 6.3   | V                     |  |

| V <sub>BUSOVP</sub> Hysteresis                                           |                         | V <sub>VBUS</sub> falling from above V <sub>E</sub>                                                                                                                                                   | BUSOVP                                                           |       | 100  |       | mV                    |  |

| Maximum Battery Voltage for Boost (BAT Pin)                              | $V_{BATMAX}$            | V <sub>BAT</sub> rising edge during boosting                                                                                                                                                          |                                                                  | 4.65  | 4.9  | 5.15  | V                     |  |

| V <sub>BATMAX</sub> Hysteresis                                           |                         | V <sub>BAT</sub> falling from above V <sub>BATMAX</sub>                                                                                                                                               |                                                                  |       | 200  |       | mV                    |  |

| Minimum Battery Voltage for Boost                                        | V <sub>BATMIN</sub>     | During boosting                                                                                                                                                                                       |                                                                  |       | 2.4  |       | V                     |  |

| (BAT Pin)                                                                | V BAIMIN                | Before Boost starts                                                                                                                                                                                   |                                                                  |       | 2.8  | 3     | •                     |  |

| Boost Output Resistance at<br>High-Impedance Mode<br>(from VBUS to PGND) | R <sub>VBUS_LKG</sub>   | CD_TS = HIGH or HZ_MO<br>0°C < T <sub>J</sub> < +85°C                                                                                                                                                 | DE = 1,                                                          | 200   |      |       | kΩ                    |  |

| Protection                                                               |                         |                                                                                                                                                                                                       |                                                                  |       |      |       |                       |  |

| Thermal Trip                                                             | T <sub>SHTDWN</sub>     |                                                                                                                                                                                                       |                                                                  |       | 165  |       | °C                    |  |

| Thermal Hysteresis                                                       | T <sub>SHTDWN_HYS</sub> |                                                                                                                                                                                                       |                                                                  |       | 10   |       | °C                    |  |

| Thermal Regulation Threshold                                             | $T_CF$                  | Charge current begins to re                                                                                                                                                                           | educe                                                            |       | 120  |       | °C                    |  |

| JEITA Thermistor Comparator (Buck                                        | Mode)                   |                                                                                                                                                                                                       |                                                                  |       |      |       |                       |  |

| T1 (0°C) Threshold Voltage                                               | $V_{T1}$                | Charge suspended if temp the threshold, as percentage                                                                                                                                                 |                                                                  |       | 73.2 |       | %                     |  |

| at CD_TS Pin                                                             |                         | Falling threshold, as perce                                                                                                                                                                           | ntage of V <sub>VREF</sub>                                       |       | 71.2 |       | - /0                  |  |

| T2 (10°C) Threshold Voltage                                              | $V_{T2}$                | Charge sets to I <sub>CHG</sub> /10 and as percentage of V <sub>VREF</sub>                                                                                                                            | V <sub>BAT_REG</sub> - 100mV,                                    |       | 68.1 |       | %                     |  |

| at CD_TS Pin                                                             |                         | Falling threshold, as perce                                                                                                                                                                           | ntage of V <sub>VREF</sub>                                       |       | 66.7 |       |                       |  |

| T3 (45°C) Threshold Voltage                                              | $V_{T3}$                | Charge sets to normal I <sub>CHG</sub> above the threshold, as pe                                                                                                                                     |                                                                  |       | 45.8 |       | %                     |  |

| at CD_TS Pin                                                             |                         | Falling threshold, as perce                                                                                                                                                                           | ntage of V <sub>VREF</sub>                                       |       | 44.5 |       | 7                     |  |

|                                                                          |                         | Charge sets to normal I <sub>CHG</sub> 100mV if T3 < T <t4, as="" pe<="" td=""><td>/10 and V<sub>BAT_REG</sub> -<br/>ercentage of V<sub>VREF</sub></td><td></td><td>35.4</td><td></td><td></td></t4,> | /10 and V <sub>BAT_REG</sub> -<br>ercentage of V <sub>VREF</sub> |       | 35.4 |       |                       |  |

| T4 (60°C) Threshold Voltage<br>at CD_TS Pin                              | V <sub>T4</sub>         | Falling Threshold, charge stemperature T is below the as percentage of V <sub>VREF</sub>                                                                                                              |                                                                  |       | 34.0 |       | %                     |  |

**ELECTRICAL CHARACTERISTICS (continued)**  $(V_{VBUS} = 5V, HZ_{MODE} = 0, OPA_{MODE} = 0 (CD_{TS} = LOW), T_{J} = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ typical values are at } T_{A} = +25^{\circ}C, \text{ unless}$ otherwise noted.)

| PARAMETER                                                             | SYMBOL                                         | CONDITIONS                                                 | MIN | TYP  | MAX | UNITS |  |  |

|-----------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------------|-----|------|-----|-------|--|--|

| Cold or Hot Thermistor Comparator                                     | Cold or Hot Thermistor Comparator (Boost Mode) |                                                            |     |      |     |       |  |  |

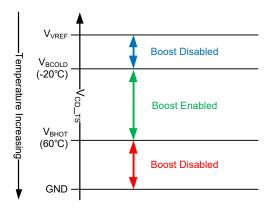

| Cold Temperature Threshold (CD_TS Pin Voltage Rising Threshold)       | $V_{BCOLD}$                                    | As percentage of V <sub>VREF</sub> (approx20°C w/ 103AT)   |     | 80   |     | %     |  |  |

| CD_TS Voltage Falling (Exit from Cold Range to Cool)                  | • BCOLD                                        | As percentage of V <sub>VREF</sub>                         |     | 79   |     | %     |  |  |

| Hot Temperature Threshold<br>(CD_TS Pin Voltage Falling<br>Threshold) | $V_{BHOT}$                                     | As percentage of V <sub>VREF</sub> (approx. 60°C w/ 103AT) |     | 31.2 |     | %     |  |  |

| CD_TS Voltage Rising<br>(Exit Hot Range to Warm)                      |                                                | As percentage of V <sub>VREF</sub>                         |     | 34.5 |     | %     |  |  |

## **TIMING REQUIREMENTS**

| PARAMETER                                                    | SYMBOL                   | CONDITIONS                                                                                                                           | MIN | TYP | MAX | UNITS |  |  |

|--------------------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|--|--|

| Weak Battery Detection                                       | Weak Battery Detection   |                                                                                                                                      |     |     |     |       |  |  |

| Deglitch Time for Weak Battery<br>Threshold                  | t <sub>WEAK_DGL</sub>    | Battery detection function: when $V_{BAT} < V_{BAT\_REG} - V_{RCH}$ during $t_{WEAK\_DGL}$ , a 128 $\mu$ s pulse is sent to STAT pin |     | 100 |     | ms    |  |  |

| Charge Termination Detection                                 |                          |                                                                                                                                      |     |     |     |       |  |  |

| Deglitch Time for Charge Termination                         | t <sub>TERM_DGL</sub>    | TERM_DGL[1:0] = 10 (32ms)                                                                                                            |     | 30  |     | ms    |  |  |

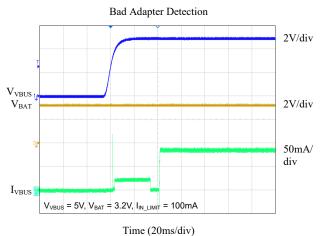

| Bad Adapter Detection                                        |                          |                                                                                                                                      |     |     |     |       |  |  |

| Deglitch Time for VBUS Rising above $V_{\text{IN(MIN)}}$     | t <sub>VBUS_R_DGL</sub>  |                                                                                                                                      |     | 30  |     | ms    |  |  |

| t <sub>INT</sub> Detection Interval                          | $t_{INT}$                | Input power source detection                                                                                                         |     | 2   |     | s     |  |  |

| Battery Recharge Threshold                                   |                          |                                                                                                                                      |     |     |     |       |  |  |

| Deglitch Time                                                | t <sub>RECH_DGL</sub>    |                                                                                                                                      |     | 120 |     | ms    |  |  |

| Battery Detection                                            |                          |                                                                                                                                      |     |     |     |       |  |  |

| Battery Detection Time                                       | t <sub>DETECT</sub>      |                                                                                                                                      |     | 224 |     | ms    |  |  |

| Sleep Comparator                                             |                          |                                                                                                                                      |     |     |     |       |  |  |

| Deglitch Time for VBUS Rising above $V_{SLP} + V_{SLP}$ EXIT | t <sub>SLEEP_R_DGL</sub> |                                                                                                                                      |     | 30  |     | ms    |  |  |

| Charge Safety Timer                                          |                          |                                                                                                                                      |     |     |     |       |  |  |

| Charge Safety Timer                                          | t <sub>CHG_SAFE</sub>    |                                                                                                                                      | 8   | 10  | 12  | h     |  |  |

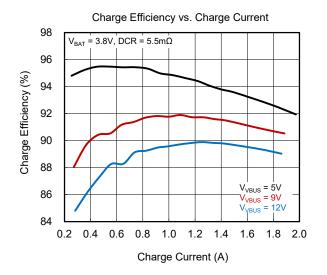

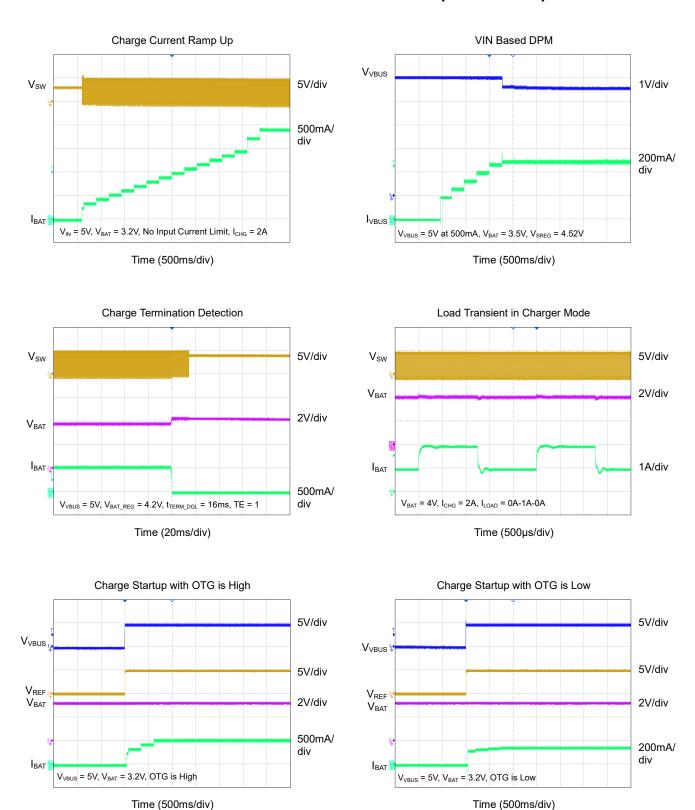

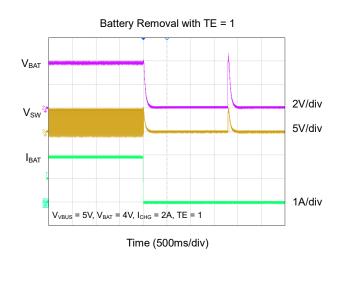

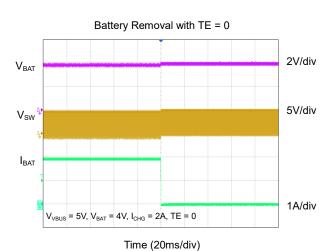

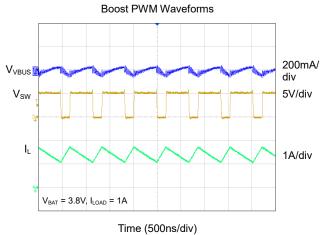

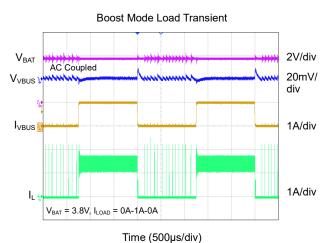

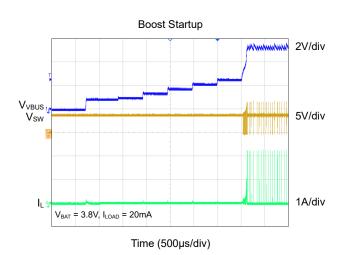

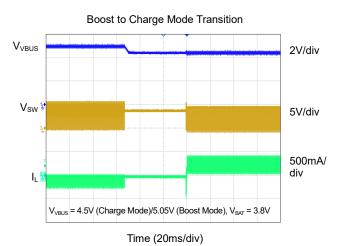

### TYPICAL PERFORMANCE CHARACTERISTICS

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

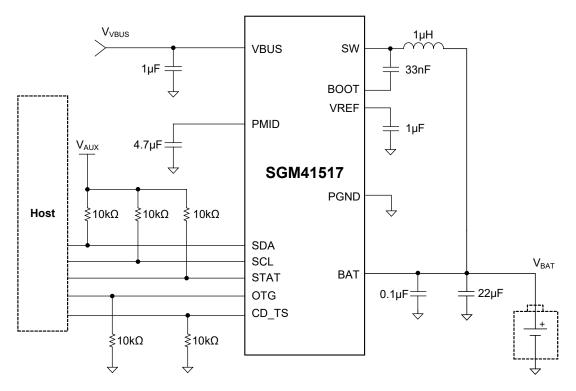

## TYPICAL APPLICATION CIRCUIT

NOTE:  $V_{VBUS}$  = 5V,  $I_{CHG}$  = 2000mA,  $V_{BAT}$  = 3.5V to 4.6V (adjustable).

Figure 1. Typical Application Circuit

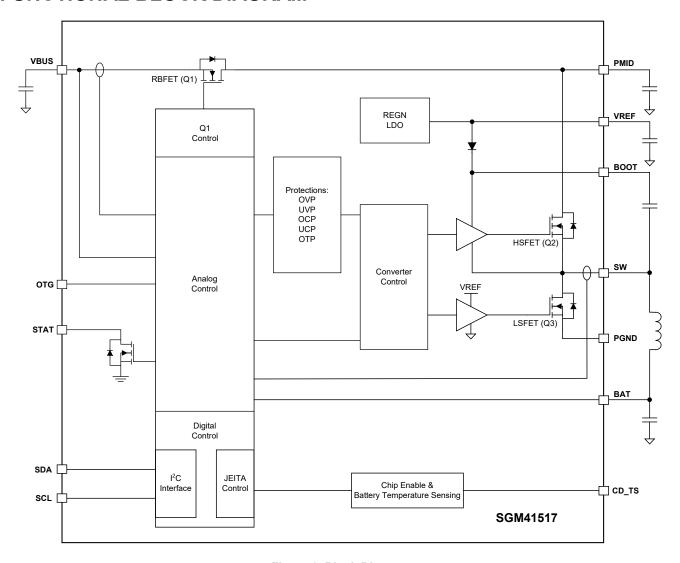

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. Block Diagram

#### **DETAILED DESCRIPTION**

#### **Overview**

For power sources with limited current, such as USB hosts or hubs, efficient converters are crucial for fully use input power capacity to quickly charge batteries. Due to the high-efficiency of switch-mode chargers over a wide input and battery voltage range compared with linear chargers, the switch-mode chargers is a good choice for high-speed charging and better thermal management.

The SGM41517 is a highly integrated synchronous switch-mode charger, which integrates FETs and small external components. The SGM41517 is suitable for portable applications powered by single battery lithium-ion or lithium-polymer battery packs. In addition, the SGM41517 also has bidirectional operation to achieve the Boost function supported by USB OTG.

The SGM41517 has three operating modes: charging mode, Boost mode, and high-impedance mode. In charging mode, the IC supports precision lithium-ion or lithium-polymer charging systems for single battery applications. In Boost mode, the IC boosts the battery voltage to VBUS to supply power to the connected OTG devices. In high-impedance mode, the IC stops charging or boosting and operates in a mode where the current from the VBUS or battery is very low, effectively reducing the power consumption of portable devices in standby mode. Through I<sup>2</sup>C communication with the host, i.e. "host" control/mode, the IC achieves smooth transition between different operating modes. Even if there is no available I<sup>2</sup>C communication, the IC will start in default mode. During default mode operation, the charger will still charge the battery, but use the default value of registers.

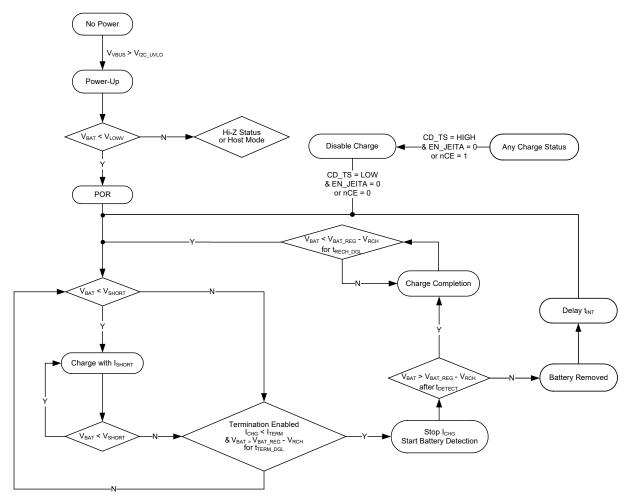

#### **Operational Flow Chart**

Figure 3. Operational Flow Chart of SGM41517 in Charge Mode

## Input Voltage Protection Input Over-Voltage Protection

The IC has built-in input over-voltage protection to protect equipment and other components from damage in the event of high input voltage (voltage from VBUS to PGND). When VBUS OVP is detected, the device turns off the PWM converter and RBFET Q1, sets the fault status bit, and sends a 128 $\mu$ s pulse to the STAT pin. Once V<sub>VBUS</sub> drops below the input over-voltage exit threshold, the fault will be cleared and the charging process will resume.

#### **Bad Adapter Detection**

When the power-on reset (POR) happens at VBUS pin, the IC performs the bad adapter detection by applying a about 30mA current sink to VBUS. If VBUS is higher than  $V_{\text{IN}(\text{MIN})}$  for 30ms, the adapter is good and the charging process is started. Otherwise, if VBUS drops below  $V_{\text{IN}(\text{MIN})}$ , a bad adapter is found, and the IC disables the current sink, sends a 128µs low pulse at the STAT pin, and sets the bad adapter flag (FAULT[2:0] = 011 in register REG0x00). After the  $t_{\text{INT}}$  (2s TYP) delay, the IC restarts the adapter detection process again.

#### Sleep Mode

When the VBUS pin voltage falls below the sleep mode entry threshold ( $V_{BAT}$  +  $V_{SLP}$ ) and VBUS is higher than the bad adapter detection threshold ( $V_{IN(MIN)}$ ), the SGM41517 enters the low power sleep mode. When adapter is not present, there is no leakage current to from BAT to VBUS. In the sleep mode, both the RBFET Q1 and PWM are turned off.

# Input Voltage Based DPM (Special Charger Voltage Threshold)

In the charging process, if the input power source cannot provide the programmed charging current, the VBUS voltage will drop. Once the VBUS decrease to  $V_{\text{IN\_DPM}}$  (default 4.52V), the chip begins to decrease the charge current for preventing any further drop of VBUS. The charge current is lower than the set value if the SGM41517 enters this mode. The feature makes the IC has the maximum compatibility with different adapters.

## **Battery Protection Battery Over-Voltage Protection**

The IC integrates a built-in over-voltage protection to protect the device and other components from the over-voltage damage when the battery is suddenly removed. When an over-voltage condition is found, the PWM converter is turned off by the device, the fault status bits can be set, and a fault pulse is sent out to the STAT pin. Once  $V_{BAT}$  drops to the battery over-voltage falling threshold, the fault is cleared and charge process is restarted again.

#### **Battery Short Protection and Charge Timeout**

In the normal charging process, if the battery voltage is lower than the short-circuit threshold  $V_{\text{SHORT}}$ , the charger charging the battery with  $I_{\text{SHORT}}$ .

When a charge cycle is started, the internal 10 hours safety timer starts to count. If the charging is not terminated in 10 hours, device will stop the PWM and send 128µs pulse at the STAT pin to notify the AP. Plug out VBUS or set the CD\_TS pin to high or set the TMR\_RST bit or nCE bit can reset the safety timer.

#### **Battery Detection in Host Mode**

For the applications that needs to removable battery pack, once the termination function is enabled, the IC provides a battery presence detection method to detect whether the battery packs is inserted or removed.

During the normal charging process controlled, once the BAT voltage is over the battery recharge threshold  $V_{BAT\_REG}$  -  $V_{RCH}$ , and the termination of charging current is detected, the IC will turn off PWM charging and enable the discharge current  $I_{DETECT}$  for  $I_{DETECT}$  (224ms, TYP) and check the battery voltage. If the battery voltage remains above the recharge threshold after  $I_{DETECT}$ , it indicates that the battery is present. On the contrary, if the battery voltage is lower than the battery recharge threshold during  $I_{WEAK\_DGL}$  (100ms TYP), the battery does not exist, the FAULT[2:0] bits are set to 111 and a 128 $\mu$ s pulse is sent to STAT pin. In this case, charging will resume after a delay in  $I_{INT}$ . This function ensures that the charging parameters are reset when replacing the battery.

#### **Default Mode**

The SGM41517 stays in default mode until  $I^2C$  communication starts. When the host sends a valid  $I^2C$  write command to the SGM41517, the IC will enter host mode automatically.

#### **USB Friendly Power-Up**

The default control bits set the charging current and regulation voltage low enough to comply with USB spec and avoid over-charging any of the Li-lon chemistries, while the host has lost communication. The input current limiting is described as follow.

#### Input Current Limiting at Power-Up

The SGM41517 integrates the input current sensing circuit and the control loop internally. In default mode, the OTG pin voltage level sets the input current limit to 100mA for low-level and 500mA for high-level. In host mode, the input current limit is set by the programmed control bits in the register REG0x01.

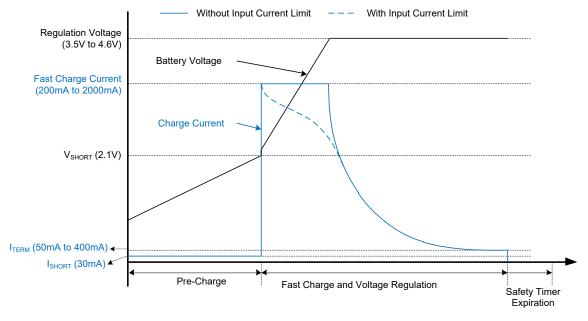

#### Device Functional Modes Charge Mode Operation Charge Profile

Once a good battery with a voltage lower than the charging threshold is inserted and a good adapter is connected, the SGM41517 will enter charging mode. In charging mode, the device has five control loops to regulate input voltage, input current, charging current, charging voltage, and chip junction temperature. During charging, all five control loops are enabled, one of which is dominant. This IC can charge the Li-lon or Li-polymer charging systems precisely. Figure 4 shows a typical charging curve without an input current regulation circuit. This is the traditional CC/CV charging curve, and Figure 4 (marked with dashed lines) also shows a typical charging curve when the input current limiting circuit dominates in constant current mode. In this case, the charging current is higher than the input current, so the charging process is faster than a linear charger. The input voltage limit, input current limit, charging current, termination current, and charging voltage can be programmed by the I<sup>2</sup>C interface.

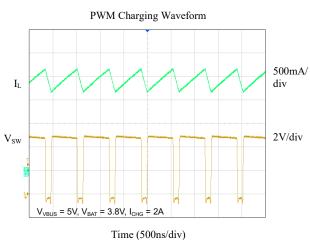

#### **PWM Controller in Charge Mode**

The SGM41517 integrates a fixed 1.5MHz or 500kHz frequency voltage-mode controller to regulate charge current

or voltage. This controller improves the line transient response, and simplifies the compensation network used for both continuous and discontinuous current mode operation. The elaborate designed controller has enough phase margins for stable operation even use small ceramic capacitors with low ESR.

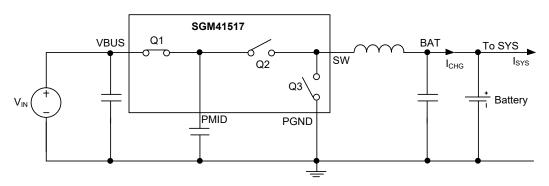

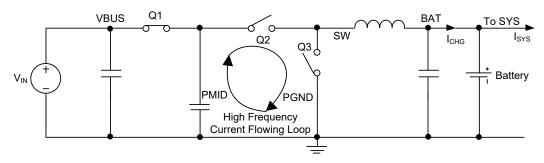

The IC has integrates three N-FETs: the reverse blocking N-FET (Q1), the high-side N-FET (Q2), and the low-side N-FET (Q3). The reverse blocking N-FET (Q1) prevents the battery discharge when  $V_{VBUS}$  is lower than  $V_{BAT}$ . The high-side N-FET (Q2) is the switching switch. A charge pump circuit is used to turn on the reverse blocking N-FET (Q1), and a bootstrap circuit with an external bootstrap capacitor is used to supply the gate drive circuit for the high-side N-FET (Q2).

The cycle-by-cycle current limit is done by sensing the current through the FETs Q2 and Q3. The limit threshold for Q2 is set to a nominal 4A peak current. The low-side N-FET (Q3) also has the zero crossing detection (ZCD) function, which determines whether the PWM controller will operate in synchronous or non-synchronous mode. If the current of the low-side FET is lower than 100mA, the low-side N-channel FET (Q3) is turned off to prevent the battery from discharging, else synchronous operation is used to minimize power loss.

Figure 4. Typical Charging Profile for without Input Current Limit and with Input Current Limit

#### **Battery Charging Process**

At the beginning of pre-charging, when the battery voltage is lower than  $V_{SHORT}$ , the IC charges the battery with short-circuit current  $I_{SHORT}$ . When the battery voltage is higher than  $V_{SHORT}$  and lower than  $V_{BAT\_REG}$ , the charging current ramp rises to the fast charging current  $I_{CHG}$  or a current decided by input current limit. Controlling the set value of fast charging current can minimize current and voltage overshoot during charging period. The input current limit and the fast charging current  $I_{CHG}$  can be set by host. Once the battery voltage reaches the regulated voltage  $V_{BAT\_REG}$ , the charging current will gradually decrease, as shown in Figure 4. The IC monitors the battery packs voltage by sensing the voltage between the BAT and PGND pin. In host mode, the voltage can be adjusted (3.5V to 4.6V) and programmed through by  $I^2$ C interface.

If termination function is enabled, a charge cycle is terminated when the battery voltage is higher than the recharge threshold and the charge current falls below the programmed termination current. TE bit is termination control bit and can be set to 0 to disable termination before it happens.

When one of the following conditions is detected, a new charge cycle is restarted:

- ullet The battery voltage falls below the  $V_{BAT\_REG}$   $V_{RCH}$  threshold.

- $\bullet$  VBUS power-on reset (POR), if the battery voltage is below the  $V_{\text{LOWV}}$  threshold.

- nCE bit is toggled or RESET bit is set (host controlled).

- CD\_TS pin is toggled from high to low (host controlled).

#### **Thermal Regulation and Protection**

For preventing the chip from overheating during charging, the IC monitors the junction temperature  $T_{\rm J}$  of the die and gradually reduces the charging current when  $T_{\rm J}$  reaches the thermal regulation threshold  $T_{\rm CF}.$  When the junction temperature rises to about 10°C above  $T_{\rm CF},$  the charging current drops to zero. Whenever  $T_{\rm J}$  exceeds  $T_{\rm SHTDWN},$  the IC will stop charging and enter thermal shutdown mode. In the status, PWM is turned off and all timers are frozen. When  $T_{\rm J}$  drops to about 10°C below  $T_{\rm SHTDWN},$  charging resumes.

#### **Status Outputs Pin (STAT)**

The STAT pin is used to indicate the IC status. When EN\_STAT bit in control register (REG0x00) is set to 1, the STAT is pulled to low-level during charging. In the other conditions, the STAT pin is used as a high-impedance (open-drain) output. When in the fault conditions, a 128µs pulse is sent out to notify the host. Charging state is indicated with the STAT pin as explained in Table 1. The role of the STAT pin is to drive an LED indicator or send an interrupt to the host processor.

Table 1. STAT Pin Function

| Charging State                                                                                                                              | STAT Indicator |

|---------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Charge in progress and EN_STAT = 1                                                                                                          | Low            |

| Other normal conditions                                                                                                                     | Open-Drain     |

| Charge mode faults: Timer fault, sleep mode,<br>VBUS or battery over-voltage, poor input source,<br>VBUS UVLO, no battery, thermal shutdown | 128µs Pulse    |

| Boost mode faults: Timer fault, over load, VBUS or battery over-voltage, low battery voltage, thermal shutdown                              | 128µs Pulse    |

#### Control Bits in Charge Mode nCE Bit (Charge Mode)

The nCE bit in the control register is used to disable or enable the charge process. 0 on this bit enables the charge and 1 disables the charge.

#### **RESET Bit**

The RESET bit of the control register is used to reset all charge parameters. When the RESET bit is set to 1, all charge parameters will be reset to default values except the safety limit register, and the RESET bit is automatically cleared to 0 once reset action is done. This is designed to reset the charge parameters before the charge starts, it is not recommended to set the RESET bit while charging or boosting are in on-going.

#### **OPA MODE Bit**

The OPA\_MODE bit is used as the operation mode control bit. When OPA\_MODE = 0 and HZ\_MODE = 0, the IC operates in charge mode, and when OPA\_MODE = 1 and HZ\_MODE = 0, the IC operates in Boost mode. Table 2 shows the detailed operation mode function.

**Table 2. Operation Mode Function**

| OPA_MODE | HZ_MODE | Operation Mode                                                                                                      |

|----------|---------|---------------------------------------------------------------------------------------------------------------------|

| 0        | 0       | Charge mode (no fault) Charge configure (fault, V <sub>VBUS</sub> > UVLO) High-impedance (V <sub>VBUS</sub> < UVLO) |

| 1        | 0       | Boost mode (no faults) Any fault enters the charge configure mode.                                                  |

| Х        | 1       | High-impedance                                                                                                      |

#### **Control Pins in Charge Mode**

#### CD\_TS Pin (Charge Disable or JEITA Related Function)

In the default status, the CD\_TS pin is used to enable or disable the charging process. When the CD\_TS pin is set to low, the charge is enabled. When the CD\_TS pin is set to high, the charge is disabled and the charger goes to high-impedance (Hi-Z) mode.

When EN\_JEITA bit is set to 1, CD\_TS pin can be used for temperature qualification (support JEITA guideline).

#### **Temperature Qualification**

The charging current and voltage of the battery must be limited when battery is cold or hot. A thermistor input for battery temperature monitoring is included in the device that can protect the battery based on JEITA guidelines.

#### **Compliance with JEITA Guideline**

JEITA guideline (April 20, 2007 release) is implemented in the device for safe charging of the Li-lon battery. JEITA highlights the considerations and limits that should be considered for charging at cold or hot battery temperatures. High charge current and voltage must be avoided outside the normal operating temperatures (typically 0°C and 60°C). This functionality can be disabled if not needed. Four temperature levels are defined by JEITA from T1 (minimum) to T4 (maximum). Outside this range, charging should be stopped. The corresponding voltages sensed by NTC are named  $V_{\rm T1}$  to  $V_{\rm T4}$ . Due to the sensor negative resistance, a higher temperature results in a lower voltage on CD\_TS pin. The battery cool range is between T1 and T2, and the warm range is between T3 and T4. Charge must be limited in the cool and warm ranges.

One of the conditions for starting a charge cycle is having the CD\_TS voltage within  $V_{T1}$  to  $V_{T4}$  window limits. If during the charge, battery gets too cold or too hot and CD\_TS voltage exceeds the T1 - T4 limits, charging is suspended (zero charge current) and the controller waits for the battery temperature to come back within the T1 to T4 window.

JEITA recommends reducing charge current to 1/2 of fast charging current or lower at cool temperatures (T1 - T2). For warmer temperature (within T3 - T4 range), charge voltage is recommended to be kept below  $V_{BAT\_REG}$  - 100mV.

The SGM41517 exceeds the JEITA requirement by its flexible charge parameter settings. At warm temperature range (T3 - T4), the charge voltage is set to the lower of  $V_{BAT\_REG}$  - 100mV when JEITA\_VSET\_H = 0, the charge voltage is set to  $V_{BAT\_REG}$  when JEITA\_VSET\_H = 1, and the charge current can be reduced down to 0%, 10% of fast charging current by the JEITA\_ISET\_H bit. At cool temperatures (T1 - T2), the current setting can be reduced down to 0% or 10% of fast

charging current selectable by the JEITA\_ISET\_L bit, and the charge voltage is set to  $V_{\text{REG}}$  - 100mV.

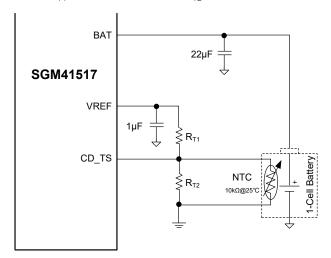

A 103AT-2 type thermistor is recommended for use with the SGM41517. Other thermistors may be used and bias network (see Figure 5) can be calculated based on the following equations:

$$R_{T2} = \frac{R_{THCOLD} \times R_{THHOT} \times \left(\frac{1}{V_{T1}} - \frac{1}{V_{T4}}\right)}{R_{THHOT} \times \left(\frac{1}{V_{T4}} - 1\right) - R_{THCOLD} \times \left(\frac{1}{V_{T1}} - 1\right)}$$

(1)

$$R_{T1} = \frac{\left(\frac{1}{V_{T1}} - 1\right)}{\left(\frac{1}{R_{T2}}\right) + \left(\frac{1}{R_{THCOLD}}\right)}$$

(2)

Where,  $V_{T1}$  and  $V_{T4}$  are  $T_{COLD}$  and  $T_{HOT}$  thresholds voltage on CD\_TS pin as percentage to  $V_{VREF}$ ,  $R_{THCOLD}$  and  $R_{THHOT}$  are thermistor resistances ( $R_{TH}$ ) at desired T1 (Cold) and T4 (Hot) temperatures. Select  $T_{COLD}=0^{\circ}C$  and  $T_{HOT}=60^{\circ}C$  for Li-Ion or Li-polymer batteries. For a 103AT-2 type thermistor  $R_{THCOLD}=27.28k\Omega$  and  $R_{THHOT}=3.02k\Omega$ , the calculation results are:  $R_{T1}=5.32k\Omega$  and  $R_{T2}=31.09k\Omega$ . The standard value of  $R_{T1}$  is  $5.23k\Omega$  and that of  $R_{T2}$  is  $30.9k\Omega$ .

Figure 5. Battery Thermistor Connection and Bias Network (EN\_JEITA = 1)

Table 3. Temperature Related Charging Control (EN\_JEITA = 1)