# SGM51620R

## 4-Channel, 2kSPS, Low-Power, 16-Bit ADC with Integrated PGA and Reference

### GENERAL DESCRIPTION

The SGM51620R is a precise 16-bit analog-to-digital converter (ADC) designed to minimize system costs and component count in applications involving the measurement of small sensor signals. It features four single-ended inputs or two differential inputs through a versatile input multiplexer (MUX), a low-noise programmable gain amplifier (PGA), two programmable excitation current sources, a voltage reference, an oscillator, a low-side switch, and a detailed temperature sensor.

The SGM51620R is capable of achieving conversions at data rates up to 2000 samples per second (SPS) with single-cycle settling. The device's digital filter operates at 20SPS, effectively rejecting 50Hz and 60Hz frequencies in noisy industrial environments. The internal PGA provides amplification levels up to 128V/V, making the SGM51620R suitable for measuring delicate sensor signals such as resistance temperature detectors (RTDs), thermocouples, thermistors, and resistive bridge sensors. The device supports the measurement of pseudo-differential or fully-differential signals when the PGA is used. Alternatively, it can be configured to bypass the internal PGA while still offering high input impedance and amplification levels up to 4V/V, facilitating single-ended measurements.

In duty-cycle mode with the PGA deactivated, the power consumption drops to a minimal 175 $\mu$ A.

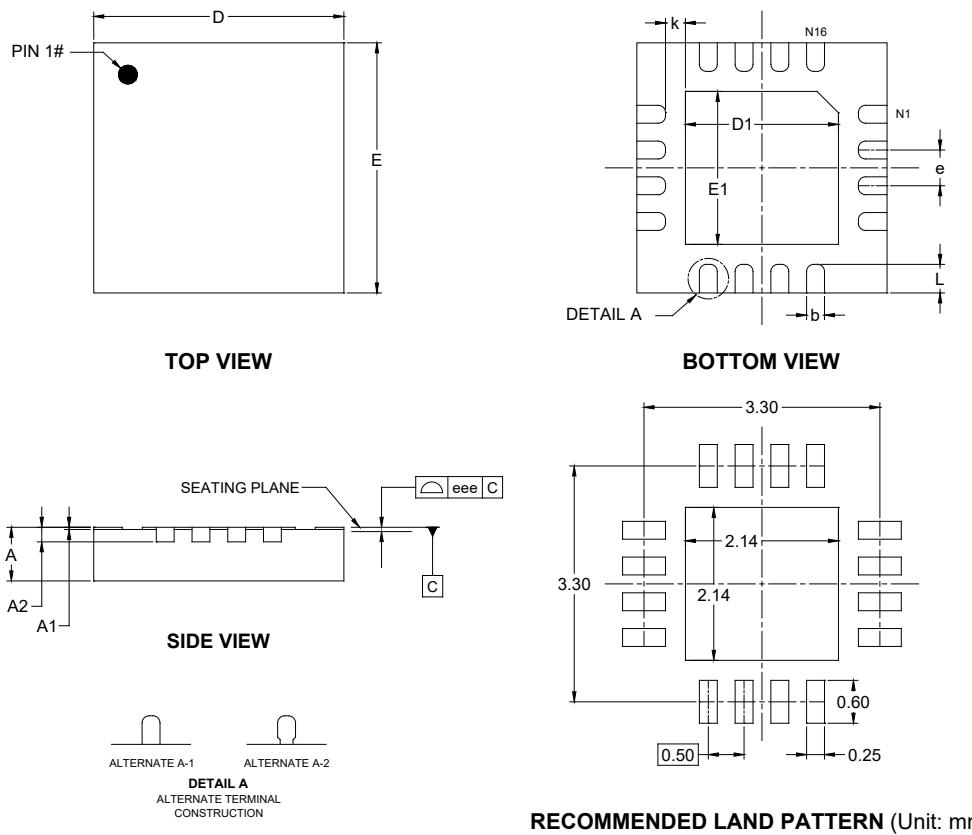

The SGM51620R is available in Green TSSOP-16 and TQFN-3.5 $\times$ 3.5-16L packages, and it is suitable for an extended temperature range from -40°C to +125°C.

### FEATURES

- **Wide Supply Voltage Range: 2.3V to 5.5V**

- **4 Single-Ended or 2 Differential Inputs**

- **Programmable Gain: 1V/V to 128V/V**

- **Programmable Data Rates: Up to 2kSPS**

- **Low Current Consumption:**

As Low as 175 $\mu$ A (TYP) in Duty-Cycle Mode

- **Effective Resolution: Up to 16 Bits**

- **Simultaneous 50Hz and 60Hz Rejection at 20SPS with Single-Cycle Settling Digital Filter**

- **Dual Matched Programmable Current Sources: 50 $\mu$ A to 1.5mA**

- **SPI-Compatible Interface (Mode 1)**

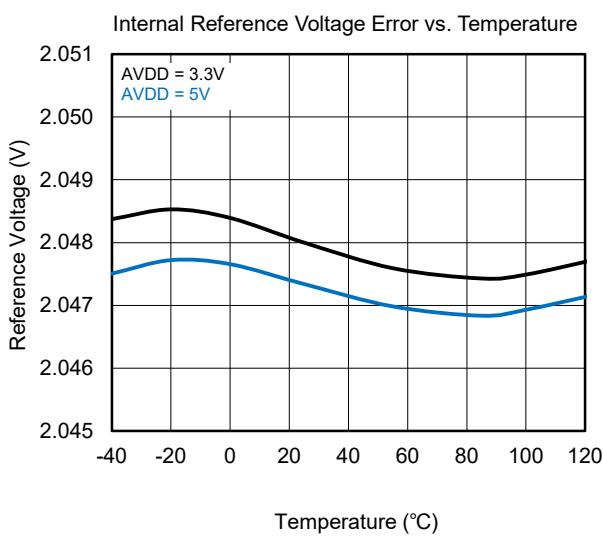

- **Internal 2.048V Reference Drift: 5ppm/°C (TYP)**

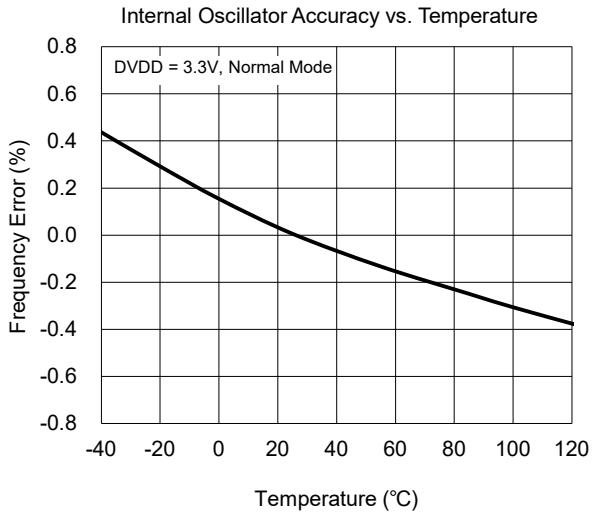

- **Internal  $\pm 0.15\%$  (TYP) Accurate Oscillator**

- **Internal Temperature Sensor Accuracy:  $\pm 0.9^\circ\text{C}$  (TYP)**

- **Available in Green TSSOP-16 and TQFN-3.5 $\times$ 3.5-16L Packages**

### APPLICATIONS

- Acquisitions for Temperature Sensor

- Thermistors

- Thermocouples

- Resistance Temperature Detectors (RTDs)

- Acquisitions for Resistive Bridge Sensors

- Weigh Scales Sensors

- Pressure Sensors

- Strain Gauges Sensors

- Factory Automation

- Process Control

- Portable Devices

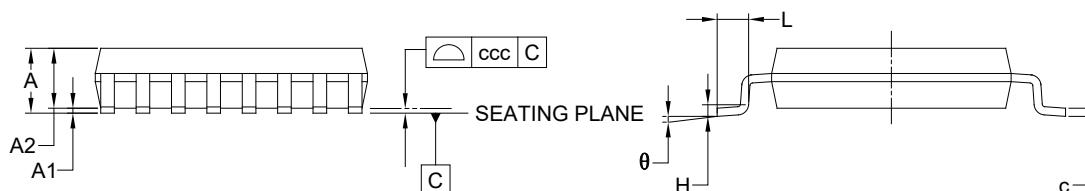

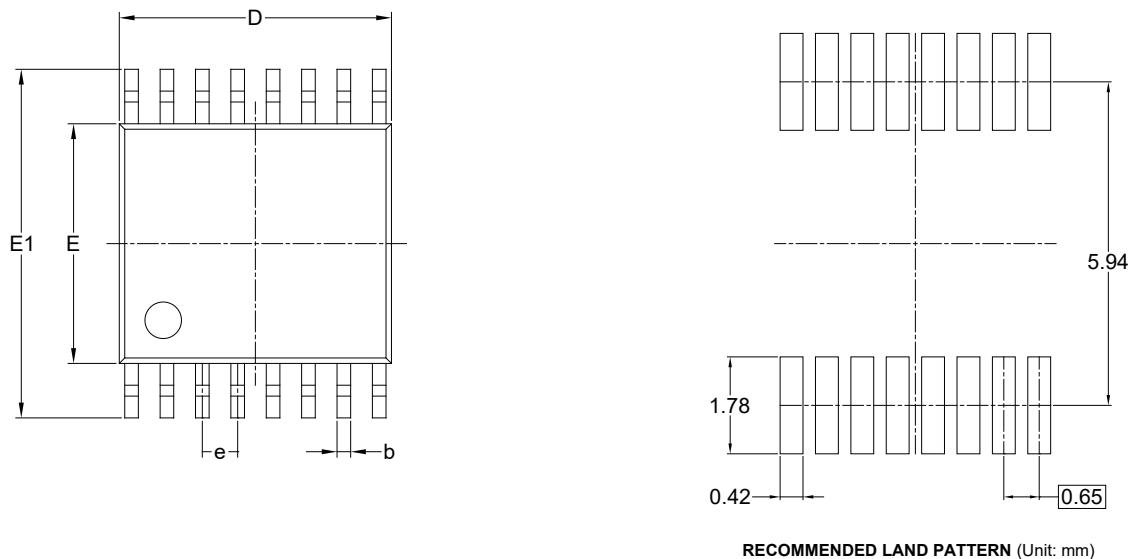

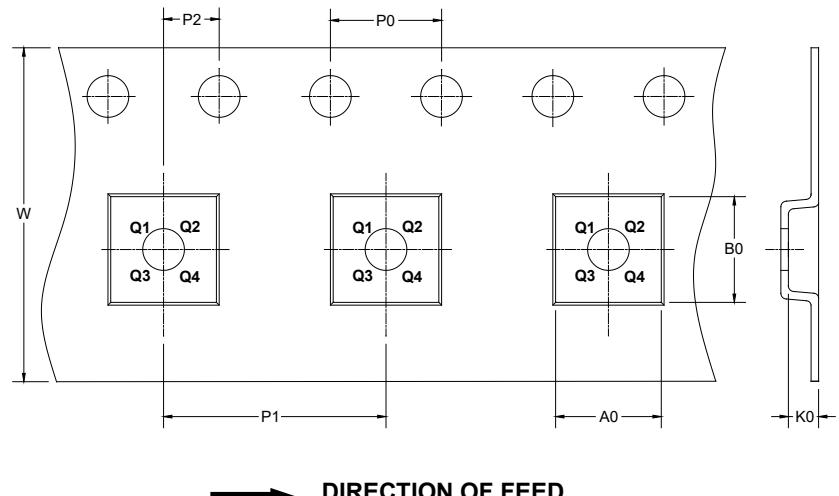

**PACKAGE/ORDERING INFORMATION**

| MODEL     | PACKAGE DESCRIPTION | SPECIFIED TEMPERATURE RANGE | ORDERING NUMBER      | PACKAGE MARKING           | PACKING OPTION      |

|-----------|---------------------|-----------------------------|----------------------|---------------------------|---------------------|

| SGM51620R | TSSOP-16            | -40°C to +125°C             | SGM51620RXTS16G/TR   | SGM163<br>XTS16<br>XXXXX  | Tape and Reel, 4000 |

|           |                     |                             | SGM51620RXTS16SG/TR  | SGM163<br>XTS16<br>XXXXX  | Tape and Reel, 500  |

|           | TQFN-3.5x3.5-16L    | -40°C to +125°C             | SGM51620RXTVI16G/TR  | 51620R<br>XTVI16<br>XXXXX | Tape and Reel, 4000 |

|           |                     |                             | SGM51620RXTVI16SG/TR | 51620R<br>XTVI16<br>XXXXX | Tape and Reel, 500  |

**MARKING INFORMATION**

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

**XXXXX**

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

## ABSOLUTE MAXIMUM RATINGS

|                                                                                     |                                |

|-------------------------------------------------------------------------------------|--------------------------------|

| Power Supply Voltage Range                                                          |                                |

| AVDD to AVSS .....                                                                  | -0.3V to 7V                    |

| DVDD to DGND .....                                                                  | -0.3V to 7V                    |

| AVSS to DGND .....                                                                  | -2.8V to 0.3V                  |

| Analog Input Voltage Range (AIN0/REFP1, AIN1, AIN2, AIN3/REFN1, REFP0, REFN0) ..... | (AVSS - 0.3V) to (AVDD + 0.3V) |

| Digital Input Voltage Range (nCS, SCLK, DIN, DOUT/nDRDY, nDRDY, CLK) .....          | (DGND - 0.3V) to (DVDD + 0.3V) |

| Input Current Range (Continuous, Any Pin except Power Supply Pins) .....            | -10mA to 10mA                  |

| Package Thermal Resistance                                                          |                                |

| TSSOP-16, $\theta_{JA}$ .....                                                       | 107°C/W                        |

| TSSOP-16, $\theta_{JB}$ .....                                                       | 68.9°C/W                       |

| TSSOP-16, $\theta_{JC}$ .....                                                       | 35.2°C/W                       |

| TQFN-3.5x3.5-16L, $\theta_{JA}$ .....                                               | 39.1°C/W                       |

| TQFN-3.5x3.5-16L, $\theta_{JB}$ .....                                               | 14.3°C/W                       |

| TQFN-3.5x3.5-16L, $\theta_{JC}$ (TOP) .....                                         | 33.3°C/W                       |

| TQFN-3.5x3.5-16L, $\theta_{JC}$ (BOT) .....                                         | 2.3°C/W                        |

| Junction Temperature .....                                                          | +150°C                         |

| Storage Temperature Range .....                                                     | -65°C to +150°C                |

| Lead Temperature (Soldering, 10s) .....                                             | +260°C                         |

| ESD Susceptibility <sup>(1)(2)</sup>                                                |                                |

| HBM .....                                                                           | ±4000V                         |

| CDM .....                                                                           | ±1000V                         |

## NOTES:

1. For human body model (HBM), all pins comply with ANSI/ESDA/JEDEC JS-001 specifications.

2. For charged device model (CDM), all pins comply with ANSI/ESDA/JEDEC JS-002 specifications.

## OVERSTRESS CAUTION

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

## ESD SENSITIVITY CAUTION

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

## RECOMMENDED OPERATING CONDITIONS

|                                                                                                                     |                                          |

|---------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| Unipolar Analog Power Supply Range                                                                                  |                                          |

| AVDD to AVSS .....                                                                                                  | 2.3V to 5.5V                             |

| AVSS to DGND .....                                                                                                  | -0.1V to 0.1V                            |

| Bipolar Analog Power Supply Range                                                                                   |                                          |

| AVDD to DGND .....                                                                                                  | 2.3V to 2.75V, 2.5V (TYP)                |

| AVSS to DGND .....                                                                                                  | -2.75V to -2.3V, -2.5V (TYP)             |

| Digital Power Supply Range                                                                                          |                                          |

| DVDD to DGND .....                                                                                                  | 2.3V to 5.5V                             |

| Differential Input Voltage Range, $V_{IN}$ , ( $V_{IN} = V_{AINP} - V_{AINN}$ ) <sup>(3)(4)</sup> .....             | - $V_{REF}/Gain$ to $V_{REF}/Gain$       |

| Absolute Input Voltage Range, $V_{AINx}$                                                                            |                                          |

| PGA Disabled, Gain = 1 to 4 .....                                                                                   | (AVSS - 0.1V) to (AVDD + 0.1V)           |

| PGA Enabled, Gain = 1 to 128 .....                                                                                  | See the Low-Noise PGA Section            |

| Common Mode Input Voltage Range                                                                                     |                                          |

| PGA Disabled, Gain = 1 to 4 .....                                                                                   | (AVSS - 0.1V) to (AVDD + 0.1V)           |

| PGA Enabled, Gain = 1 to 128 .....                                                                                  | See the Low-Noise PGA Section            |

| Differential Reference Input Voltage Range <sup>(5)</sup> , $V_{REF}$ , ( $V_{REF} = V_{REFPx} - V_{REFNx}$ ) ..... | 0.75V to AVDD, 2.5V (TYP)                |

| Absolute Negative Reference Voltage Range <sup>(5)</sup> , $V_{REFNx}$ .....                                        | (AVSS - 0.1V) to ( $V_{REFPx} - 0.75V$ ) |

| Absolute Positive Reference Voltage Range <sup>(5)</sup> , $V_{REFPx}$ .....                                        | ( $V_{REFNx} + 0.75V$ ) to (AVDD + 0.1V) |

| External Clock Frequency, $f_{CLK}$ .....                                                                           | 0.5MHz to 4.5MHz, 4.096MHz (TYP)         |

| Duty-Cycle .....                                                                                                    | 40% to 60%                               |

| Input Voltage Range .....                                                                                           | DGND to DVDD                             |

| Operating Temperature Range .....                                                                                   | -40°C to +125°C                          |

## NOTES:

3. The  $AIN_P$  and  $AIN_N$  represent the positive and negative inputs of the PGA. The  $AIN_x$  refers to one of the four available analog inputs. When the PGA is disabled, it means that the low-noise PGA is powered down and bypassed. However, gains of 1, 2, and 4 are still possible in this case. Refer to the Bypassing the PGA section for more details.

4. Except for the effects of gain and offset error, the measurement range is limited to  $\pm[(AVDD - AVSS) - 0.4V]/Gain$  when the PGA is enabled.

5. The REFPx and REFNx refer to one of the two available differential reference input pairs.

## DISCLAIMER

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

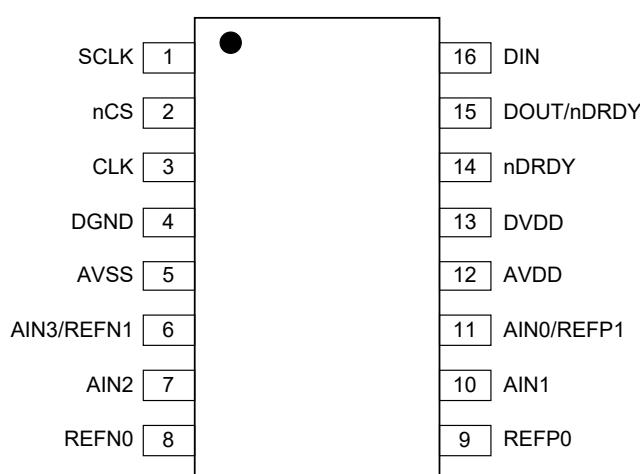

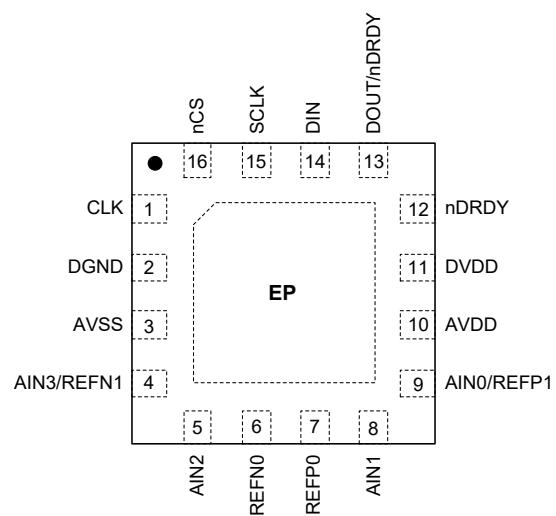

## PIN CONFIGURATIONS

(TOP VIEW)

TSSOP-16

(TOP VIEW)

TQFN-3.5x3.5-16L

## PIN DESCRIPTION

| PIN      |                  | NAME       | TYPE | FUNCTION                                                                                                                   |

|----------|------------------|------------|------|----------------------------------------------------------------------------------------------------------------------------|

| TSSOP-16 | TQFN-3.5x3.5-16L |            |      |                                                                                                                            |

| 1        | 15               | SCLK       | DI   | Serial Clock Input Pin.                                                                                                    |

| 2        | 16               | nCS        | DI   | Chip Select Pin. Active low. Connect to DGND when not in use.                                                              |

| 3        | 1                | CLK        | DI   | External Clock Source Pin. Connect to DGND when not in use.                                                                |

| 4        | 2                | DGND       | G    | Digital Ground.                                                                                                            |

| 5        | 3                | AVSS       | P    | Negative Analog Power Supply.                                                                                              |

| 6        | 4                | AIN3/REFN1 | AI   | Analog Input 3/Negative Reference Input 1.<br>The internal low-side power switch is connected between AIN3/REFN1 and AVSS. |

| 7        | 5                | AIN2       | AI   | Analog Input 2.                                                                                                            |

| 8        | 6                | REFNO      | AI   | Negative Reference Input 0.                                                                                                |

| 9        | 7                | REFP0      | AI   | Positive Reference Input 0.                                                                                                |

| 10       | 8                | AIN1       | AI   | Analog Input 1.                                                                                                            |

| 11       | 9                | AIN0/REFP1 | AI   | Analog Input 0/Positive Reference Input 1.                                                                                 |

| 12       | 10               | AVDD       | P    | Positive Analog Power Supply.                                                                                              |

| 13       | 11               | DVDD       | P    | Positive Digital Power Supply.                                                                                             |

| 14       | 12               | nDRDY      | DO   | Data Ready Pin. Active low. Keep floating or tie to DVDD with a weak pull-up resistor if unused.                           |

| 15       | 13               | DOUT/nDRDY | DO   | Serial Data Output Combined with Data Ready. Active low.                                                                   |

| 16       | 14               | DIN        | DI   | Serial Data Input Pin.                                                                                                     |

| —        | Exposed Pad      | EP         | —    | Exposed Pad. It should be connected to AVSS.                                                                               |

NOTE: DI = digital input, DO = digital output, AI = analog input, P = power, G = ground.

## ELECTRICAL CHARACTERISTICS

( $T_A = -40^\circ\text{C}$  to  $+125^\circ\text{C}$ ,  $\text{AVDD} = 3.3\text{V}$ ,  $\text{AVSS} = 0\text{V}$ ,  $\text{DVDD} = 3.3\text{V}$ , PGA enabled,  $\text{DR} = 20\text{SPS}$ , and external  $\text{V}_{\text{REF}} = 2.5\text{V}$ , typical values are at  $T_A = +25^\circ\text{C}$ , unless otherwise noted.)<sup>(1)</sup>

| PARAMETER                                  | SYMBOL                 | CONDITIONS                                                                                    | MIN                                              | TYP                                                 | MAX  | UNITS                        |

|--------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------|------|------------------------------|

| <b>Analog Inputs</b>                       |                        |                                                                                               |                                                  |                                                     |      |                              |

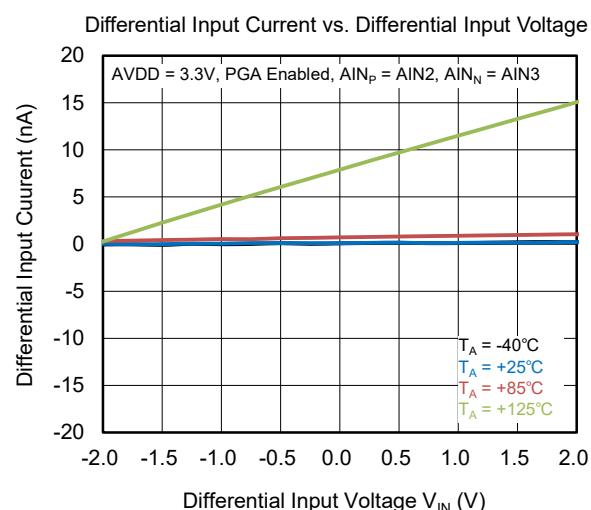

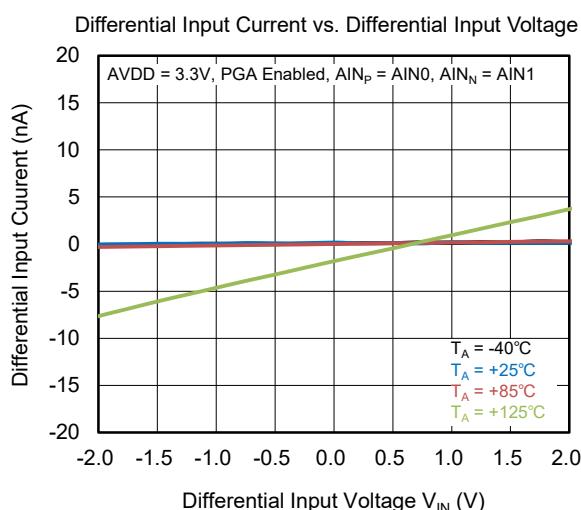

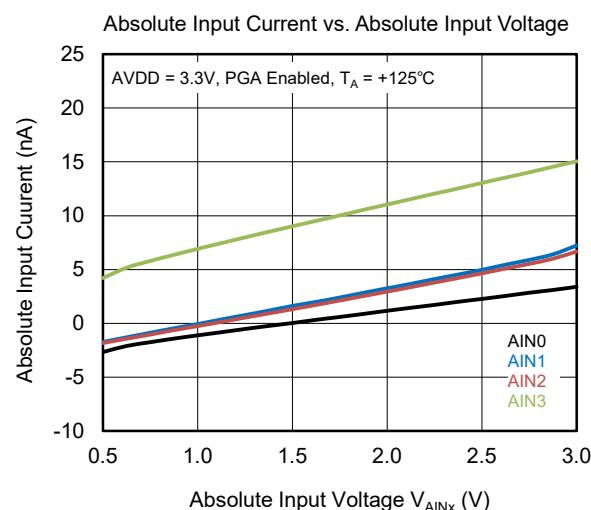

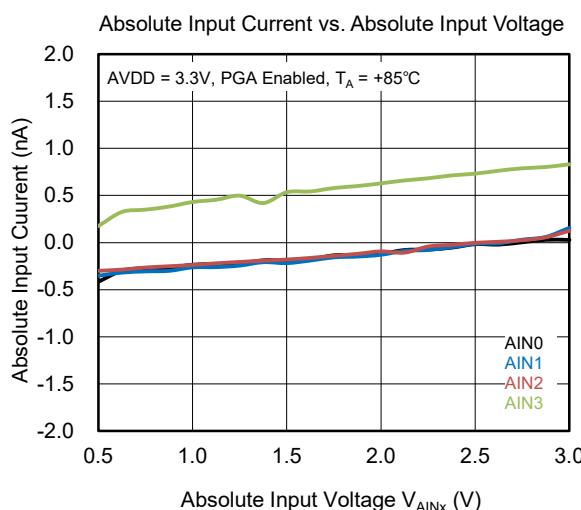

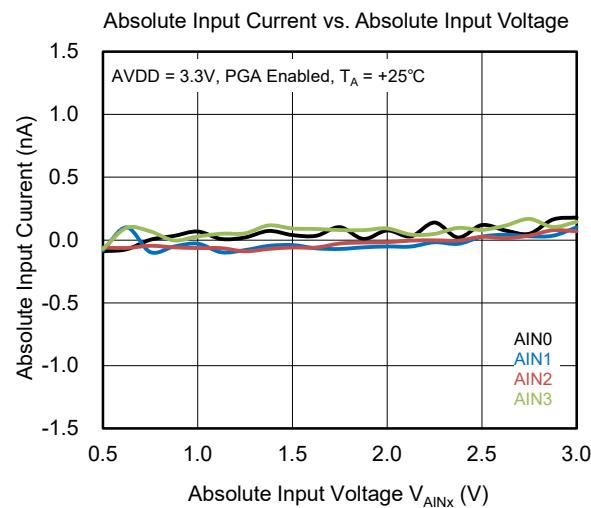

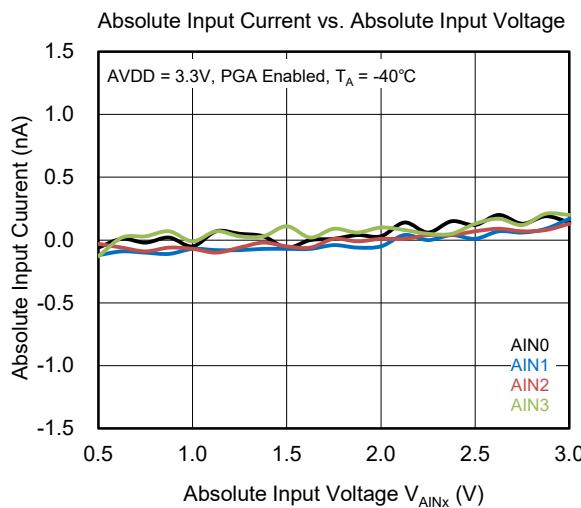

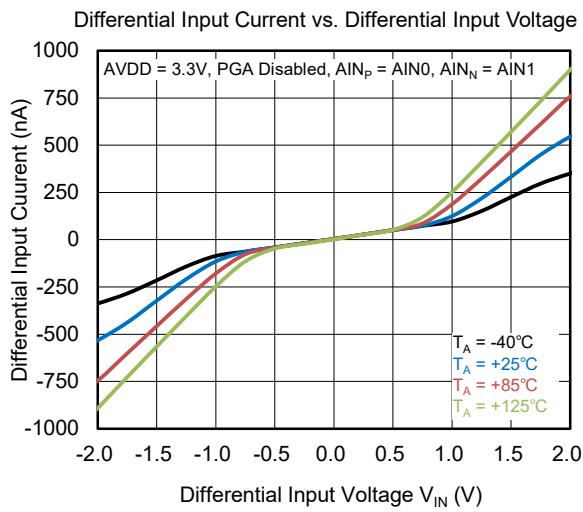

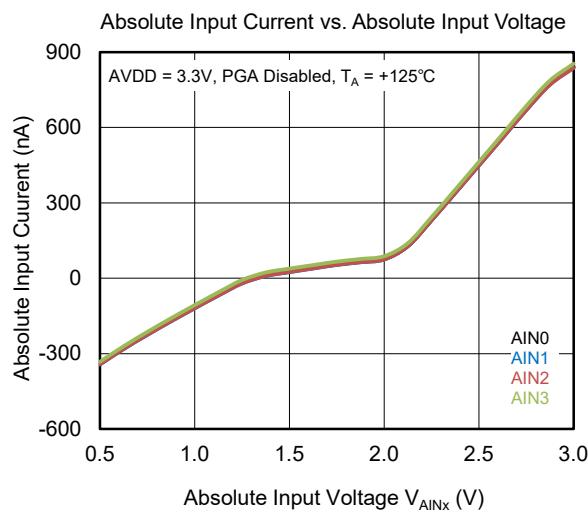

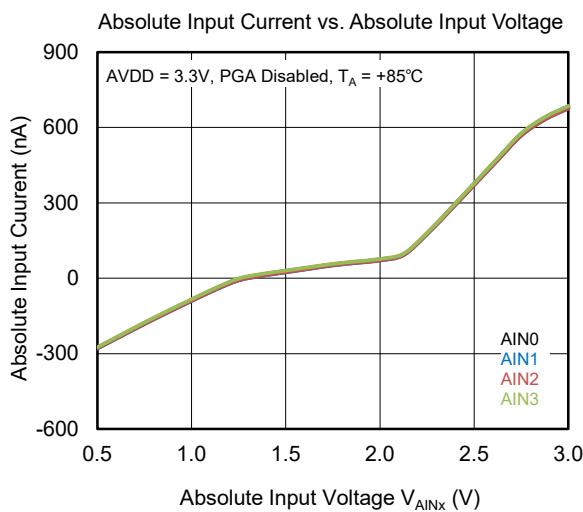

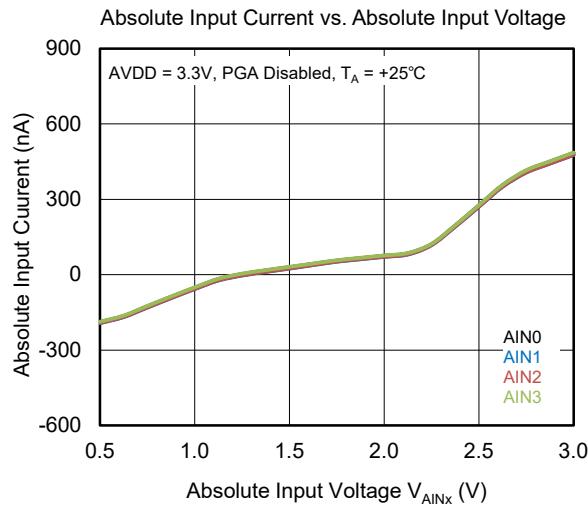

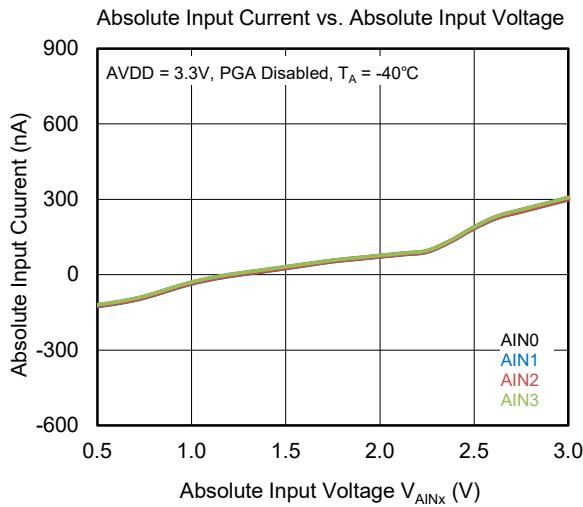

| Absolute Input Current                     |                        |                                                                                               |                                                  | See the Typical Performance Characteristics section |      |                              |

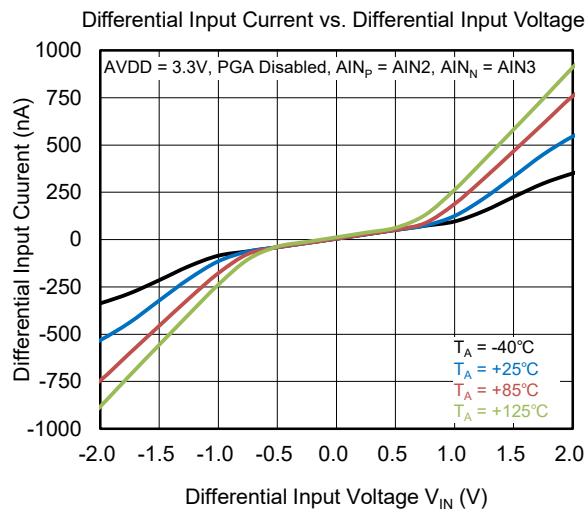

| Differential Input Current                 |                        |                                                                                               |                                                  | See the Typical Performance Characteristics section |      |                              |

| <b>System Performance</b>                  |                        |                                                                                               |                                                  |                                                     |      |                              |

| Resolution<br>(No Missing Codes)           |                        |                                                                                               |                                                  | 16                                                  |      | Bits                         |

| Data Rate                                  | DR                     | Normal mode                                                                                   | 20, 40, 75, 150, 300, 600, 1000                  |                                                     |      | SPS                          |

|                                            |                        | Duty-cycle mode                                                                               | 5, 10, 18.75, 37.5, 75, 150, 250                 |                                                     |      |                              |

|                                            |                        | Turbo mode                                                                                    | 40, 80, 150, 300, 600, 1200, 2000                |                                                     |      |                              |

| Noise (Input-Referred)                     |                        |                                                                                               | See the Noise Performance section                |                                                     |      |                              |

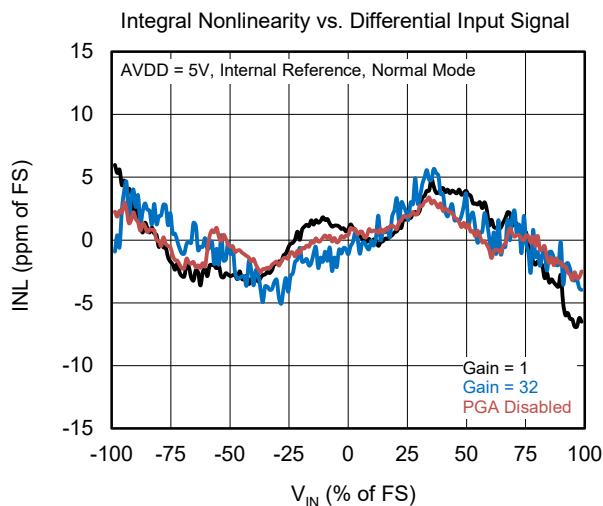

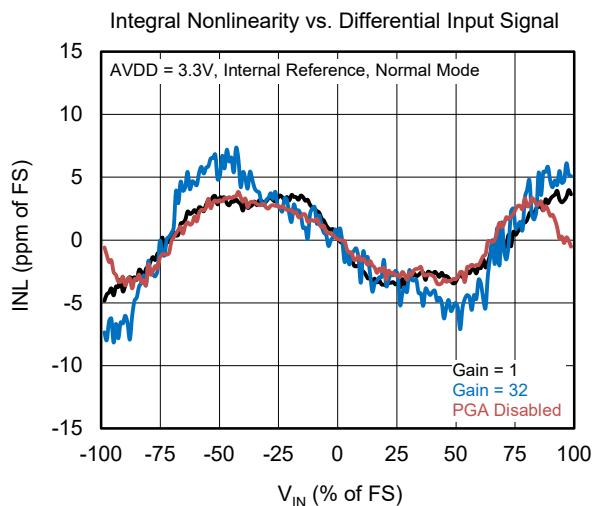

| Integral Nonlinearity                      | INL                    | $\text{Gain} = 1$ to 128, $\text{V}_{\text{CM}} = 0.5 \text{ AVDD}$ , best fit <sup>(2)</sup> |                                                  | $\pm 4.5$                                           | 20   | ppmFSR                       |

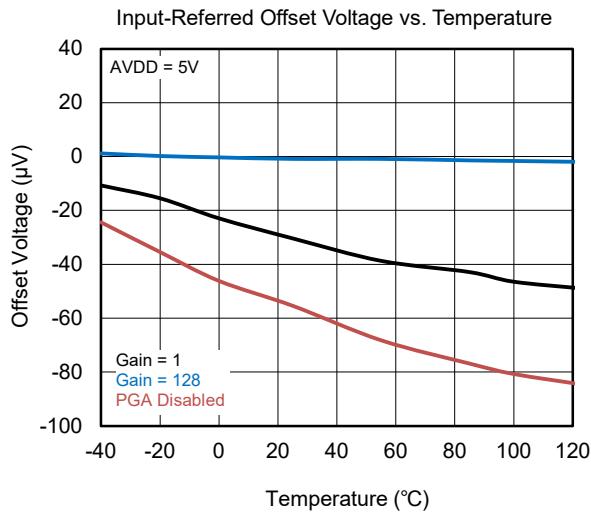

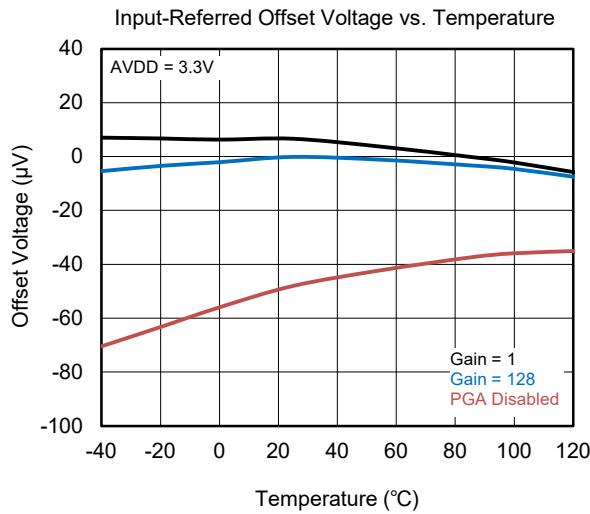

| Input Offset Voltage                       | $\text{V}_{\text{IO}}$ | PGA disabled, Gain = 1 to 4, differential inputs                                              |                                                  | $\pm 70$                                            |      | $\mu\text{V}$                |

|                                            |                        | Gain = 1 to 128, differential inputs                                                          |                                                  | $\pm 5$                                             |      |                              |

| Offset Drift                               |                        | PGA disabled, Gain = 1 to 4                                                                   |                                                  | 0.15                                                |      | $\mu\text{V}/^\circ\text{C}$ |

|                                            |                        | Gain = 1 to 128, $T_A = -40^\circ\text{C}$ to $+85^\circ\text{C}$ <sup>(2)</sup>              |                                                  | 0.15                                                | 0.35 |                              |

|                                            |                        | Gain = 1 to 128                                                                               |                                                  | 0.15                                                |      |                              |

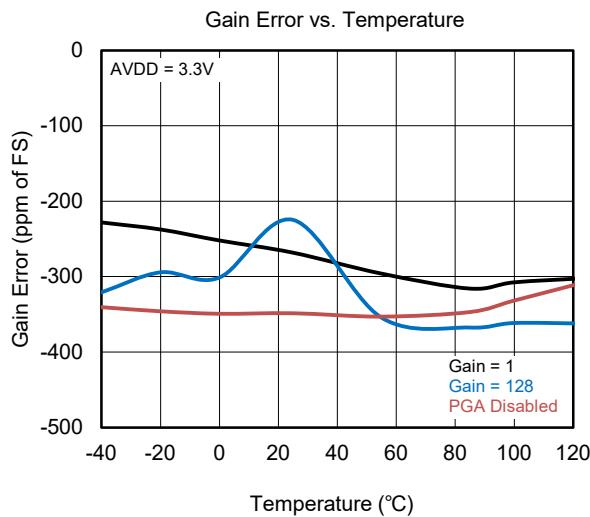

| Gain Error                                 | $\text{E}_G$           | PGA disabled, Gain = 1 to 4                                                                   |                                                  | $\pm 0.015$                                         |      | %                            |

|                                            |                        | Gain = 1 to 64, $T_A = +25^\circ\text{C}$                                                     | -0.07                                            | $\pm 0.015$                                         | 0.07 |                              |

|                                            |                        | Gain = 1 to 128, $T_A = +25^\circ\text{C}$                                                    |                                                  | $\pm 0.04$                                          | 0.25 |                              |

| Gain Drift                                 |                        | PGA disabled, Gain = 1 to 4                                                                   |                                                  | 1                                                   |      | ppm/ $^\circ\text{C}$        |

|                                            |                        | Gain = 1 to 128 <sup>(2)</sup>                                                                |                                                  | 1.5                                                 | 4    |                              |

| Normal Mode Rejection Ratio <sup>(2)</sup> | NMRR                   | DR = 20SPS,<br>external CLK                                                                   | 50Hz $\pm 3\%$ ,<br>50/60[1:0] bits = 10         | 100                                                 |      | dB                           |

|                                            |                        |                                                                                               | 60Hz $\pm 3\%$ ,<br>50/60[1:0] bits = 11         | 100                                                 |      |                              |

|                                            |                        |                                                                                               | 50Hz or 60Hz $\pm 3\%$ ,<br>50/60[1:0] bits = 01 | 85                                                  |      |                              |

| Common Mode Rejection Ratio                | CMRR                   | At DC, Gain = 1                                                                               |                                                  | 95                                                  |      | dB                           |

|                                            |                        | $f_{\text{CM}} = 50\text{Hz}$ , DR = 2000SPS <sup>(2)</sup>                                   |                                                  | 101                                                 |      |                              |

|                                            |                        | $f_{\text{CM}} = 60\text{Hz}$ , DR = 2000SPS <sup>(2)</sup>                                   |                                                  | 101                                                 |      |                              |

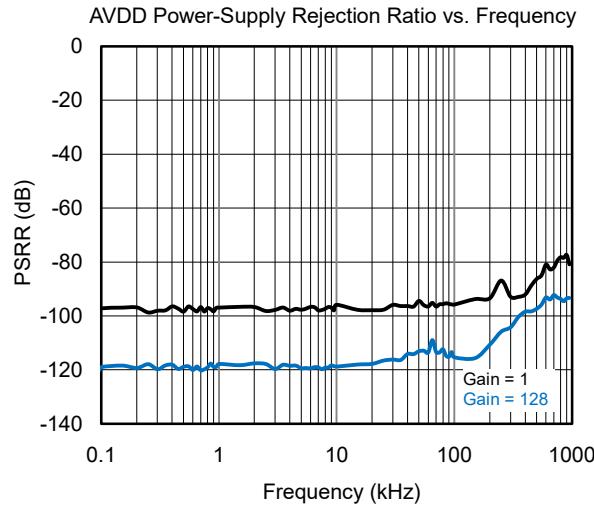

| Power Supply Rejection Ratio               | PSRR                   | AVDD at DC, $\text{V}_{\text{CM}} = 0.5 \text{ AVDD}$ , Gain = 1                              | 80                                               | 95                                                  |      | dB                           |

|                                            |                        | DVDD at DC, $\text{V}_{\text{CM}} = 0.5 \text{ AVDD}$ , Gain = 1 <sup>(2)</sup>               | 98                                               | 120                                                 |      |                              |

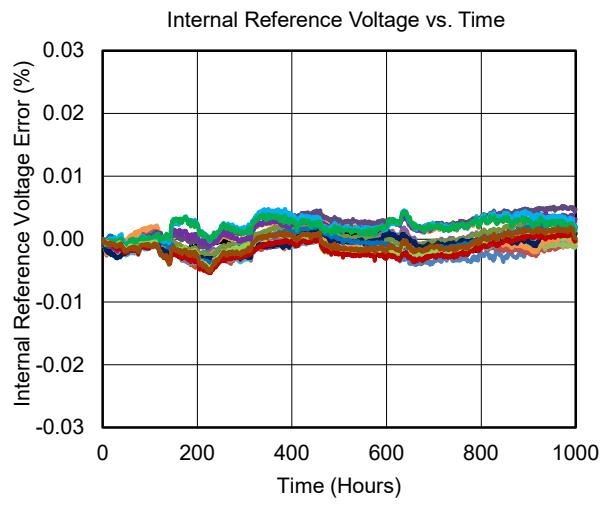

| <b>Internal Voltage Reference</b>          |                        |                                                                                               |                                                  |                                                     |      |                              |

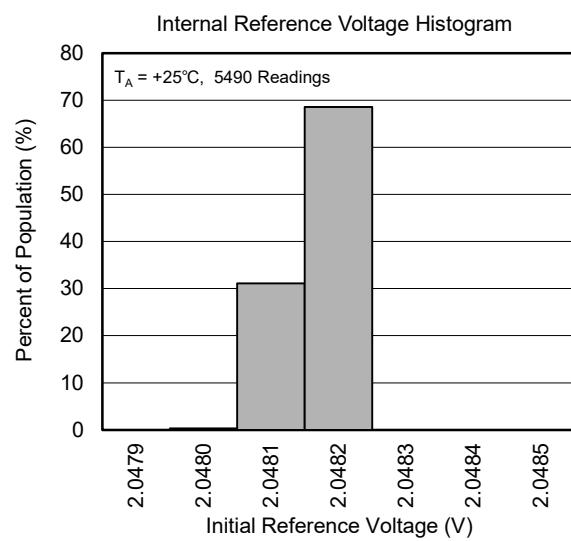

| Initial Accuracy                           |                        | $T_A = +25^\circ\text{C}$                                                                     |                                                  | 2.048                                               |      | V                            |

| Reference Drift <sup>(2)</sup>             |                        |                                                                                               |                                                  | 5                                                   | 10   | ppm/ $^\circ\text{C}$        |

| Long-Term Drift                            |                        | 1000 hours                                                                                    |                                                  | 80                                                  |      | ppm                          |

| <b>Voltage Reference Inputs</b>            |                        |                                                                                               |                                                  |                                                     |      |                              |

| Reference Input Current                    |                        | $\text{REFP0} = \text{V}_{\text{REF}}$ , $\text{REFN0} = \text{AVSS}$                         |                                                  | $\pm 25$                                            |      | nA                           |

| <b>Internal Oscillator</b>                 |                        |                                                                                               |                                                  |                                                     |      |                              |

| Internal Oscillator Accuracy               |                        | Normal mode                                                                                   | -2.2                                             | $\pm 0.15$                                          | 2.2  | %                            |

## NOTES:

1. PGA disabled stands for the low-noise PGA is bypassed, while the gains are still available for 1, 2, and 4. Refer to the Bypassing the PGA section for more information.

2. Design and characterization data guarantee the establishment of the minimum and maximum values.

## ELECTRICAL CHARACTERISTICS (continued)

( $T_A = -40^\circ\text{C}$  to  $+125^\circ\text{C}$ ,  $\text{AVDD} = 3.3\text{V}$ ,  $\text{AVSS} = 0\text{V}$ ,  $\text{DVDD} = 3.3\text{V}$ , PGA enabled,  $\text{DR} = 20\text{SPS}$ , and external  $\text{V}_{\text{REF}} = 2.5\text{V}$ , typical values are at  $T_A = +25^\circ\text{C}$ , unless otherwise noted.)<sup>(1)</sup>

| PARAMETER                                 | SYMBOL          | CONDITIONS                                                                                      | MIN                           | TYP        | MAX               | UNITS                     |

|-------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------|-------------------------------|------------|-------------------|---------------------------|

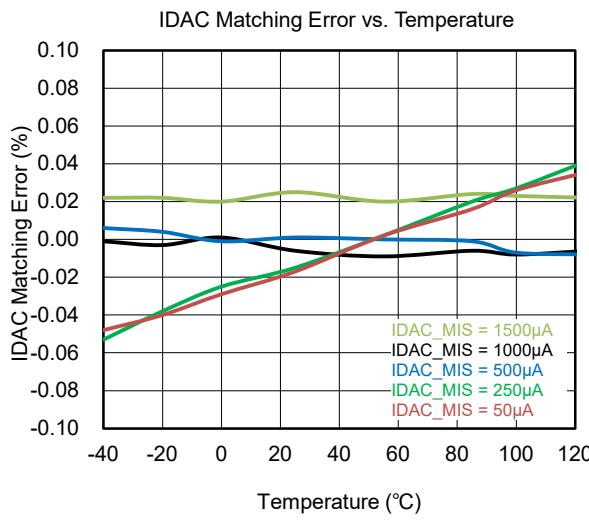

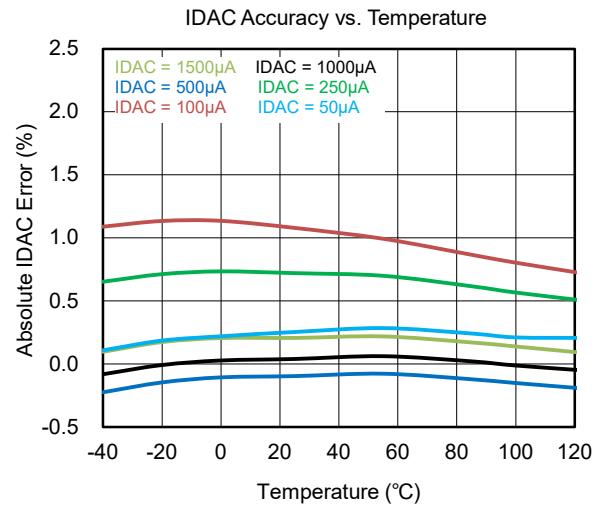

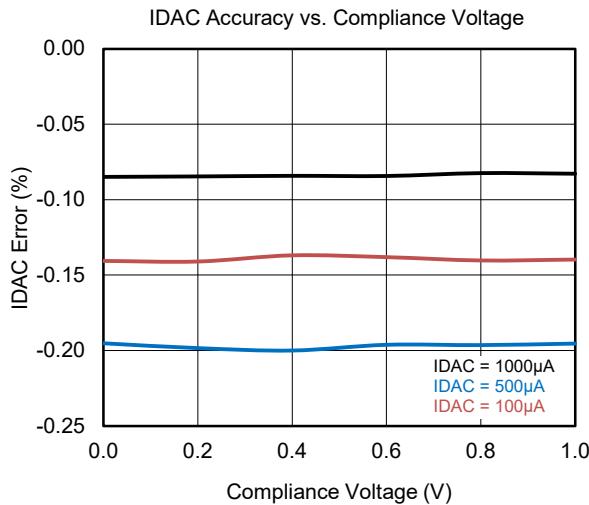

| <b>Excitation Current Sources (IDACs)</b> |                 |                                                                                                 |                               |            |                   |                           |

| Current Settings                          |                 |                                                                                                 | 50, 100, 250, 500, 1000, 1500 |            |                   | $\mu\text{A}$             |

| Compliance Voltage                        |                 | All current settings                                                                            |                               |            | AVDD - 0.9        | V                         |

| Accuracy                                  |                 | 1500 $\mu\text{A}$ , 1000 $\mu\text{A}$ current settings                                        |                               | $\pm 0.2$  |                   | %                         |

|                                           |                 | 500 $\mu\text{A}$ , 50 $\mu\text{A}$ current settings                                           |                               | $\pm 0.4$  |                   |                           |

|                                           |                 | 250 $\mu\text{A}$ current setting                                                               |                               | $\pm 0.8$  |                   |                           |

|                                           |                 | 100 $\mu\text{A}$ current setting                                                               |                               | $\pm 1.1$  |                   |                           |

| Current Match                             |                 | Between IDACs                                                                                   |                               | $\pm 0.7$  |                   | %                         |

|                                           |                 | Between IDACs (not valid for 100 $\mu\text{A}$ setting)                                         |                               | $\pm 0.02$ |                   |                           |

| Temperature Drift                         |                 | 1500 $\mu\text{A}$ , 1000 $\mu\text{A}$ , 500 $\mu\text{A}$ , 50 $\mu\text{A}$ current settings |                               | 17.5       | 47                | ppm/ $^\circ\text{C}$     |

|                                           |                 | 250 $\mu\text{A}$ current setting                                                               |                               | 26         | 65                |                           |

|                                           |                 | 100 $\mu\text{A}$ current setting                                                               |                               | 44         | 101               |                           |

| Temperature Drift Matching                |                 | Between IDACs, 1500 $\mu\text{A}$ current setting                                               |                               | 1.1        | 3                 | ppm/ $^\circ\text{C}$     |

|                                           |                 | Between IDACs, 1000 $\mu\text{A}$ current setting                                               |                               | 1.7        | 4.5               |                           |

|                                           |                 | Between IDACs, 500 $\mu\text{A}$ current setting                                                |                               | 3          | 7.5               |                           |

|                                           |                 | Between IDACs, 250 $\mu\text{A}$ current setting                                                |                               | 3.5        | 11                |                           |

|                                           |                 | Between IDACs, 100 $\mu\text{A}$ current setting                                                |                               | 32         | 65                |                           |

|                                           |                 | Between IDACs, 50 $\mu\text{A}$ current setting                                                 |                               | 7.5        | 26                |                           |

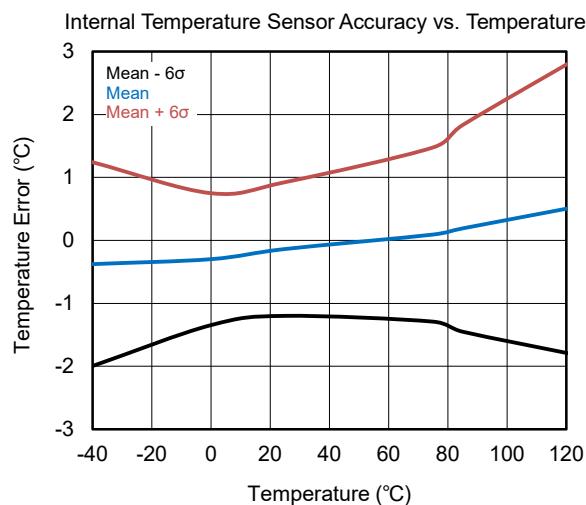

| <b>Temperature Sensor</b>                 |                 |                                                                                                 |                               |            |                   |                           |

| Conversion Resolution                     |                 |                                                                                                 |                               | 14         |                   | Bits                      |

| Temperature Resolution                    |                 |                                                                                                 |                               | 0.03125    |                   | $^\circ\text{C}$          |

| Accuracy                                  |                 | $T_A = 0^\circ\text{C}$ to $+75^\circ\text{C}$                                                  | -1.5                          | $\pm 0.5$  | 1.5               | $^\circ\text{C}$          |

|                                           |                 | $T_A = -40^\circ\text{C}$ to $+125^\circ\text{C}$                                               | -3                            | $\pm 0.9$  | 3                 |                           |

| Accuracy vs. Analog Supply Voltage        |                 |                                                                                                 |                               | 0.18       | 1.1               | $^\circ\text{C}/\text{V}$ |

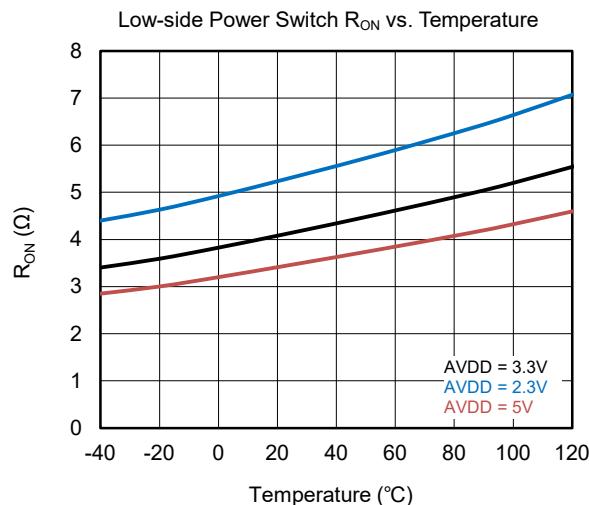

| <b>Low-side Power Switch</b>              |                 |                                                                                                 |                               |            |                   |                           |

| On-Resistance                             | $R_{\text{ON}}$ |                                                                                                 |                               | 4.5        |                   | $\Omega$                  |

| Current through Switch                    |                 |                                                                                                 |                               |            | 30                | mA                        |

| <b>Digital Inputs/Outputs</b>             |                 |                                                                                                 |                               |            |                   |                           |

| High-Level Input Voltage                  | $V_{\text{IH}}$ |                                                                                                 | 0.7 $\times$ DVDD             |            | DVDD              | V                         |

| Low-Level Input Voltage                   | $V_{\text{IL}}$ |                                                                                                 | DGND                          |            | 0.3 $\times$ DVDD | V                         |

| High-Level Output Voltage                 | $V_{\text{OH}}$ | $I_{\text{OH}} = 3\text{mA}$                                                                    | 0.8 $\times$ DVDD             |            |                   | V                         |

| Low-Level Output Voltage                  | $V_{\text{OL}}$ | $I_{\text{OL}} = 3\text{mA}$                                                                    |                               |            | 0.2 $\times$ DVDD | V                         |

| Input High Leakage Current                | $I_{\text{IH}}$ | $V_{\text{IH}} = 5.5\text{V}$                                                                   | -1                            |            | 1                 | $\mu\text{A}$             |

| Input Low Leakage Current                 | $I_{\text{IL}}$ | $V_{\text{IL}} = \text{DGND}$                                                                   | -1                            |            | 1                 | $\mu\text{A}$             |

## ELECTRICAL CHARACTERISTICS (continued)

( $T_A = -40^\circ\text{C}$  to  $+125^\circ\text{C}$ ,  $\text{AVDD} = 3.3\text{V}$ ,  $\text{AVSS} = 0\text{V}$ ,  $\text{DVDD} = 3.3\text{V}$ , PGA enabled,  $\text{DR} = 20\text{SPS}$ , and external  $\text{V}_{\text{REF}} = 2.5\text{V}$ , typical values are at  $T_A = +25^\circ\text{C}$ , unless otherwise noted.)<sup>(1)</sup>

| PARAMETER                             | SYMBOL                   | CONDITIONS                    | MIN            | TYP  | MAX | UNITS |

|---------------------------------------|--------------------------|-------------------------------|----------------|------|-----|-------|

| <b>Power Supply</b>                   |                          |                               |                |      |     |       |

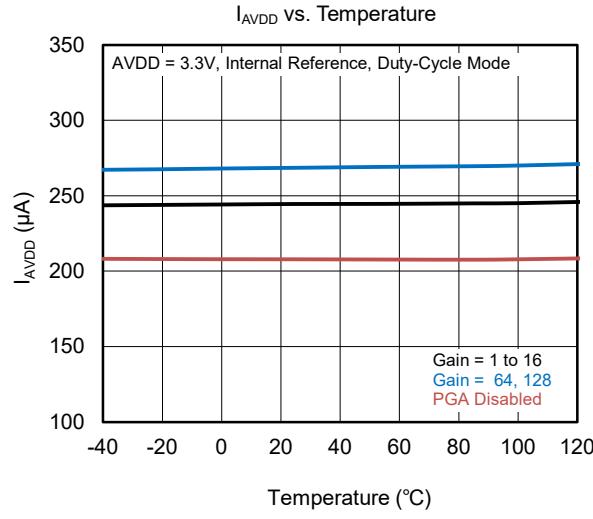

| Analog Supply Current <sup>(3)</sup>  | $\text{I}_{\text{AVDD}}$ | Power-down mode               |                | 0.45 | 2.5 |       |

|                                       |                          | Duty-cycle mode               | PGA disabled   | 175  |     |       |

|                                       |                          |                               | Gain = 1 to 16 | 206  |     |       |

|                                       |                          |                               | Gain = 32      | 211  |     |       |

|                                       |                          | Normal mode                   | Gain = 64, 128 | 216  |     |       |

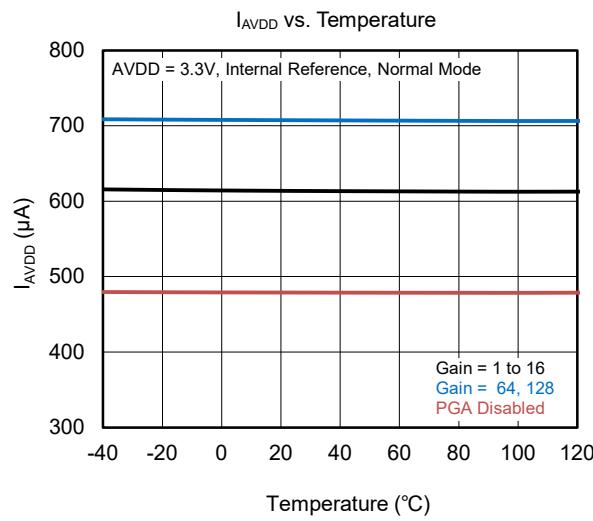

|                                       |                          |                               | PGA disabled   | 480  |     |       |

|                                       |                          |                               | Gain = 1 to 16 | 615  | 750 |       |

|                                       |                          |                               | Gain = 32      | 655  |     |       |

|                                       |                          | Turbo mode                    | Gain = 64, 128 | 706  |     |       |

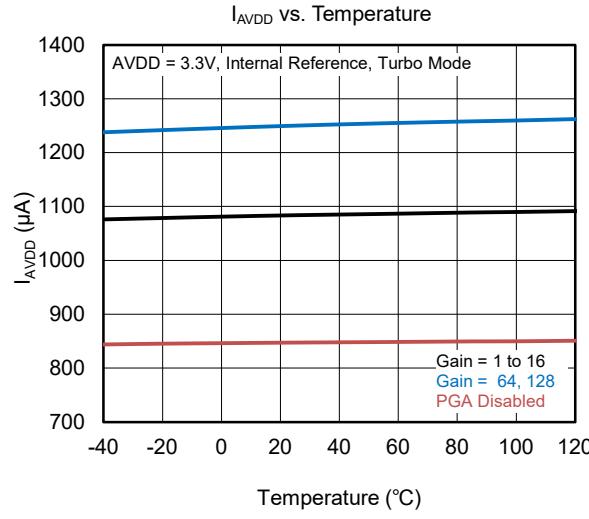

|                                       |                          |                               | PGA disabled   | 752  |     |       |

|                                       |                          |                               | Gain = 1 to 16 | 950  |     |       |

|                                       |                          |                               | Gain = 32      | 996  |     |       |

|                                       |                          |                               | Gain = 64, 128 | 1027 |     |       |

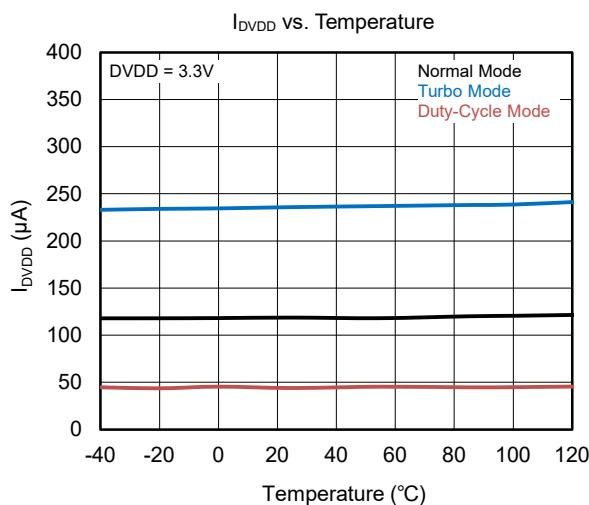

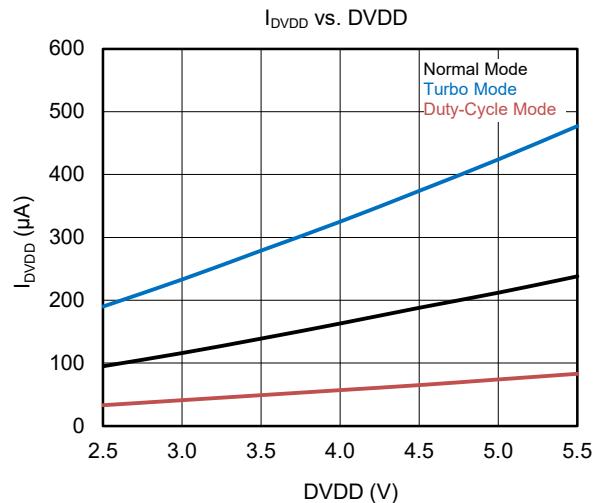

| Digital Supply Current <sup>(3)</sup> | $\text{I}_{\text{DVDD}}$ | Power-down mode               |                | 0.45 | 3   |       |

|                                       |                          | Duty-cycle mode               |                | 48   |     |       |

|                                       |                          | Normal mode                   |                | 120  | 200 |       |

|                                       |                          | Turbo mode                    |                | 246  |     |       |

| Power Dissipation <sup>(3)</sup>      | $\text{P}_D$             | Duty-cycle mode, PGA disabled |                | 0.8  |     |       |

|                                       |                          | Normal mode, Gain = 1 to 16   |                | 2.5  |     |       |

|                                       |                          | Turbo mode, Gain = 1 to 16    |                | 4    |     |       |

## NOTE:

3. With the internal voltage reference engaged, the internal oscillator activated, IDACs in the deactivated state, and continuous conversion mode, the analog supply current experiences a fall of 70 $\mu\text{A}$  on average (typical) in both normal mode and turbo mode when transitioning to an external reference. In cases where the IDACs are enabled (excluding the current flowing through the IDACs themselves), the analog supply current undergoes a typical elevation of 200 $\mu\text{A}$ .

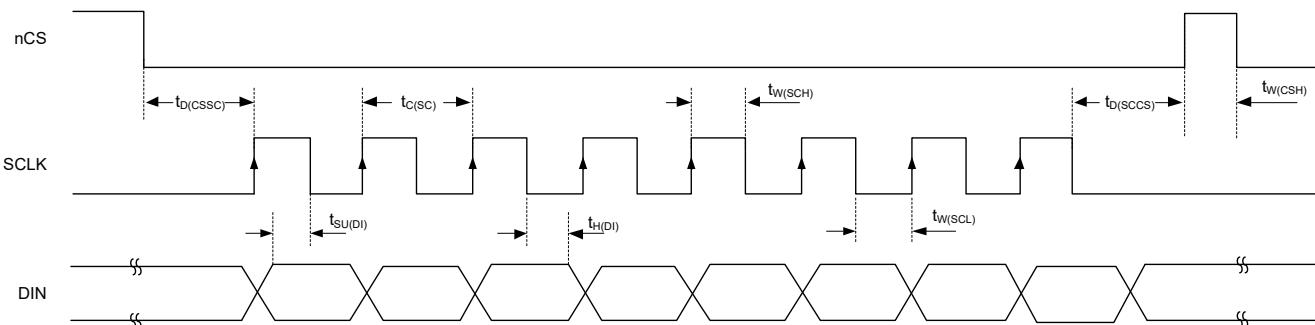

## SPI TIMING REQUIREMENTS

(T<sub>A</sub> = -40°C to +125°C, DVDD = 2.3V to 5.5V, unless otherwise noted.)

| PARAMETER                                                             | SYMBOL               | CONDITIONS                      | MIN | TYP | MAX   | UNITS            |

|-----------------------------------------------------------------------|----------------------|---------------------------------|-----|-----|-------|------------------|

| Delay Time, nCS Falling Edge to First SCLK Rising Edge <sup>(1)</sup> | t <sub>D(CSSC)</sub> |                                 | 50  |     |       | ns               |

| Delay Time, Final SCLK Falling Edge to nCS Rising Edge                | t <sub>D(SCCS)</sub> |                                 | 25  |     |       | ns               |

| Pulse Duration, nCS High                                              | t <sub>W(CSH)</sub>  |                                 | 50  |     |       | ns               |

| SCLK Period                                                           | t <sub>C(SC)</sub>   |                                 | 150 |     |       | ns               |

| Pulse Duration, SCLK High                                             | t <sub>W(SCH)</sub>  |                                 | 60  |     |       | ns               |

| Pulse Duration, SCLK Low                                              | t <sub>W(SCL)</sub>  |                                 | 60  |     |       | ns               |

| Setup Time, DIN Valid before SCLK Falling Edge                        | t <sub>SU(DI)</sub>  |                                 | 50  |     |       | ns               |

| Hold Time, DIN Valid after SCLK Falling Edge                          | t <sub>H(DI)</sub>   |                                 | 25  |     |       | ns               |

| SPI Timeout <sup>(2)</sup>                                            |                      | Normal mode,<br>duty-cycle mode |     |     | 13955 | t <sub>MOD</sub> |

|                                                                       |                      | Turbo mode                      |     |     | 27910 | t <sub>MOD</sub> |

## NOTES:

1. nCS can be kept low without sharing SPI bus with the other devices.

2. Using the internal oscillator or an external 4.096MHz clock. t<sub>MOD</sub> = 1/f<sub>MOD</sub>. The modulator frequency f<sub>MOD</sub> is 256kHz for normal and duty-cycle modes and 512kHz for turbo mode.

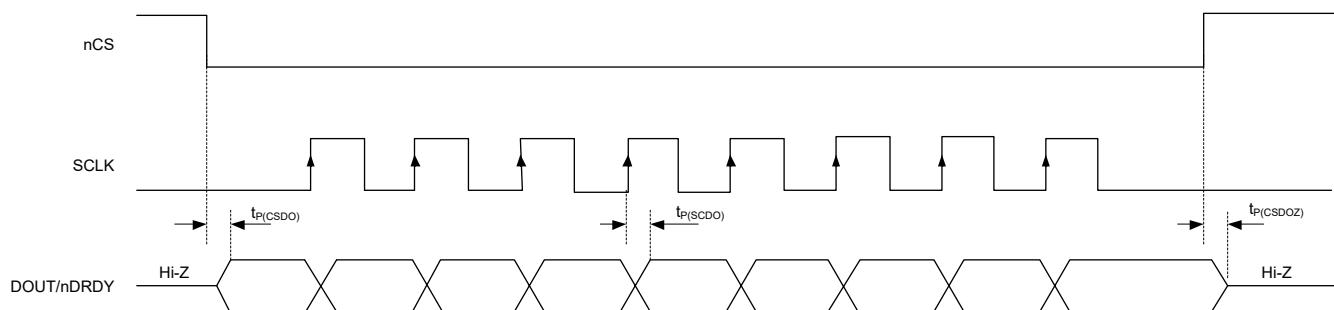

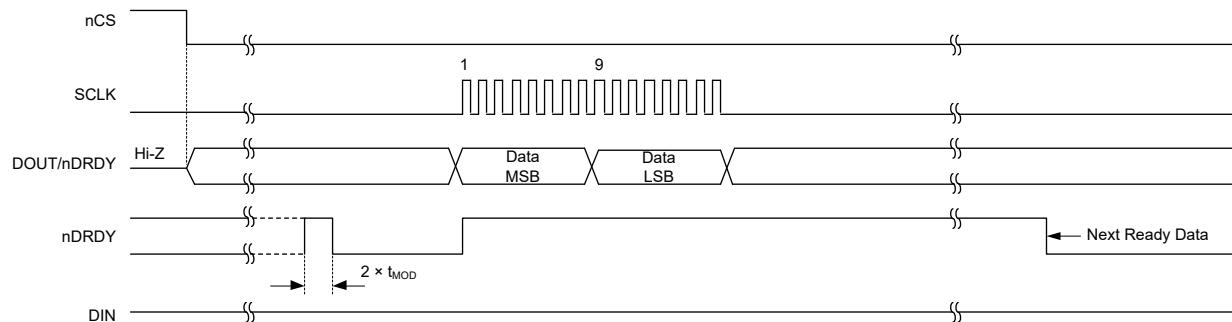

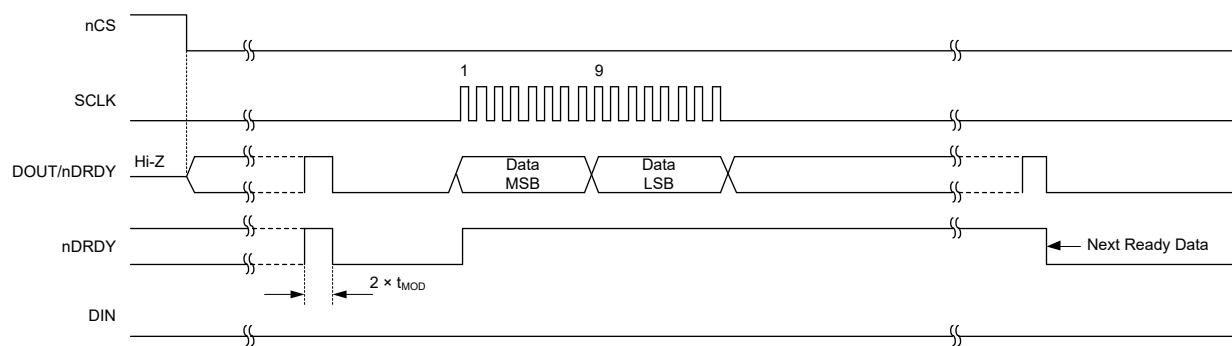

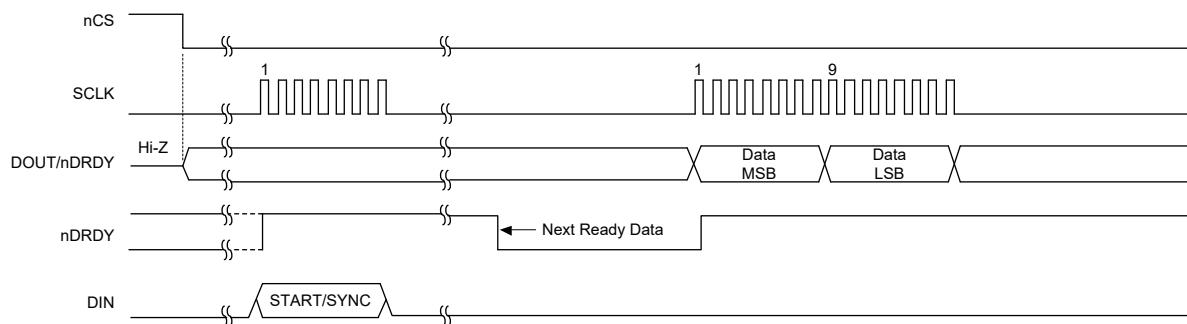

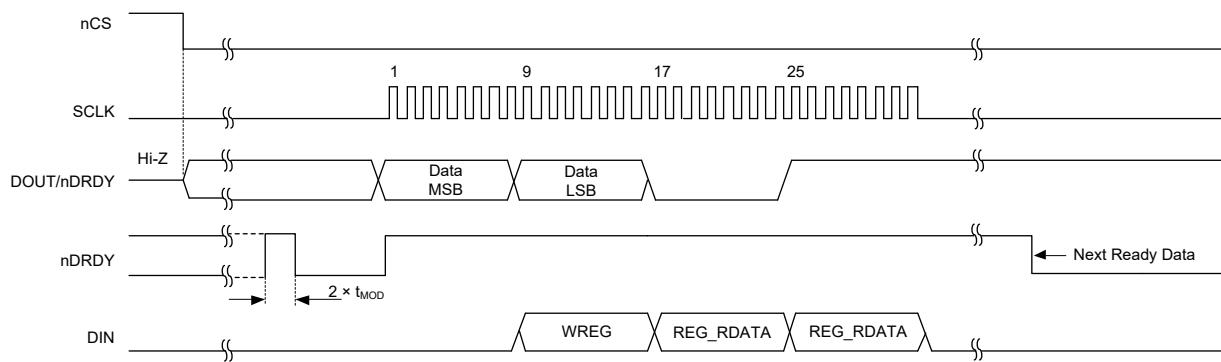

## NOTE:

Shown as the single-byte communication, the actual communication may be multiple bytes.

Figure 1. Serial Interface Timing Diagram

## SPI SWITCHING CHARACTERISTICS

(T<sub>A</sub> = -40°C to +125°C, DVDD = 2.3V to 5.5V, unless otherwise noted.)

| PARAMETER                                                      | SYMBOL         | CONDITIONS                       | MIN | TYP | MAX | UNITS |

|----------------------------------------------------------------|----------------|----------------------------------|-----|-----|-----|-------|

| Propagation Delay Time, nCS Falling Edge to DOUT Driven        | $t_{P(CSD0)}$  | DOUT load = 20pF    10kΩ to DGND |     |     | 50  | ns    |

| Propagation Delay Time, SCLK Rising Edge to Valid New DOUT     | $t_{P(SCD0)}$  | DOUT load = 20pF    10kΩ to DGND | 0   |     | 50  | ns    |

| Propagation Delay Time, nCS Rising Edge to DOUT High Impedance | $t_{P(CSD0Z)}$ | DOUT load = 20pF    10kΩ to DGND |     |     | 50  | ns    |

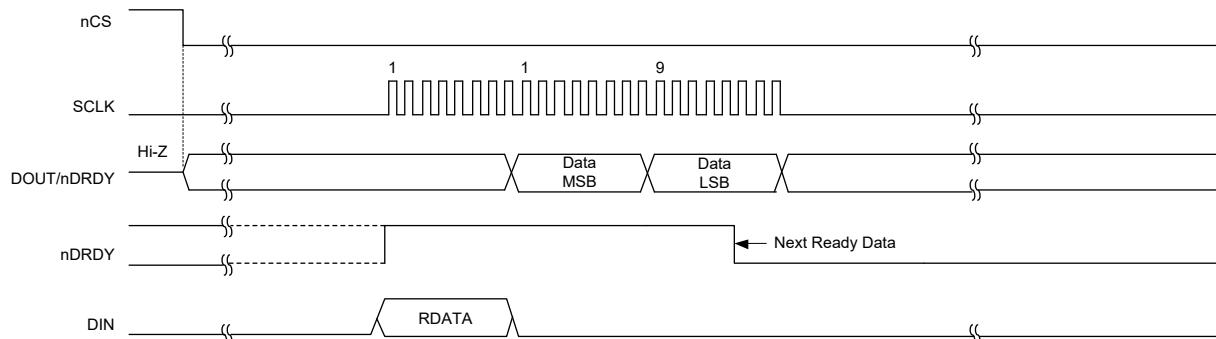

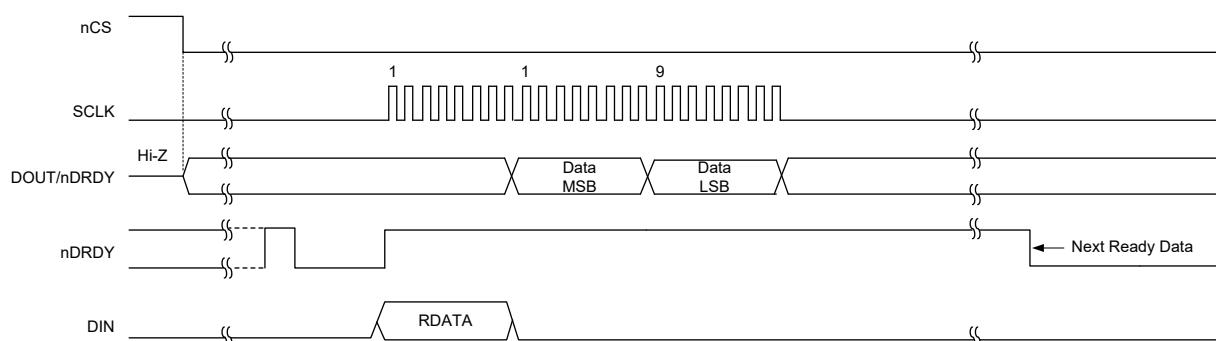

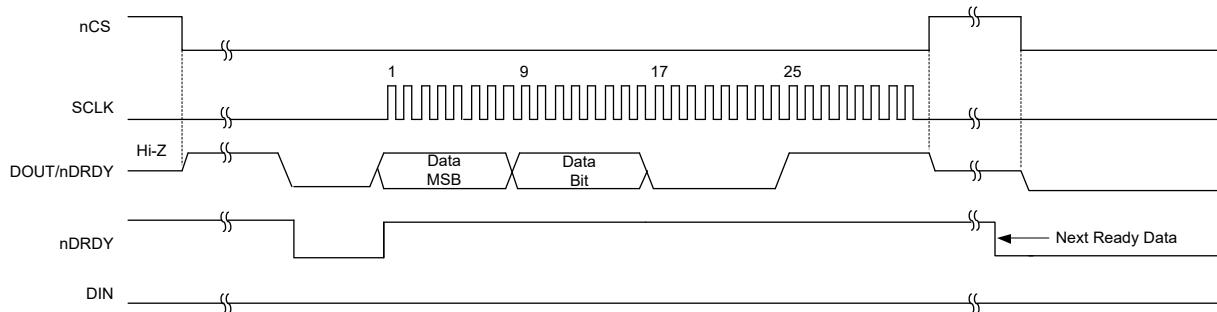

NOTE:

Shown as the single-byte communication, the actual communication may be multiple bytes.

Figure 2. Serial Interface Switching Characteristics

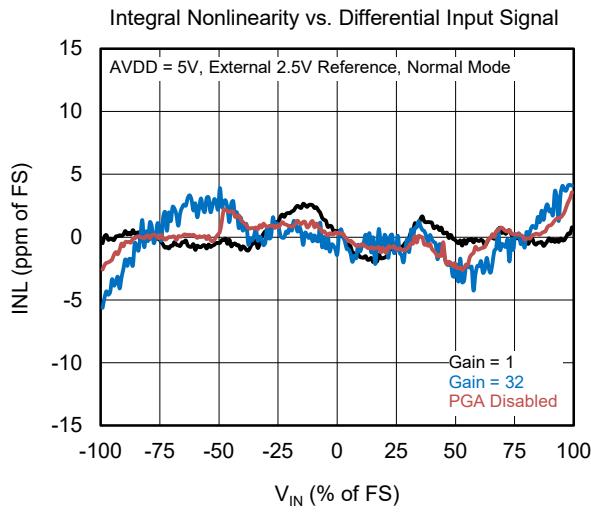

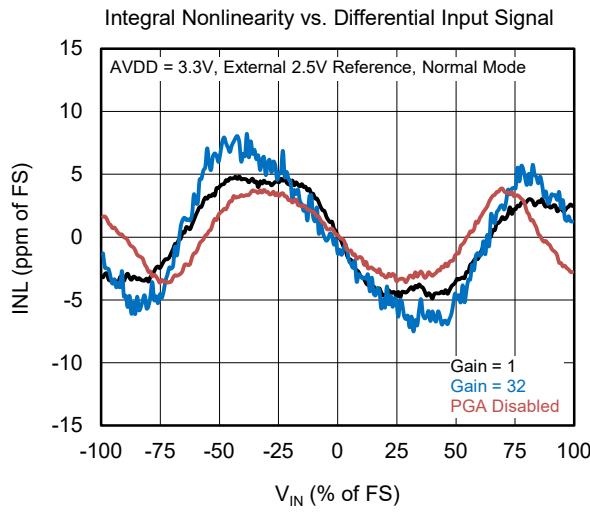

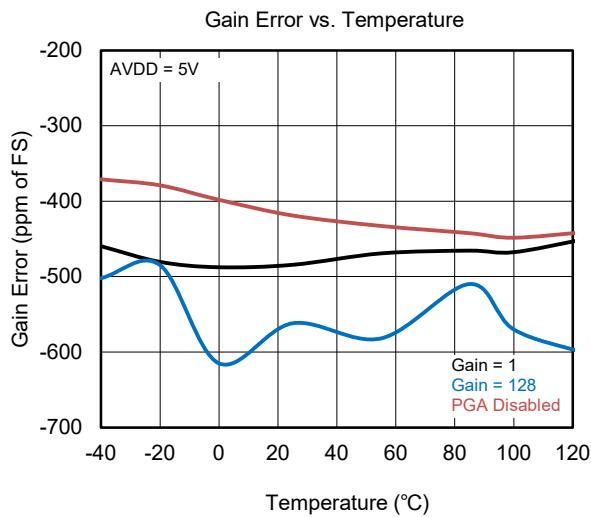

## TYPICAL PERFORMANCE CHARACTERISTICS

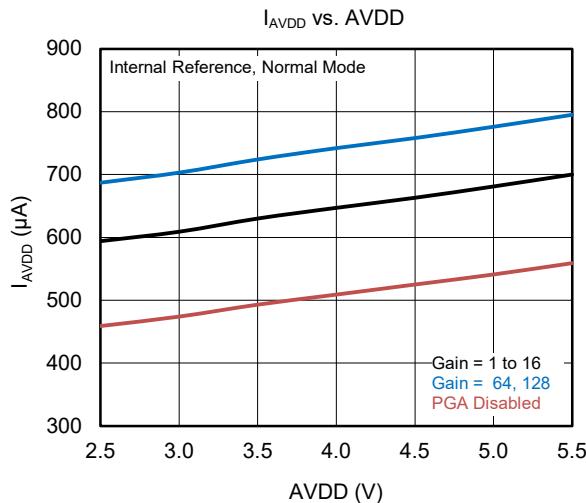

$T_A = +25^\circ\text{C}$ , AVDD = 3.3V, AVSS = 0V, and PGA enabled using external  $V_{\text{REF}} = 2.5\text{V}$ , unless otherwise noted.

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

TA = +25°C, AVDD = 3.3V, AVSS = 0V, and PGA enabled using external VREF = 2.5V, unless otherwise noted.

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

TA = +25°C, AVDD = 3.3V, AVSS = 0V, and PGA enabled using external VREF = 2.5V, unless otherwise noted.

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$T_A = +25^\circ\text{C}$ ,  $\text{AVDD} = 3.3\text{V}$ ,  $\text{AVSS} = 0\text{V}$ , and PGA enabled using external  $\text{V}_{\text{REF}} = 2.5\text{V}$ , unless otherwise noted.

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$T_A = +25^\circ\text{C}$ ,  $\text{AVDD} = 3.3\text{V}$ ,  $\text{AVSS} = 0\text{V}$ , and PGA enabled using external  $\text{V}_{\text{REF}} = 2.5\text{V}$ , unless otherwise noted.

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$T_A = +25^\circ\text{C}$ ,  $\text{AVDD} = 3.3\text{V}$ ,  $\text{AVSS} = 0\text{V}$ , and PGA enabled using external  $\text{V}_{\text{REF}} = 2.5\text{V}$ , unless otherwise noted.

## PARAMETER MEASUREMENT INFORMATION

## Noise Performance

The sigma-delta ( $\Sigma\Delta$ ) analog-to-digital converters (ADCs) operate on the oversampling principle. In this technique, the input signal of a  $\Sigma\Delta$  ADC is sampled at a high frequency called the modulator frequency. Subsequently, the sampled data undergoes digital filtering and decimation, resulting in a conversion outcome at the desired output data rate. The relationship between the modulator frequency and the output data rate is termed the oversampling ratio (OSR). Improve the OSR to reduce the output data rate, and optimize the ADC's noise performance. Lowering the output data rate reduces input-related noise, as more modulator samples are averaged for each conversion outcome. Increasing the gain further decreases the input-referred noise, which is especially beneficial for precise measurement of weak signals.

The noise performance details are presented in Table 1 through Table 8. These tables showcase the typical noise performance results at  $+25^\circ\text{C}$  using the internal 2.048V reference. The data represents average readings from a single device over approximately 0.75 seconds, with the

inputs shorted together internally. For the given conditions, Table 1, Table 3, Table 5, and Table 7 report input-referred noise in  $\mu\text{V}_{\text{RMS}}$  units (with corresponding values in  $\mu\text{V}_{\text{PP}}$  shown in parentheses). Meanwhile, Table 2, Table 4, Table 6, and Table 8 present the corresponding information in terms of effective number of bits (ENOB), derived from  $\mu\text{V}_{\text{RMS}}$  values using Equation 1. Additionally, the noise-free bits, determined from peak-to-peak noise values through Equation 2, are indicated in parentheses.

It is noteworthy that the input-referred noise (Table 1, Table 3, Table 5, and Table 7) experiences only minor fluctuations when an external low-noise reference is used. When dealing with reference voltages other than 2.048V, ENOB values and noise-free bits can be calculated by using Equation 1 through Equation 3.

$$\text{ENOB} = \ln(\text{Full-Scale Range}/V_{\text{RMS-Noise}})/\ln(2) \quad (1)$$

$$\text{Noise-Free Bits} = \ln(\text{Full-Scale Range}/V_{\text{PP-Noise}})/\ln(2) \quad (2)$$

$$\text{Full-Scale Range} = 2 \cdot V_{\text{REF}}/\text{Gain} \quad (3)$$

Table 1. Noise in  $\mu\text{V}_{\text{RMS}}$  ( $\mu\text{V}_{\text{PP}}$ ) at  $\text{AVDD} = 3.3\text{V}$ ,  $\text{AVSS} = 0\text{V}$ , Normal Mode, and Internal Reference = 2.048V

| Data Rate (SPS) | Gain (PGA Enabled) |               |               |             |             |             |             |             |

|-----------------|--------------------|---------------|---------------|-------------|-------------|-------------|-------------|-------------|

|                 | 1                  | 2             | 4             | 8           | 16          | 32          | 64          | 128         |

| 20              | 62.5 (62.5)        | 31.25 (31.25) | 15.62 (15.62) | 7.81 (7.81) | 3.91 (3.91) | 1.95 (1.95) | 0.98 (0.98) | 0.49 (0.49) |

| 40              | 62.5 (62.5)        | 31.25 (31.25) | 15.62 (15.62) | 7.81 (7.81) | 3.91 (3.91) | 1.95 (1.95) | 0.98 (0.98) | 0.49 (0.49) |

| 75              | 62.5 (62.5)        | 31.25 (31.25) | 15.62 (15.62) | 7.81 (7.81) | 3.91 (3.91) | 1.95 (1.95) | 0.98 (0.98) | 0.49 (0.49) |

| 150             | 62.5 (62.5)        | 31.25 (31.25) | 15.62 (15.62) | 7.81 (7.81) | 3.91 (3.91) | 1.95 (1.95) | 0.98 (0.98) | 0.49 (0.98) |

| 300             | 62.5 (62.5)        | 31.25 (31.25) | 15.62 (15.62) | 7.81 (7.81) | 3.91 (3.91) | 1.95 (1.95) | 0.98 (1.95) | 0.49 (1.95) |

| 600             | 62.5 (62.5)        | 31.25 (31.25) | 15.62 (15.62) | 7.81 (7.81) | 3.91 (3.91) | 1.95 (1.95) | 0.98 (2.93) | 0.49 (2.44) |

| 1000            | 62.5 (62.5)        | 31.25 (31.25) | 15.62 (15.62) | 7.81 (7.81) | 3.91 (3.91) | 1.95 (3.91) | 0.98 (2.93) | 0.49 (3.91) |

Table 2. ENOB from RMS Noise (Noise-Free Bits from Peak-to-Peak Noise) at  $\text{AVDD} = 3.3\text{V}$ ,  $\text{AVSS} = 0\text{V}$ , Normal Mode, and Internal Reference = 2.048V

| Data Rate (SPS) | Gain (PGA Enabled) |             |             |             |             |             |              |              |

|-----------------|--------------------|-------------|-------------|-------------|-------------|-------------|--------------|--------------|

|                 | 1                  | 2           | 4           | 8           | 16          | 32          | 64           | 128          |

| 20              | 16.0 (16.0)        | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0)  | 16.0 (16.0)  |

| 40              | 16.0 (16.0)        | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0)  | 16.0 (16.0)  |

| 75              | 16.0 (16.0)        | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0)  | 16.0 (16.0)  |

| 150             | 16.0 (16.0)        | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0)  | 16.0 (15.0)  |

| 300             | 16.0 (16.0)        | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (15.0)  | 16.0 (14.0)  |

| 600             | 16.0 (16.0)        | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (14.42) | 16.0 (13.68) |

| 1000            | 16.0 (16.0)        | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (15.0) | 16.0 (14.42) | 16.0 (13.0)  |

## PARAMETER MEASUREMENT INFORMATION (continued)

Table 3. Noise in  $\mu\text{VRMS}$  ( $\mu\text{VPP}$ ) with PGA Disabled at AVDD = 3.3V, AVSS = 0V, Normal Mode, and Internal Reference = 2.048V

| Data Rate (SPS) | Gain (PGA Disabled) |               |               |

|-----------------|---------------------|---------------|---------------|

|                 | 1                   | 2             | 4             |

| 20              | 62.5 (62.5)         | 31.25 (31.25) | 15.62 (15.62) |

| 40              | 62.5 (62.5)         | 31.25 (31.25) | 15.62 (15.62) |

| 75              | 62.5 (62.5)         | 31.25 (31.25) | 15.62 (15.62) |

| 150             | 62.5 (62.5)         | 31.25 (31.25) | 15.62 (15.62) |

| 300             | 62.5 (62.5)         | 31.25 (31.25) | 15.62 (15.62) |

| 600             | 62.5 (62.5)         | 31.25 (31.25) | 15.62 (15.62) |

| 1000            | 62.5 (62.5)         | 31.25 (31.25) | 15.62 (31.25) |

Table 4. ENOB from RMS Noise (Noise-Free Bits from Peak-to-Peak Noise) with PGA Disabled at AVDD = 3.3V, AVSS = 0V, Normal Mode, and Internal Reference = 2.048V

| Data Rate (SPS) | Gain (PGA Disabled) |             |             |

|-----------------|---------------------|-------------|-------------|

|                 | 1                   | 2           | 4           |

| 20              | 16.0 (16.0)         | 16.0 (16.0) | 16.0 (16.0) |

| 40              | 16.0 (16.0)         | 16.0 (16.0) | 16.0 (16.0) |

| 75              | 16.0 (16.0)         | 16.0 (16.0) | 16.0 (16.0) |

| 150             | 16.0 (16.0)         | 16.0 (16.0) | 16.0 (16.0) |

| 300             | 16.0 (16.0)         | 16.0 (16.0) | 16.0 (16.0) |

| 600             | 16.0 (16.0)         | 16.0 (16.0) | 16.0 (16.0) |

| 1000            | 16.0 (16.0)         | 16.0 (16.0) | 16.0 (15.0) |

Table 5. Noise in  $\mu\text{VRMS}$  ( $\mu\text{VPP}$ ) at AVDD = 3.3V, AVSS = 0V, Turbo Mode, and Internal Reference = 2.048V

| Data Rate (SPS) | Gain (PGA Enabled) |               |               |             |             |             |             |             |

|-----------------|--------------------|---------------|---------------|-------------|-------------|-------------|-------------|-------------|

|                 | 1                  | 2             | 4             | 8           | 16          | 32          | 64          | 128         |

| 40              | 62.5 (62.5)        | 31.25 (31.25) | 15.62 (15.62) | 7.81 (7.81) | 3.91 (3.91) | 1.95 (1.95) | 0.98 (0.98) | 0.49 (0.49) |

| 80              | 62.5 (62.5)        | 31.25 (31.25) | 15.62 (15.62) | 7.81 (7.81) | 3.91 (3.91) | 1.95 (1.95) | 0.98 (0.98) | 0.49 (0.98) |

| 150             | 62.5 (62.5)        | 31.25 (31.25) | 15.62 (15.62) | 7.81 (7.81) | 3.91 (3.91) | 1.95 (1.95) | 0.98 (0.98) | 0.49 (0.98) |

| 300             | 62.5 (62.5)        | 31.25 (31.25) | 15.62 (15.62) | 7.81 (7.81) | 3.91 (3.91) | 1.95 (1.95) | 0.98 (1.95) | 0.49 (1.46) |

| 600             | 62.5 (62.5)        | 31.25 (31.25) | 15.62 (15.62) | 7.81 (7.81) | 3.91 (3.91) | 1.95 (3.91) | 0.98 (1.95) | 0.49 (1.95) |

| 1200            | 62.5 (62.5)        | 31.25 (31.25) | 15.62 (15.62) | 7.81 (7.81) | 3.91 (3.91) | 1.95 (3.91) | 0.98 (3.91) | 0.49 (2.93) |

| 2000            | 62.5 (62.5)        | 31.25 (31.25) | 15.62 (15.62) | 7.81 (7.81) | 3.91 (7.81) | 1.95 (3.91) | 0.98 (3.91) | 0.49 (3.91) |

Table 6. ENOB from RMS Noise (Noise-Free Bits from Peak-to-Peak Noise) at AVDD = 3.3V, AVSS = 0V, Turbo Mode, and Internal Reference = 2.048V

| Data Rate (SPS) | Gain (PGA Enabled) |             |             |             |             |             |             |              |

|-----------------|--------------------|-------------|-------------|-------------|-------------|-------------|-------------|--------------|

|                 | 1                  | 2           | 4           | 8           | 16          | 32          | 64          | 128          |

| 40              | 16.0 (16.0)        | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0)  |

| 80              | 16.0 (16.0)        | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (15.0)  |

| 150             | 16.0 (16.0)        | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (15.0)  |

| 300             | 16.0 (16.0)        | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (15.0) | 16.0 (14.42) |

| 600             | 16.0 (16.0)        | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (15.0) | 16.0 (15.0) | 16.0 (14.0)  |

| 1200            | 16.0 (16.0)        | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (15.0) | 16.0 (14.0) | 16.0 (13.42) |

| 2000            | 16.0 (16.0)        | 16.0 (16.0) | 16.0 (16.0) | 16.0 (16.0) | 16.0 (15.0) | 16.0 (15.0) | 16.0 (14.0) | 16.0 (13.0)  |

## PARAMETER MEASUREMENT INFORMATION (continued)

Table 7. Noise in  $\mu\text{VRMS}$  ( $\mu\text{VPP}$ ) with PGA Disabled at AVDD = 3.3V, AVSS = 0V, Turbo Mode, and Internal Reference = 2.048V

| Data Rate (SPS) | Gain (PGA Disabled) |               |               |

|-----------------|---------------------|---------------|---------------|

|                 | 1                   | 2             | 4             |

| 40              | 62.5 (62.5)         | 31.25 (31.25) | 15.62 (15.62) |

| 80              | 62.5 (62.5)         | 31.25 (31.25) | 15.62 (15.62) |

| 150             | 62.5 (62.5)         | 31.25 (31.25) | 15.62 (15.62) |

| 300             | 62.5 (62.5)         | 31.25 (31.25) | 15.62 (15.62) |

| 600             | 62.5 (62.5)         | 31.25 (31.25) | 15.62 (15.62) |

| 1200            | 62.5 (62.5)         | 31.25 (31.25) | 15.62 (15.62) |

| 2000            | 62.5 (62.5)         | 31.25 (31.25) | 15.62 (31.25) |

Table 8. ENOB from RMS Noise (Noise-Free Bits from Peak-to-Peak Noise) with PGA Disabled at AVDD = 3.3V, AVSS = 0V, Turbo Mode, and Internal Reference = 2.048V

| Data Rate (SPS) | Gain (PGA Disabled) |             |             |

|-----------------|---------------------|-------------|-------------|

|                 | 1                   | 2           | 4           |

| 40              | 16.0 (16.0)         | 16.0 (16.0) | 16.0 (16.0) |

| 80              | 16.0 (16.0)         | 16.0 (16.0) | 16.0 (16.0) |

| 150             | 16.0 (16.0)         | 16.0 (16.0) | 16.0 (16.0) |

| 300             | 16.0 (16.0)         | 16.0 (16.0) | 16.0 (16.0) |

| 600             | 16.0 (16.0)         | 16.0 (16.0) | 16.0 (16.0) |

| 1200            | 16.0 (16.0)         | 16.0 (16.0) | 16.0 (16.0) |

| 2000            | 16.0 (16.0)         | 16.0 (16.0) | 16.0 (15.0) |

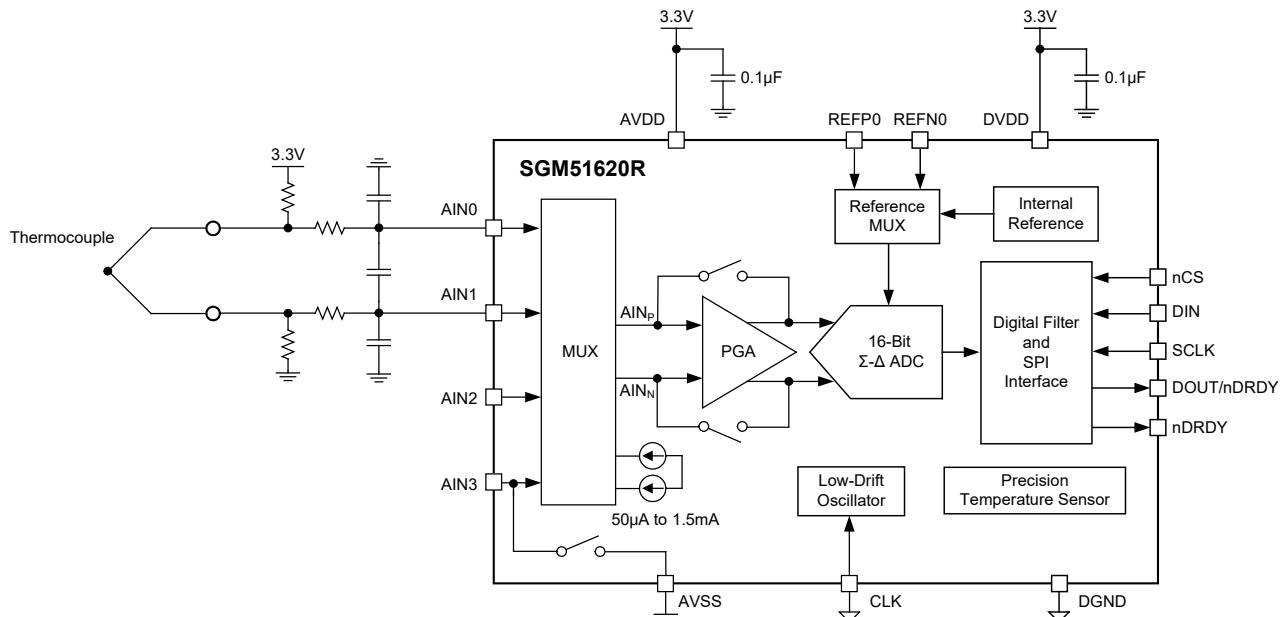

## TYPICAL APPLICATION CIRCUIT

Figure 3. K-Type Thermocouple Measurement

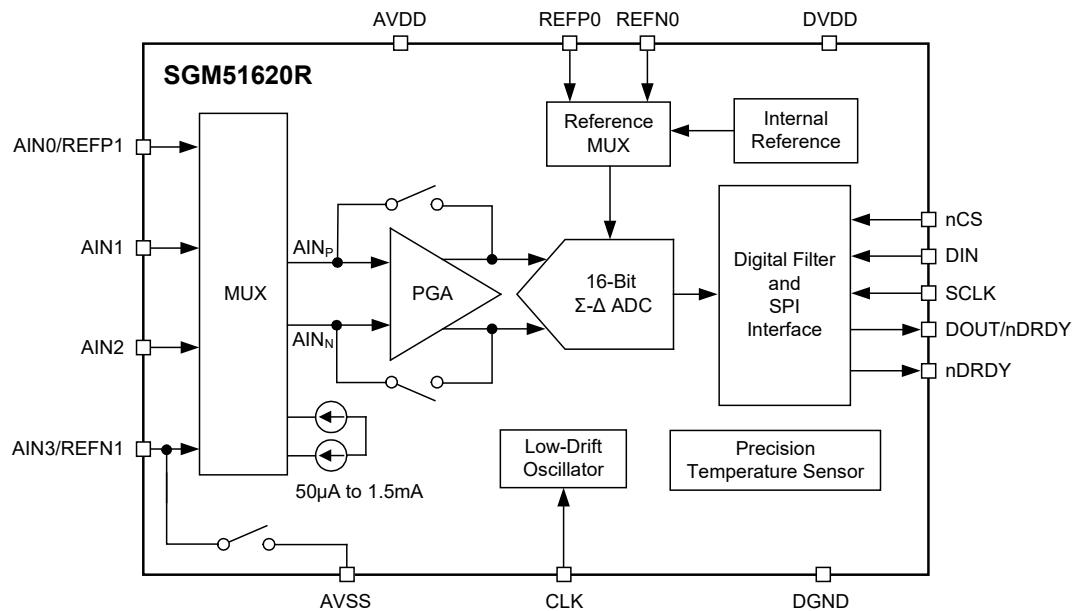

## FUNCTIONAL BLOCK DIAGRAM

Figure 4. Block Diagram

## DETAILED DESCRIPTION

## Overview

The SGM51620R is a compact and energy-efficient 16-bit  $\Sigma\Delta$  ADC designed for applications that require precise measurement of delicate sensor signals. Its small size and low power consumption make it an ideal choice for efficient systems.

Featuring a  $\Sigma\Delta$  ADC core, a single-cycle settling digital filter, a low-noise, high input impedance programmable gain amplifier (PGA), an internal voltage reference, and a clock oscillator, the SGM51620R offers a comprehensive set of functionalities. The inclusion of a highly linear and accurate temperature sensor, along with two precisely matched programmable current sources (IDACs) for sensor excitation, enhances the device's versatility.

The ADC accurately measures a differential signal ( $V_{IN}$ ), which represents the voltage difference between  $AIN_p$  and  $AIN_n$  nodes. Its core comprises a differential switched-capacitor  $\Sigma\Delta$  modulator followed by a digital filter. This architecture effectively attenuates the common mode signals, contributing to improve the signal fidelity.

The SGM51620R provides two conversion modes: single-shot and continuous conversion. In single-shot mode, the ADC performs a single conversion upon request, stores the result in an internal data buffer and enters a low-power state for energy efficiency. Continuous conversion mode initiates a new conversion immediately after the completion of the previous one, providing freshly generated data at the programmed data rate for a consistent flow of information.

## Multiplexer

The SGM51620R features a highly versatile input multiplexer,

as shown in Figure 5. This multiplexer setup provides the flexibility to measure either four single-ended signals, two differential signals, or a combination of two single-ended and one differential signal. The multiplexer configuration is controlled by four bits labeled  $MUX[3:0]$  within the configuration register. When dealing with single-ended signals, a switch within the multiplexer allows the internal connection of the negative ADC input ( $AIN_n$ ) to AVSS. For system monitoring purposes, the ADC offers the option to select either  $(AVDD - AVSS)/4$  or the currently chosen external reference voltage ( $V_{REFPx} - V_{REFNx}$ )/4 as inputs.

In addition, the multiplexer allows routing of the two programmable current sources to any analog input ( $AIN_x$ ) or to dedicated reference pins (REFP0, REFN0), providing enhanced application flexibility. The device incorporates electrostatic discharge (ESD) diodes to protect AVDD and AVSS integrity. To keep these ESD diodes inactive, it is crucial to ensure that the absolute voltage applied to any input falls within the specified range as defined by Equation 4.

$$AVSS - 0.3V < V_{AINx} < AVDD + 0.3V \quad (4)$$

In cases where the voltages applied to the input pins have the potential to exceed the specified conditions, it may be necessary to consider incorporating the external Schottky clamp diodes or series resistors to limit the input current within safe parameters (for detailed guidance, refer to the Absolute Maximum Ratings section). It is important to note that if an unused input is subjected to overdriving, it could potentially impact ongoing conversions on other input pins. In situations where the risk of overdrive on idle inputs exists, it is recommended to use external Schottky diodes to clamp the signal and prevent adverse effects.

Figure 5. Analog Input Multiplexer

## DETAILED DESCRIPTION (continued)

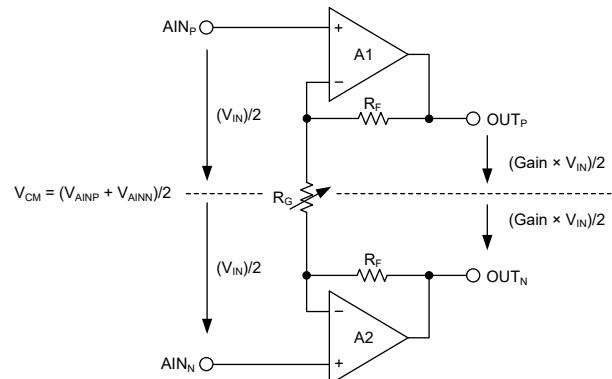

## Low-Noise PGA

The SGM51620R features a programmable gain amplifier (PGA) known for its low-noise, minimal drift and high input impedance characteristics. This versatile PGA allows easy adjustment to achieve gains of 1, 2, 4, 8, 16, 32, 64, or 128, providing significant flexibility. The input of the PGA is strengthened with an electromagnetic interference (EMI) filter, enhancing signal integrity.

The range of the differential full-scale input voltage (FSR) for the programmable gain amplifier (PGA) is determined by the combination of the selected gain setting and the reference voltage used. This relationship is expressed by Equation 5.

$$FSR = \pm V_{REF}/\text{Gain} \quad (5)$$

Table 9 provides an overview of the associated full-scale ranges applicable when utilizing the internal 2.048V reference.

Table 9. PGA Full-Scale Range

| Gain Setting | FSR          |

|--------------|--------------|

| 1            | $\pm 2.048V$ |

| 2            | $\pm 1.024V$ |

| 4            | $\pm 0.512V$ |

| 8            | $\pm 0.256V$ |

| 16           | $\pm 0.128V$ |

| 32           | $\pm 0.064V$ |

| 64           | $\pm 0.032V$ |

| 128          | $\pm 0.016V$ |

## PGA Common Mode Voltage Requirements

To ensure that the programmable gain amplifier (PGA) operates within its linear range, the specific conditions must be met by the input signals, as explained in this section.

In Figure 6, it is crucial to understand that the outputs of both amplifiers (A1 and A2), labeled as OUT<sub>P</sub> and OUT<sub>N</sub>, should not approach the supply rails (AVSS and AVDD) closer than a threshold of 200mV. When these output voltages come within 200mV of the supply rails, the amplifiers go into saturation, leading to nonlinearity. To prevent this nonlinear state, the output voltage levels must meet the criterion shown in Equation 6:

$$AVSS + 0.2V \leq V_{OUTN}, V_{OUTP} \leq AVDD - 0.2V \quad (6)$$

Translating the conditions specified by Equation 6 into requirements for the inputs of the programmable gain amplifier (PGA), specifically AIN<sub>P</sub> and AIN<sub>N</sub>, is beneficial as

direct access to the PGA outputs is not available. Considering the symmetrical nature of the PGA, it is reasonable to assume that the common mode voltage at the PGA output reflects that of the common mode voltage in the input signal. This symmetry is depicted in Figure 6.

Figure 6. PGA Common Mode Voltage

The determination of the common mode voltage is achieved through the utilization of Equation 7:

$$V_{CM} = (V_{AINP} + V_{AINN})/2 = (V_{OUTP} + V_{OUTN})/2 \quad (7)$$

The voltages present at the inputs of the programmable gain amplifier (PGA), named AIN<sub>P</sub> and AIN<sub>N</sub>, can be formulated by using Equation 8 and Equation 9:

$$V_{AINP} = V_{CM} + V_{IN}/2 \quad (8)$$

$$V_{AINN} = V_{CM} - V_{IN}/2 \quad (9)$$

Consequently, the output voltages (V<sub>OUTP</sub> and V<sub>OUTN</sub>) can be calculated according to Equation 10 and Equation 11:

$$V_{OUTP} = V_{CM} + \text{Gain} \times V_{IN}/2 \quad (10)$$

$$V_{OUTN} = V_{CM} - \text{Gain} \times V_{IN}/2 \quad (11)$$

The conditions governing the output voltages of the amplifiers A1 and A2 (as shown in Equation 6) can now be transformed into prerequisites for the input common mode voltage range, employing Equation 10 and Equation 11. This translation leads to the expression of these requirements in the form of Equation 12 and Equation 13:

$$V_{CM(\text{MIN})} \geq AVSS + 0.2V + \text{Gain} \times V_{IN(\text{MAX})}/2 \quad (12)$$

$$V_{CM(\text{MAX})} \leq AVDD - 0.2V - \text{Gain} \times V_{IN(\text{MAX})}/2 \quad (13)$$

## DETAILED DESCRIPTION (continued)

To establish the upper and lower boundaries of the common mode voltage, it is imperative to employ the maximum differential input voltage ( $V_{IN(MAX)}$ ) that emerges within the application. It is important to note that  $V_{IN(MAX)}$  may be less than the theoretically achievable full-scale (FS) value.

Furthermore, apart from adhering to Equation 12, the minimum value of the common mode voltage ( $V_{CM}$ ) must also satisfy Equation 14 due to the distinct design characteristics of the programmable gain amplifier (PGA).

$$V_{CM(MIN)} \geq AVSS + (AVDD - AVSS)/4 \quad (14)$$

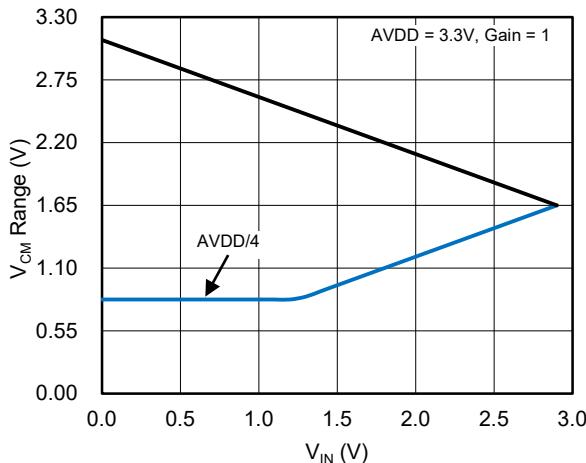

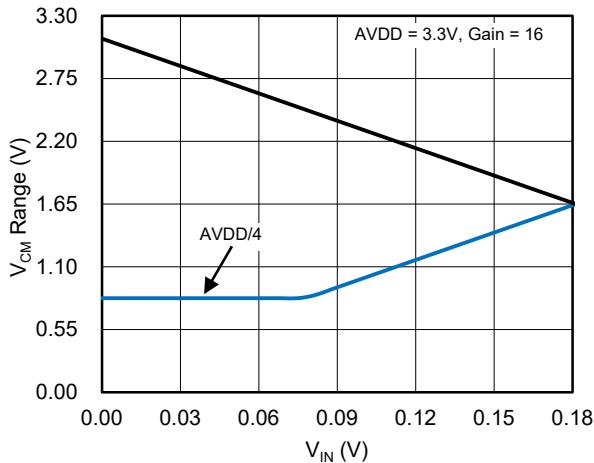

Graphical depictions of the common mode voltage limits are elucidated in Figure 7 and Figure 8. These illustrations are predicated on the conditions of  $AVDD = 3.3V$  and  $AVSS = 0V$ , considering two distinct scenarios: Gain = 1 and Gain = 16.

Figure 7. Common Mode Voltage Limits (Gain = 1)

Figure 8. Common Mode Voltage Limits (Gain = 16)

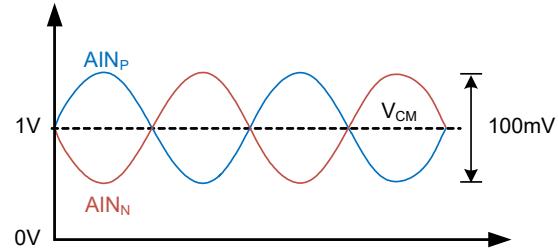

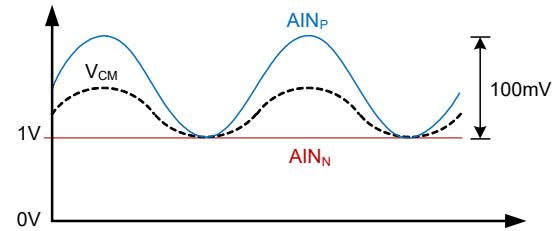

The example of the fully-differential input signal is shown in Figure 9, and the example of the pseudo-differential input signal is shown in Figure 10.

Figure 9. Fully-Differential Input Signal

Figure 10. Pseudo-Differential Input Signal

## Bypassing the PGA

For gain settings of 1, 2, and 4, the device provides an option to turn off and bypass the low-noise PGA by toggling the PGA\_BYPASS bit in the configuration register. Disabling the PGA offers a dual advantage of reducing overall power consumption and relaxing the constraints outlined in Equations 12 to 14 related to the common mode input voltage range ( $V_{CM}$ ). With the PGA turned off, the valid range for both absolute and common mode input voltage is  $(AVSS - 0.1V \leq V_{AINx}, V_{CM} \leq AVDD + 0.1V)$ .

When measuring single-ended signals referenced to AVSS (where  $AIN_P = V_{IN}$  and  $AIN_N = AVSS$ ), bypassing the PGA is necessary. The device allows the configuration of single-ended measurements either by externally connecting one of the analog inputs to AVSS or by utilizing the internal AVSS connection provided by the multiplexer (achieved through MUX[3:0] settings 1000 to 1011). It is important to note that when the internal multiplexer is set to configurations where  $AIN_N = AVSS$  (specifically, MUX[3:0] = 1000 to 1011), the PGA is automatically bypassed and disabled, irrespective of the PGA\_BYPASS setting. Additionally, when the gain is set to values greater than 4, the device limits the gain to a maximum of 4.

## DETAILED DESCRIPTION (continued)

## Modulator

Within the SGM51620R, a sophisticated  $\Sigma\Delta$  modulator is employed to convert the analog input voltage into a pulse code modulated (PCM) data stream. The modulator operates at a clock frequency called  $f_{MOD}$ , which is set to  $f_{CLK}/16$  in both normal and duty-cycle modes. In turbo mode, the clock frequency increases to  $f_{MOD} = f_{CLK}/8$ . The modulator's clock source,  $f_{CLK}$ , can be derived from either the internal oscillator or an external clock input. Table 10 provides a detailed breakdown of modulator frequencies for each operational mode, depending on whether the internal oscillator or an external clock source with a frequency of 4.096MHz is used.

**Table 10. Modulator Clock Frequency for Different Operating Modes<sup>(1)</sup>**

| Operating Mode  | $f_{MOD}$ |

|-----------------|-----------|

| Duty-cycle mode | 256kHz    |

| Normal mode     | 256kHz    |

| Turbo mode      | 512kHz    |

NOTE:

1. Using the internal oscillator or an external 4.096MHz clock.

## Digital Filter

The SGM51620R features a finite impulse response (FIR) digital filter with linear-phase characteristics. This filter serves

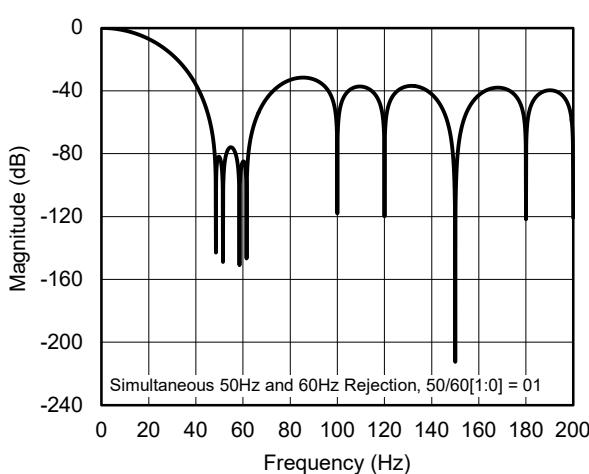

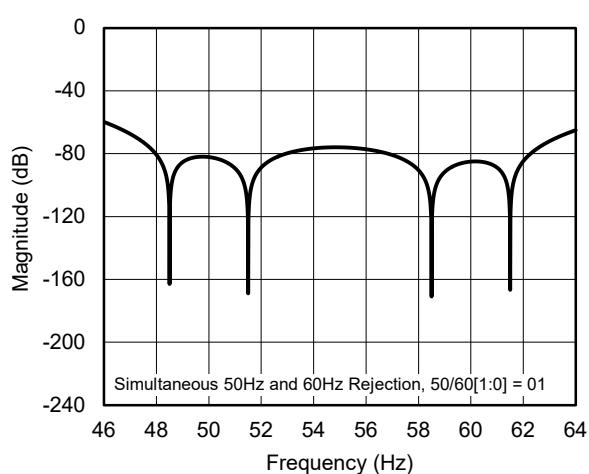

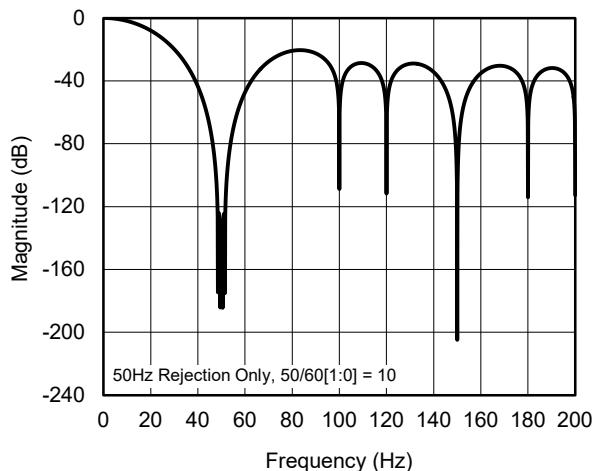

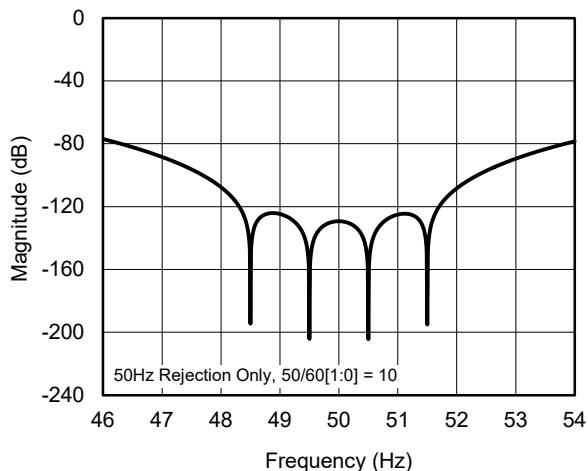

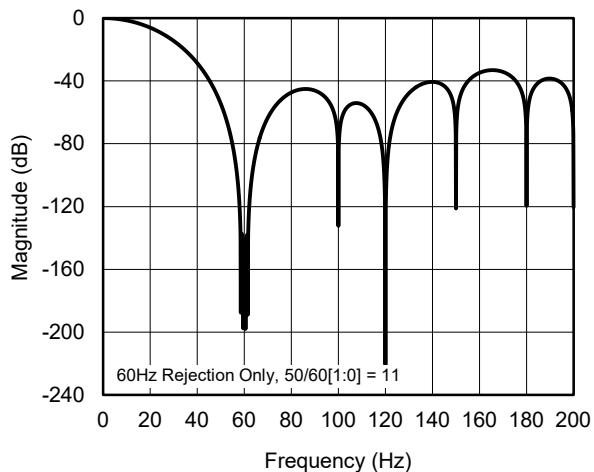

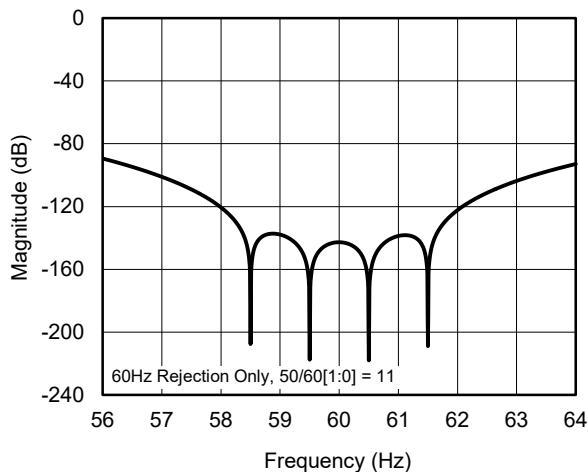

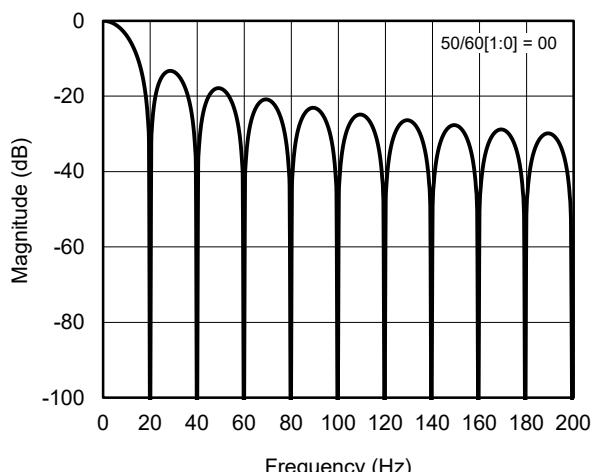

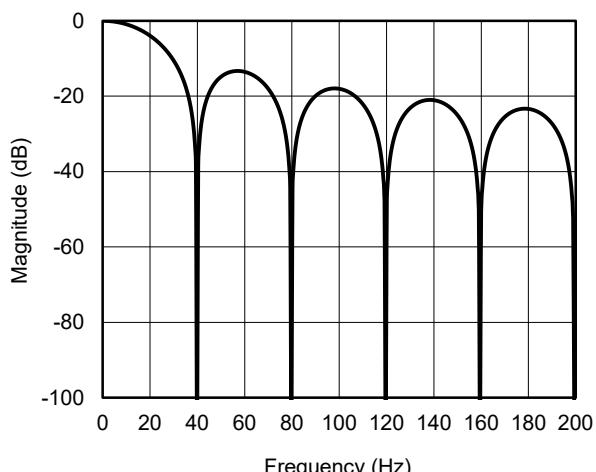

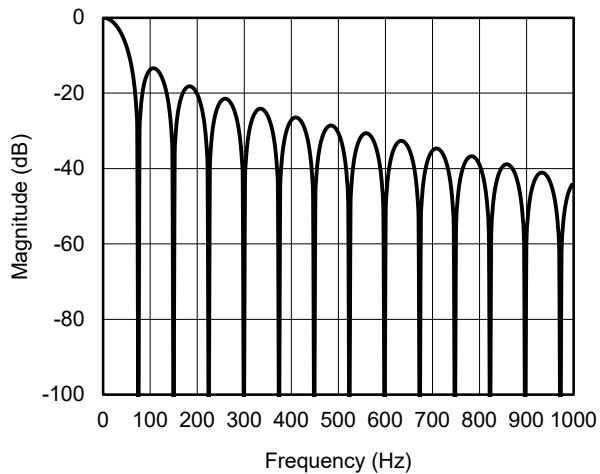

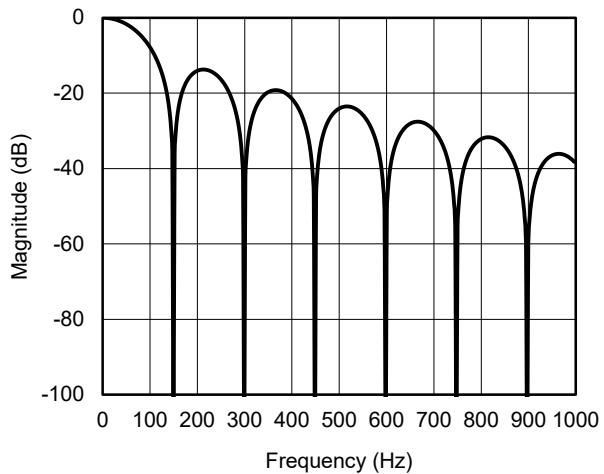

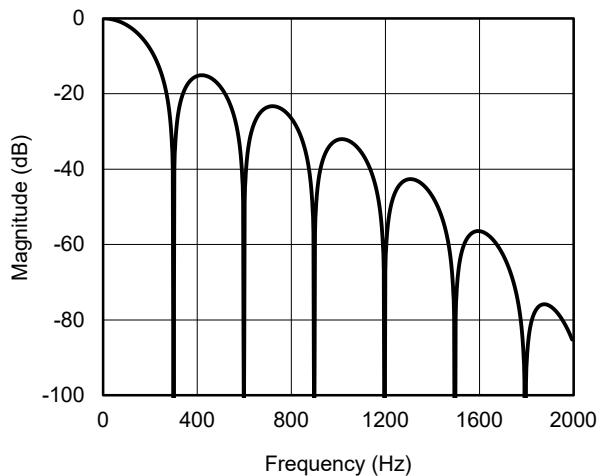

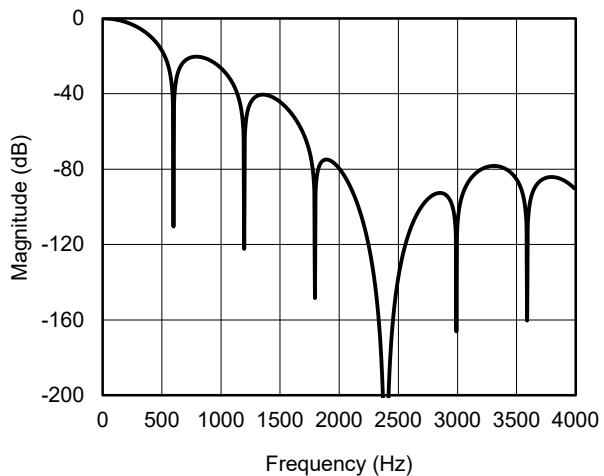

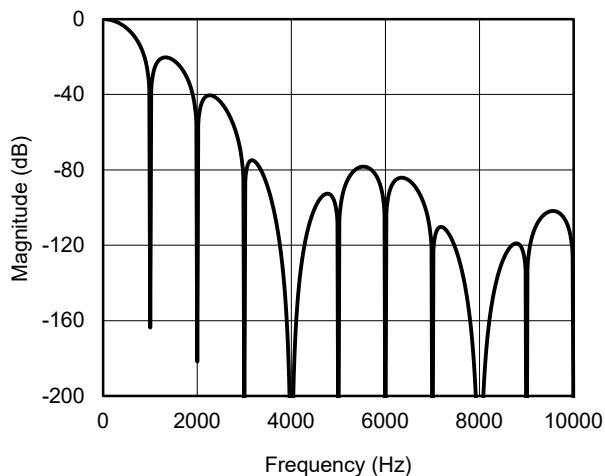

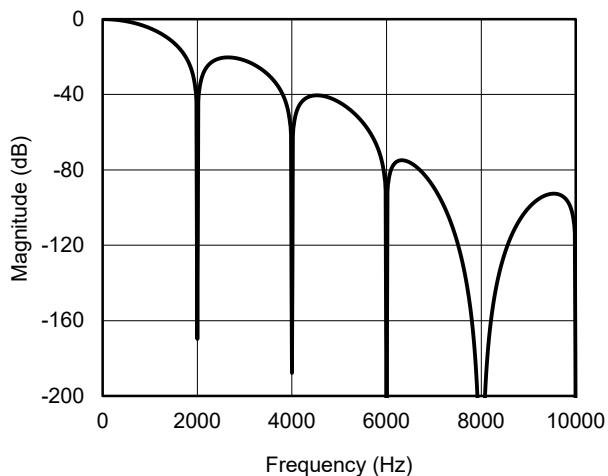

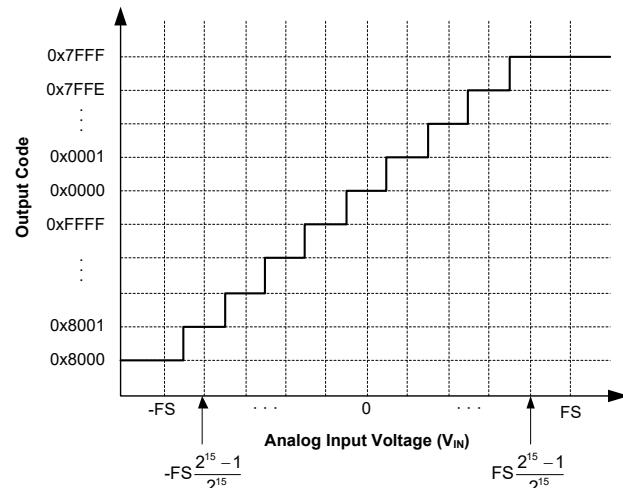

a dual purpose, filtering and decimating the incoming digital data stream from the modulator. Notably, the digital filter automatically adapts to different data rates, ensuring a settling process within a single-cycle. Operating at data rates of 5SPS and 20SPS, the filter configuration provides flexibility to reject either 50Hz or 60Hz line frequencies, or both simultaneously. Two bits (50/60[1:0]) in the configuration register enable easy customization of the filter's behavior. The frequency responses of the digital filter across various output data rates are thoroughly detailed for scenarios involving the internal oscillator or an external 4.096MHz clock, as shown in Figure 11 to Figure 24.

The notching characteristics of the filter and the scaling of output data rates are directly proportional to the clock frequency. For example, a notch that appears at 20Hz with a 4.096MHz clock will shift to 10Hz with a 2.048MHz clock. It is important to note that the internal oscillator is subject to temperature-induced variations, detailed in the Electrical Characteristics table. As a result, the data rate and conversion time vary with these oscillation fluctuations. For applications that require stricter tolerance for a digital filter notch at a specific frequency, considering an external precision clock source is advisable.

**Figure 11. Filter Response (DR = 20SPS)**

**Figure 12. Detailed View of Filter Response (DR = 20SPS)**

## DETAILED DESCRIPTION (continued)

Figure 13. Filter Response (DR = 20SPS)

Figure 14. Detailed View of Filter Response (DR = 20SPS)

Figure 15. Filter Response (DR = 20SPS)

Figure 16. Detailed View of Filter Response (DR = 20SPS)

Figure 17. Filter Response (DR = 20SPS)

Figure 18. Filter Response (DR = 40SPS)

## DETAILED DESCRIPTION (continued)

Figure 19. Filter Response (DR = 75SPS)

Figure 20. Filter Response (DR = 150SPS)

Figure 21. Filter Response (DR = 300SPS)

Figure 22. Filter Response (DR = 600SPS)

Figure 23. Filter Response (DR = 1kSPS)

Figure 24. Filter Response (DR = 2kSPS)

## DETAILED DESCRIPTION (continued)

## Output Data Rate

The effective conversion times for each specified data rate configuration are shown in Table 11, expressed in terms of  $t_{CLK}$  cycles, assuming an external clock with a frequency of  $f_{CLK} = 4.096\text{MHz}$ .

In continuous conversion mode, the data rate sequence is measured from one falling edge of nDRDY to the next nDRDY falling edge. The first conversion begins either  $210 \cdot t_{CLK}$  cycles (normal mode, duty-cycle mode) or  $114 \cdot t_{CLK}$  cycles (turbo mode) after the final SCLK falling edge of the START/SYNC command.

For single-shot mode, the data rate sequence is measured from the last SCLK falling edge of the START/SYNC command to the upcoming nDRDY falling edge, rounded up to the next  $t_{CLK}$  cycle. If the internal oscillator is in use, an additional time is needed to accommodate the oscillator's wake-up period, which can be up to  $50\mu\text{s}$  (normal mode, duty-cycle mode) or  $25\mu\text{s}$  (turbo mode) in single-shot mode. The wake-up process of the internal oscillator starts with the

initial SCLK rising edge of the START/SYNC command. If the SCLK frequency exceeds 160kHz (normal mode, duty-cycle mode) or 320kHz (turbo mode), there is a chance that the internal oscillator may not be fully operational by the end of the START/SYNC command. In such cases, the ADC waits for the internal oscillator to fully power up before initiating a conversion.

It is important to note that while the conversion time for the 20SPS setting is not precisely equal to  $1/20\text{Hz} = 50\text{ms}$ , this deviation does not apply any influence on the specified 50Hz or 60Hz rejection performance. For the accomplishment of the specified 50Hz and 60Hz rejection levels listed in the Electrical Characteristics table, a requisite condition necessitates the external clock frequency to be set at 4.096MHz. Conversely, in scenarios where the internal oscillator is utilized, the conversion time and filter notching characteristics exhibit variations corresponding to the figures detailed in the Electrical Characteristics table, accounting for oscillator accuracy considerations.

Table 11. Conversion Times

| Nominal Data Rate (SPS) | -3dB Bandwidth (Hz) | Actual Conversion Time ( $t_{CLK}$ ) |                  |

|-------------------------|---------------------|--------------------------------------|------------------|

|                         |                     | Continuous Conversion Mode           | Single-Shot Mode |

| <b>Normal Mode</b>      |                     |                                      |                  |

| 20                      | 8.8                 | 205439                               | 206262           |

| 40                      | 17.6                | 102719                               | 103543           |

| 75                      | 33                  | 54784                                | 55607            |

| 150                     | 66                  | 27390                                | 28217            |

| 300                     | 130                 | 13693                                | 14516            |

| 600                     | 240                 | 6824                                 | 7696             |

| 1000                    | 400                 | 4071                                 | 4944             |

| <b>Duty-Cycle Mode</b>  |                     |                                      |                  |

| 5                       | 8.8                 | 819597                               | 206262           |

| 10                      | 17.6                | 409887                               | 103543           |

| 18.75                   | 33                  | 218735                               | 55607            |

| 37.5                    | 66                  | 109519                               | 28213            |

| 75                      | 130                 | 54895                                | 14520            |

| 150                     | 240                 | 27591                                | 7696             |

| 250                     | 400                 | 16663                                | 4944             |

| <b>Turbo Mode</b>       |                     |                                      |                  |

| 40                      | 17.6                | 102719                               | 103166           |

| 80                      | 35.2                | 51360                                | 51806            |

| 150                     | 66                  | 27390                                | 27841            |

| 300                     | 132                 | 13693                                | 14143            |