## **SGM51610S**

# Low-Power, SPI-Compatible, 16-Bit ADC with Internal Reference and Temperature Sensor

#### GENERAL DESCRIPTION

The SGM51610S is a highly precise and efficient 16-bit analog-to-digital converter (ADC) that has been designed to meet the needs of modern sensor measurement applications. The ADC is available in a Green MSOP-10 package or UTQFN-2×1.5-10L package and comes equipped with all the essential features necessary for measuring common sensor signals. These features include a programmable gain amplifier (PGA), voltage reference, oscillator, and high-accuracy temperature sensor. With a wide power supply range of 2V to 5.5V, the SGM51610S is ideal for space and power-constrained applications that demand precision and efficiency.

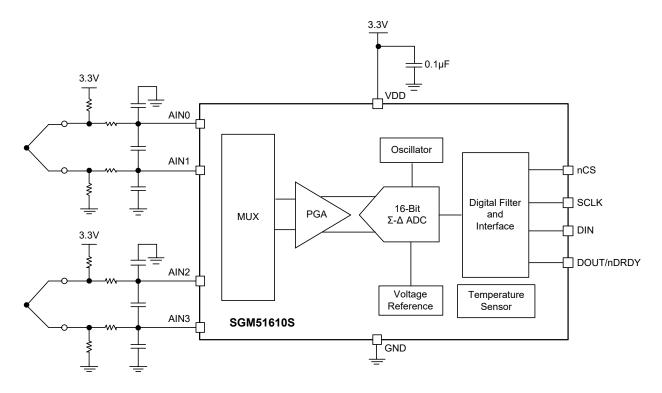

The SGM51610S can achieve conversion rates of up to 960 samples per second (SPS) with single-cycle settling. The ADC features a programmable gain amplifier (PGA) that supports input ranges from ±256mV to ±6.144V, enabling accurate measurement of both large and small signals with high resolution. In addition, the input multiplexer (MUX) allows for the measurement of two differential or four single-ended inputs. The SGM51610S also comes equipped with a high-precision temperature sensor that can be used for system-level temperature monitoring or cold junction compensation for thermocouples.

The SGM51610S can operate in either continuous conversion mode or single-shot mode, which automatically powers down after a conversion to significantly reduce current consumption during idle periods. The SGM51610S is designed to operate within a temperature range of -40°C to +125°C, making them suitable for use in a wide range of applications.

#### **FEATURES**

- Four Single-Ended or Two Differential Inputs

- Wide Supply Range: 2V to 5.5V

- Low Current Consumption:

- Continuous Mode: 207µA (TYP)

- Single-Shot Mode: Automatic Power-Down

- Programmable Output Data Rate:

- 5SPS to 960SPS

- Single-Cycle Settling

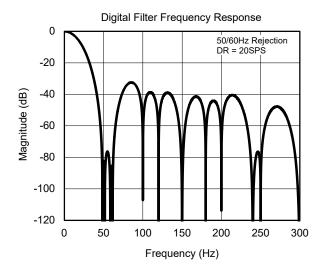

- 50/60Hz Line Rejection

- Robust Encryption for Factory Mode Entry

- Internal PGA

- Internal Oscillator

- Internal Low-Drift Voltage Reference

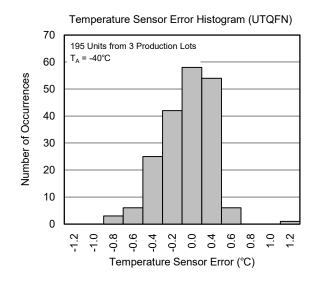

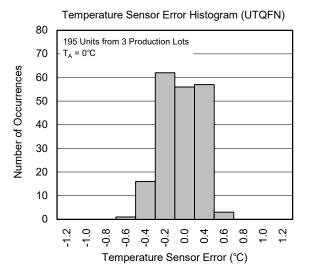

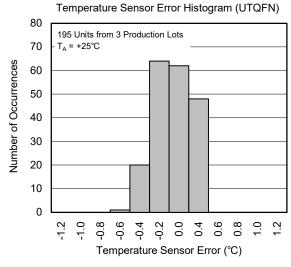

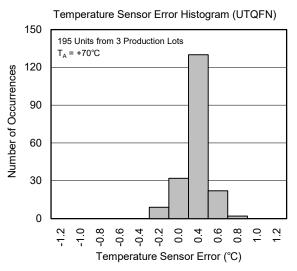

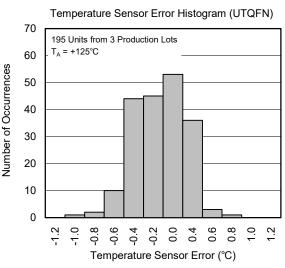

- Internal Temperature Sensor:

0.2°C (TYP) Error at 0°C to 70°C

- Available in Green MSOP-10 and UTQFN-2×1.5-10L Packages

#### **APPLICATIONS**

Automotive Applications

Battery Current Measurement

BMS Insulation Detection

HMI

**Temperature Measurement**

Thermocouple with Cold Junction Compensation

**Thermistor Measurement**

Portable Instrumentation

**Process Controls and Factory Automation**

#### PACKAGE/ORDERING INFORMATION

| MODEL           | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER   | PACKAGE<br>MARKING       | PACKING<br>OPTION   |

|-----------------|------------------------|-----------------------------------|----------------------|--------------------------|---------------------|

|                 | MSOD 10                | -40°C to +125°C                   | SGM51610SXMS10G/TR   | SGM1AP<br>XMS10<br>XXXXX | Tape and Reel, 4000 |

| SGM51610S       | MSOP-10<br>GM51610S    | -40 C to +125 C                   | SGM51610SXMS10SG/TR  | SGM1AP<br>XMS10<br>XXXXX | Tape and Reel, 500  |

|                 | LITOEN 2×1 5 101       | -40°C to +125°C                   | SGM51610SXURA10G/TR  | 1AN<br>XXXX              | Tape and Reel, 3000 |

| UTQFN-2×1.5-10l | 01QFN-2*1.5-10L        |                                   | SGM51610SXURA10SG/TR | 1AN<br>XXXX              | Tape and Reel, 500  |

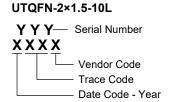

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code. XXXX = Date Code, Trace Code and Vendor Code.

X X X X

Vendor Code

Trace Code

Date Code - Year

MSOP-10

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### ABSOLUTE MAXIMUM RATINGS

| Power Supply Voltage Range (VDD to GND)0.3V to 7V                  |

|--------------------------------------------------------------------|

| Analog Input Voltage Range (AIN0, AIN1, AIN2, AIN3)                |

| GND - 0.3V to V <sub>DD</sub> + 0.3V                               |

| Digital Input Voltage Range (DIN, DOUT/nDRDY, SCLK, nCS)           |

| GND - 0.3V to V <sub>DD</sub> + 0.3V                               |

| Input Current, Continuous (Any Pin except Power Supply Pins)       |

| -10mA to 10mA                                                      |

| Package Thermal Resistance                                         |

| MSOP-10, θ <sub>JA</sub>                                           |

| MSOP-10, θ <sub>JB</sub> 92.4°C/W                                  |

| MSOP-10, θ <sub>JC</sub>                                           |

| UTQFN-2×1.5-10L, θ <sub>JA</sub> 82.4°C/W                          |

| UTQFN-2×1.5-10L, θ <sub>JB</sub>                                   |

| UTQFN-2×1.5-10L, θ <sub>JC</sub>                                   |

| Junction Temperature+150°C                                         |

| Storage Temperature Range65°C to +150°C                            |

| Lead Temperature (Soldering, 10s)+260°C ESD Susceptibility (1) (2) |

| HBM±4000V                                                          |

| CDM±1000V                                                          |

| ±1000V                                                             |

#### NOTES:

- 1. For human body model (HBM), all pins comply with ANSI/ESDA/JEDEC JS-001 specifications.

- 2. For charged device model (CDM), all pins comply with ANSI/ESDA/JEDEC JS-002 specifications.

#### RECOMMENDED OPERATING CONDITIONS

| Power Supply Voltage (VDD to GND), V <sub>DD</sub>          |                        |

|-------------------------------------------------------------|------------------------|

| Full-Scale Input Voltage Range (3) (4) (V <sub>IN</sub> = V | AINP - VAINN), FSR     |

|                                                             | See Table 4            |

| Absolute Input Voltage Range, VAINX                         | GND to V <sub>DD</sub> |

| Digital Input Voltage Range                                 | GND to V <sub>DD</sub> |

| Operating Temperature Range                                 | -40°C to +125°C        |

|                                                             |                        |

#### NOTES:

- 3.  $AIN_P$  and  $AIN_N$  refer to the chosen positive and negative inputs respectively, while  $AIN_x$  represents any of the four analog inputs that are available.

- 4. The ADC scaling's full-scale range is indicated by this parameter. It is essential to ensure that no more than  $V_{DD}$  + 0.3V or 5.5V (whichever is lower) is applied to the device.

#### **SGM51610S**

# Low-Power, SPI-Compatible, 16-Bit ADC with Internal Reference and Temperature Sensor

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all

integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

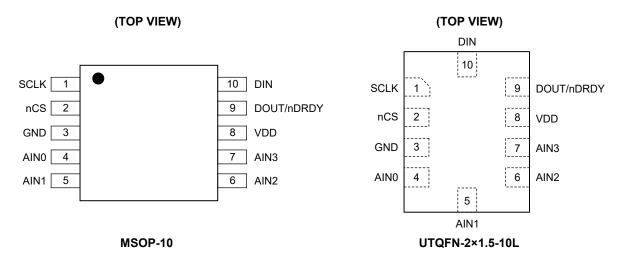

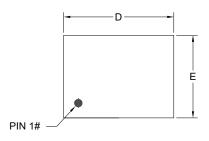

#### PIN CONFIGURATIONS

## **PIN DESCRIPTION**

| PIN | NAME       | TYPE | FUNCTION                                                                         |

|-----|------------|------|----------------------------------------------------------------------------------|

| 1   | SCLK       | DI   | Serial Clock Input.                                                              |

| 2   | nCS        | DI   | Chip Select. Active low. Tie to GND if unused.                                   |

| 3   | GND        | G    | Ground.                                                                          |

| 4   | AIN0       | Al   | Analog Input 0. Keep float or connect to VDD if unused.                          |

| 5   | AIN1       | Al   | Analog Input 1. Keep float or connect to VDD if unused.                          |

| 6   | AIN2       | Al   | Analog Input 2. Keep float or connect to VDD if unused.                          |

| 7   | AIN3       | Al   | Analog Input 3. Keep float or connect to VDD if unused.                          |

| 8   | VDD        | Р    | Power Supply. A 100nF decoupling capacitor is required from power supply to GND. |

| 9   | DOUT/nDRDY | DO   | Serial Data Output Combined with Data Ready. Active low.                         |

| 10  | DIN        | DI   | Serial Data Input.                                                               |

NOTE: DI = digital input, DO = digital output, AI = analog input, P = power, G = ground.

## **ELECTRICAL CHARACTERISTICS**

$(V_{DD}$  = 3.3V, Data Rate (DR) = 5SPS, and Full-Scale Range (FSR) = ±2.048V,  $T_A$  = -40°C to +125°C, typical values are at  $T_A$  = +25°C, unless otherwise noted.)

| PARAMETER                     | SYMBOL         | CONDITIONS                                            |                         | MIN       | TYP            | MAX                   | UNITS  |

|-------------------------------|----------------|-------------------------------------------------------|-------------------------|-----------|----------------|-----------------------|--------|

| Analog Inputs                 |                | •                                                     |                         |           |                |                       |        |

| Full-Scale Input Voltage (1)  |                | V <sub>IN</sub> = AIN <sub>P</sub> - AIN <sub>N</sub> |                         |           | ±4.096/PGA     |                       | V      |

| Analog Input Voltage          |                | AIN <sub>P</sub> or AIN <sub>N</sub> to G             | SND                     | GND - 0.1 |                | V <sub>DD</sub> + 0.1 | V      |

| Differential Input Impedance  |                |                                                       |                         |           | See Table 3    |                       |        |

| System Performance            |                |                                                       |                         |           |                |                       |        |

| Resolution                    |                | No missing codes                                      | S                       | 16        |                |                       | Bits   |

| Data Rate                     | DR             |                                                       |                         |           | See Table 5    |                       | SPS    |

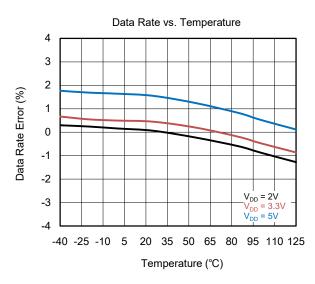

| Data Rate Variation           |                | All data rates                                        |                         | -4        |                | 4                     | %      |

| Output Noise                  |                |                                                       |                         | Se        | e Noise Perfor | mance sectio          | n      |

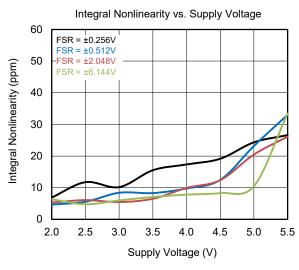

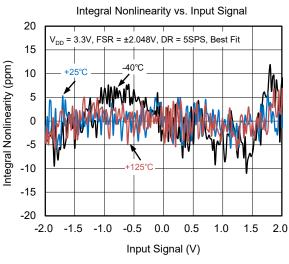

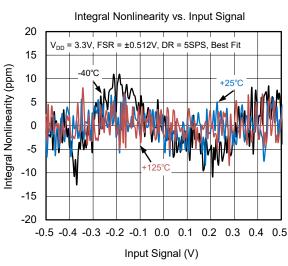

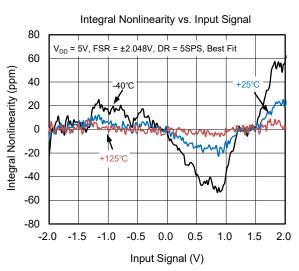

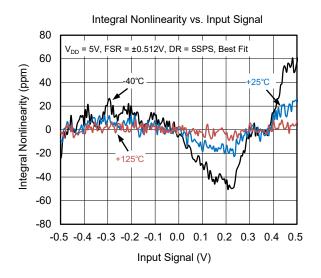

| Integral Nonlinearity         | INL            | DR = 5SPS, FSR                                        | R = ±2.048V (2)         |           | 0.7            | 4                     | LSB    |

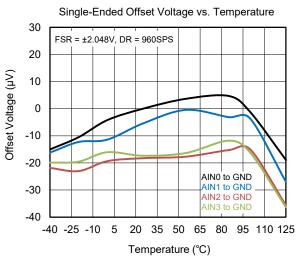

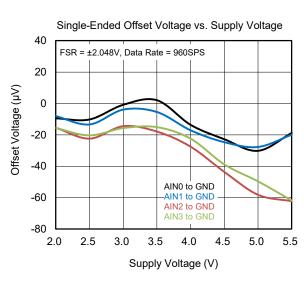

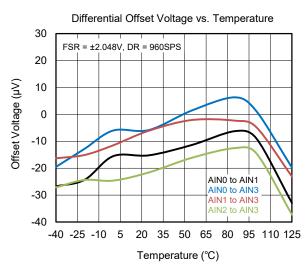

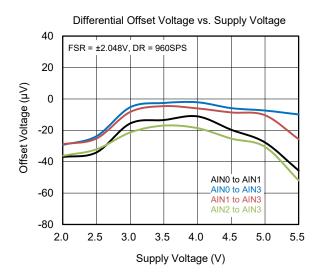

| Offset Error                  | F              | FSR = ±2.048V                                         | Differential inputs     |           | 0.1            | ±5                    | LCD    |

| Oliset Error                  | Eo             | FSR - ±2.046V                                         | Single-ended inputs     |           | 0.7            |                       | LSB    |

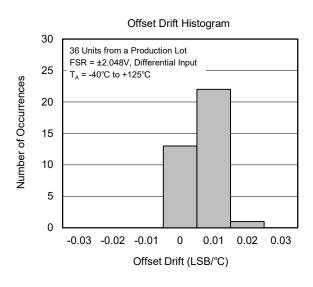

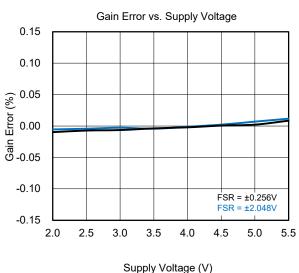

| Offset Drift                  |                | FSR = ±2.048V                                         |                         |           | 0.004          |                       | LSB/°C |

| Offset Power Supply Rejection |                | FSR = ±2.048V                                         |                         |           | 0.3            |                       | LSB/V  |

| Offset Channel Match          |                | Match between a inputs                                | ny two differential     |           | 0.1            |                       | LSB    |

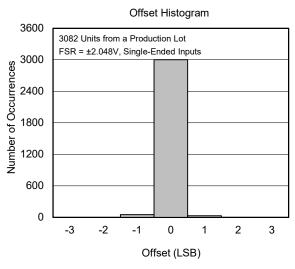

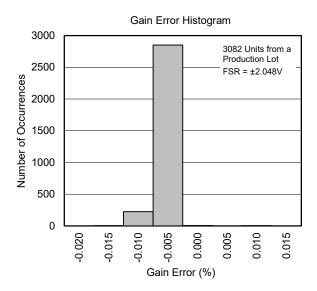

| Gain Error (3)                | E <sub>G</sub> | FSR = ±2.048V, 7                                      | Γ <sub>A</sub> = +25°C  |           | 0.01           | 0.15                  | %      |

|                               |                | FSR = ±0.256V<br>FSR = ±2.048V                        |                         |           | 5              |                       | ppm/°C |

| Gain Drift (3)(4)             |                |                                                       |                         |           | 5              | 15                    |        |

|                               |                | FSR = ±6.144V (1                                      | 1)                      |           | 5              |                       |        |

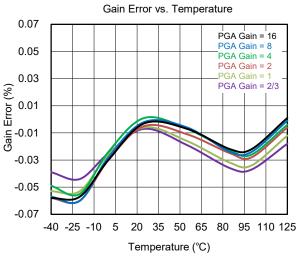

| Gain Power Supply Rejection   |                |                                                       |                         |           | 45             |                       | ppm/V  |

| Gain Match (3)                |                | Match between a                                       | ny two PGA gains        |           | 0.01           | 0.1                   | %      |

| Gain Channel Match            |                | Match between a                                       | ny two inputs           |           | 0.01           | 0.1                   | %      |

|                               |                | At DC, FSR = ±2                                       | .048V                   |           | 118            |                       |        |

| Common Mode Poinction Potio   | CMRR           | At DC, FSR = ±6.                                      | .144V <sup>(1)</sup>    |           | 115            |                       | dB     |

| Common Mode Rejection Ratio   | CIVIRK         | f <sub>CM</sub> = 50Hz, DR =                          | 960SPS                  |           | 104            |                       |        |

|                               |                | f <sub>CM</sub> = 60Hz, DR =                          | 960SPS                  |           | 104            |                       |        |

| Normal Mode Rejection Ratio   | NMRR           | ODR = 10SPS, 5                                        | ODR = 10SPS, 50Hz ± 1Hz |           | 95             |                       | dB     |

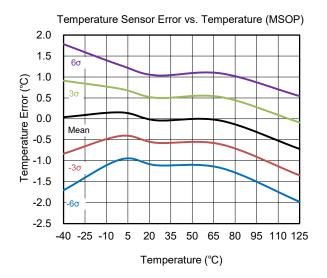

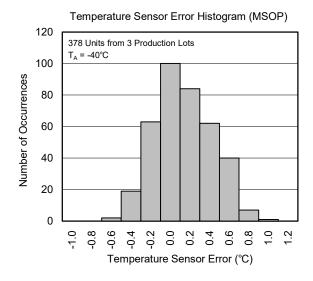

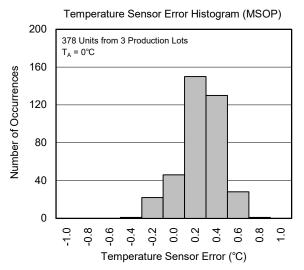

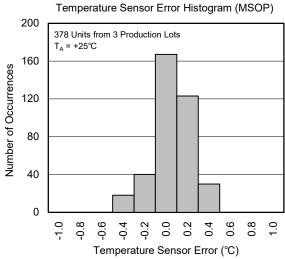

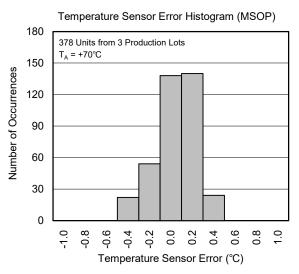

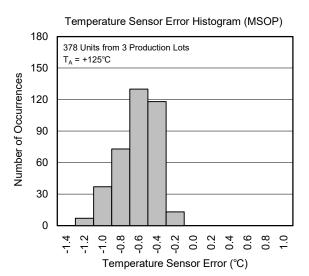

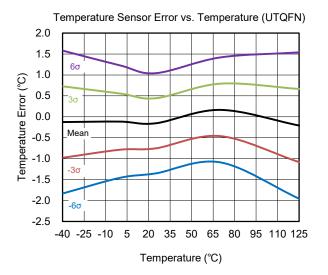

| Temperature Sensor            |                |                                                       |                         |           |                |                       |        |

| Temperature Range             |                |                                                       |                         | -40       |                | 125                   | °C     |

| Temperature Resolution        |                |                                                       |                         |           | 0.03125        |                       | °C/LSB |

|                               |                | $T_A = 0^{\circ}C \text{ to } +70^{\circ}C$           | C                       |           | 0.2            | ±1.5                  | 90     |

| Accuracy                      |                | $T_A = -40^{\circ}C \text{ to } +12^{\circ}$          | 25°C                    |           | 0.7            | ±2                    | °C     |

|                               |                | vs. supply                                            |                         |           | 0.1            | ±1                    | °C/V   |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 3.3V, Data Rate (DR) = 5SPS, and Full-Scale Range (FSR) = \pm 2.048V, T_A = -40^{\circ}C to +125^{\circ}C, typical values are at T_A = +25^{\circ}C, unless otherwise noted.)$

| PARAMETER                 | SYMBOL          | CONDITIONS                      | MIN                   | TYP  | MAX                   | UNITS |

|---------------------------|-----------------|---------------------------------|-----------------------|------|-----------------------|-------|

| Digital Inputs/Outputs    |                 |                                 |                       |      | •                     |       |

| High-Level Input Voltage  | V <sub>IH</sub> |                                 | 0.7 × V <sub>DD</sub> |      |                       | V     |

| Low-Level Input Voltage   | V <sub>IL</sub> |                                 |                       |      | 0.2 × V <sub>DD</sub> | V     |

| High-Level Output Voltage | V <sub>OH</sub> |                                 | 0.8 × V <sub>DD</sub> |      |                       | V     |

| Low-Level Output Voltage  | V <sub>OL</sub> |                                 |                       |      | 0.2 × V <sub>DD</sub> | V     |

| High Input Leakage        | I <sub>H</sub>  | V <sub>IH</sub> = 5.5V          | -1                    |      | 1                     | μΑ    |

| Low Input Leakage         | IL              | V <sub>IL</sub> = GND           | -1                    |      | 1                     | μΑ    |

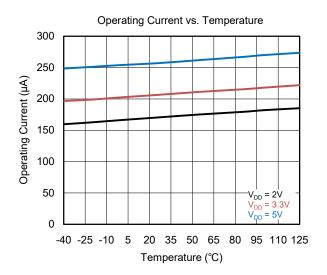

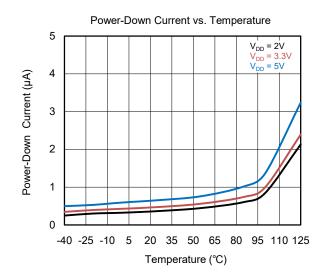

| Power Supply              | ·               |                                 |                       |      |                       |       |

|                           |                 | Power-down current at +25°C     |                       | 0.5  | 1                     |       |

| Cumply Current            |                 | Power-down current up to +125°C |                       |      | 5                     |       |

| Supply Current            | $I_{VDD}$       | Operating current at +25°C      |                       | 207  | 240                   | μA    |

|                           |                 | Operating current up to +125°C  |                       |      | 300                   |       |

|                           |                 | V <sub>DD</sub> = 5V            |                       | 1.30 |                       |       |

| Power Dissipation         | P <sub>D</sub>  | V <sub>DD</sub> = 3.3V          |                       | 0.68 |                       | mW    |

|                           |                 | V <sub>DD</sub> = 2V            |                       | 0.34 |                       |       |

#### NOTES:

- 1. This parameter specifies the maximum range of the ADC scaling. The device should not be subjected to more than  $V_{DD} + 0.3V$  or 5.5V (whichever is lower).

- 2. The best-fit INL is used to cover 99% of the full-scale range.

- 3. The parameter includes all errors originating from the onboard PGA and voltage reference.

- 4. The maximum value is specified by the characterization process.

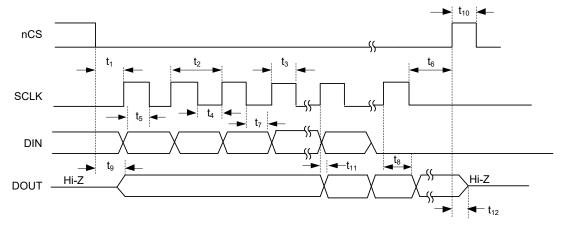

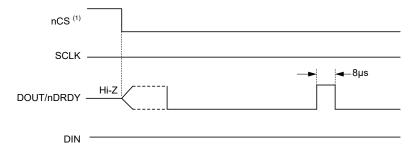

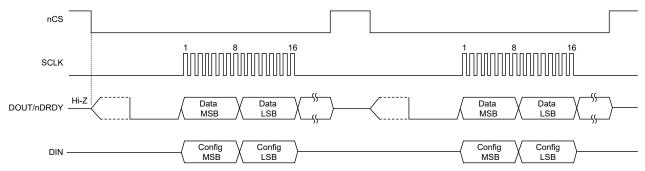

#### **TIMING REQUIREMENTS: SERIAL INTERFACE**

( $V_{DD}$  = 2V to 5.5V,  $T_A$  = -40°C to +125°C, unless otherwise noted.)

| PARAMETER                                                      | SYMBOL                | CONDITIONS | MIN  | TYP | MAX | UNITS |

|----------------------------------------------------------------|-----------------------|------------|------|-----|-----|-------|

| Delay Time, nCS Falling Edge to the First SCLK Rising Edge (1) | t <sub>1</sub>        |            | 100  |     |     | ns    |

| Delay Time, Final SCLK Falling Edge to nCS Rising Edge         | <b>t</b> <sub>6</sub> |            | 1000 |     |     | ns    |

| Pulse Duration, nCS High                                       | t <sub>10</sub>       |            | 200  |     |     | ns    |

| SCLK Period                                                    | t <sub>2</sub>        |            | 350  |     |     | ns    |

| Pulse Duration, SCLK High                                      | t <sub>3</sub>        |            | 250  |     |     | ns    |

| Pulse Duration, SCLK Low (2)                                   | +                     |            | 100  |     |     | ns    |

| Fuise Duration, SCER LOW                                       | $t_4$                 |            |      |     | 28  | ms    |

| Setup Time, DIN Valid before SCLK Falling Edge                 | t <sub>5</sub>        |            | 50   |     |     | ns    |

| Hold Time, DIN Valid after SCLK Falling Edge                   | t <sub>7</sub>        |            | 50   |     |     | ns    |

| Hold Time, SCLK Rising Edge to DOUT Invalid                    | t <sub>8</sub>        |            | 0    |     |     | ns    |

#### NOTES:

- 1. If the serial bus is not shared with any other device, nCS can be permanently tied low.

- 2. Resetting the SPI interface is possible by holding SCLK low for more than 28ms.

## **SWITCHING CHARACTERISTICS: SERIAL INTERFACE**

$(T_A = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted.})$

| PARAMETER                                                      | SYMBOL          | CONDITIONS                       | MIN | TYP | MAX | UNITS |

|----------------------------------------------------------------|-----------------|----------------------------------|-----|-----|-----|-------|

| Propagation Delay Time, nCS Falling Edge to DOUT Driven        | t <sub>9</sub>  | DOUT load = 20pF    100kΩ to GND |     |     | 100 | ns    |

| Propagation Delay Time, SCLK Rising Edge to Valid New DOUT     | t <sub>11</sub> | DOUT load = 20pF    100kΩ to GND | 0   |     | 50  | ns    |

| Propagation Delay Time, nCS Rising Edge to DOUT High Impedance | t <sub>12</sub> | DOUT load = 20pF    100kΩ to GND |     |     | 100 | ns    |

Figure 1. Serial Interface Timing Diagram

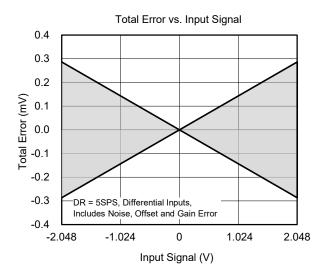

## TYPICAL PERFORMANCE CHARACTERISTICS

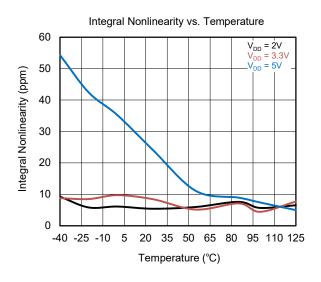

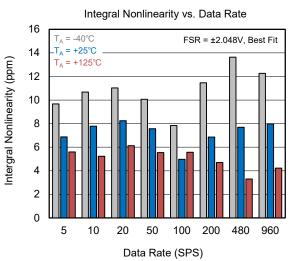

At  $T_A = +25$ °C,  $V_{DD} = 3.3$ V, FSR = ±2.048V, unless otherwise noted.

At  $T_A = +25$ °C,  $V_{DD} = 3.3$ V, FSR =  $\pm 2.048$ V, unless otherwise noted.

At  $T_A = +25$ °C,  $V_{DD} = 3.3$ V, FSR =  $\pm 2.048$ V, unless otherwise noted.

At  $T_A = +25^{\circ}C$ ,  $V_{DD} = 3.3V$ , FSR =  $\pm 2.048V$ , unless otherwise noted.

At  $T_A = +25$ °C,  $V_{DD} = 3.3$ V, FSR =  $\pm 2.048$ V, unless otherwise noted.

At  $T_A$  = +25°C,  $V_{DD}$  = 3.3V, FSR = ±2.048V, unless otherwise noted.

## **APPLICATION CIRCUITS SAMPLE**

Figure 2. Thermocouple Measurement Using Cold-Junction Compensation by Integrated Temperature Sensor

## **FUNCTIONAL BLOCK DIAGRAM**

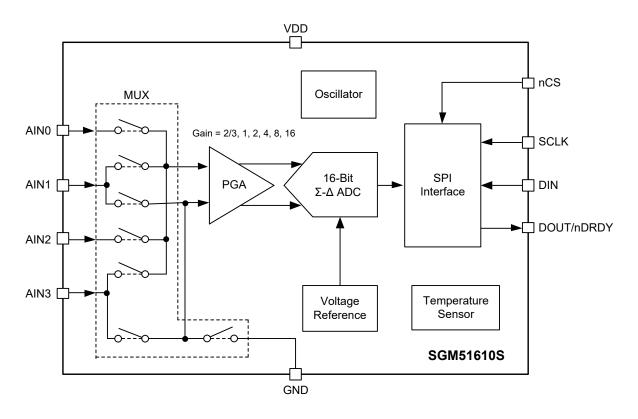

Figure 3. Block Diagram

#### **DETAILED DESCRIPTION**

#### Overview

The SGM51610S is a compact, energy-efficient, 16-bit ADC that utilizes sigma-delta technology. It consists of a core ADC with an adjustable gain, a clock oscillator, an internal voltage reference, and an SPI. Additionally, this device functions as a precise and linear temperature sensor. These features are designed to minimize the need for external circuitry and enhance overall performance. The functional block diagram of the SGM51610S is illustrated in Figure 3.

The SGM51610S provides two unique conversion modes: single-shot and continuous. In single-shot mode, the ADC executes a single conversion of the input signal upon receiving a request, saves the result in an internal Conversion register, and then enters a power-down state. This mode is ideal for systems that require periodic conversions or have long idle periods between conversions, as it significantly reduces power consumption. On the other hand, continuous conversion mode automatically initiates a new conversion of the input signal as soon as the previous one is completed, with the conversion rate matching the programmed data rate. Data can be accessed instantly and will consistently represent the most recently finished conversion.

#### **Noise Performance**

Sigma-delta ( $\Sigma$ - $\Delta$ ) analog-to-digital converters (ADCs) utilize oversampling to function. The input signal of a  $\Sigma$ - $\Delta$  ADC is sampled at a high frequency, known as the modulator frequency. This signal is then filtered and decimated in the digital domain to produce a conversion result at the output data rate. The oversampling ratio (OSR), which is the ratio between the modulator frequency and output data rate, can be adjusted to optimize the ADC's noise performance by increasing the OSR and decreasing the output data rate. With an increase in OSR, a greater number of internal modulator samples are averaged to produce one conversion result, leading to a decrease in input-referred noise furthermore. Amplifying the ADC can also reduce input-referred noise, proving advantageous for measuring low-level signals.

Table 1 and Table 2 provide a concise overview of the device's noise performance, showcasing the typical noise performance at  $T_A$  = +25°C with external shorted inputs. Table 1 exhibits the input-referred noise in  $\mu$ VRMS units, accompanied by  $\mu$ V<sub>PP</sub> values in parentheses, while Table 2 showcases the corresponding data in effective number of bits (ENOB) derived from  $\mu$ VRMS values using Equation 1. The noise-free bits, determined from peak-to-peak noise values using Equation 2, are displayed in parentheses.

ENOB =

$$\ln (FSR/V_{RMS-Noise})/\ln (2)$$

(1)

Noise-Free Bits =

$$\ln (FSR/V_{PP-Noise})/\ln (2)$$

(2)

Table 1. Noise with Internal Reference (RMS in µV)

| DR<br>FS (V) | 960   | 480   | 200   | 100   | 50    | 20    | 10    | 5     |

|--------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 6.144        | 187.5 | 187.5 | 187.5 | 187.5 | 187.5 | 187.5 | 187.5 | 187.5 |

| 4.096        | 125   | 125   | 125   | 125   | 125   | 125   | 125   | 125   |

| 2.048        | 62.5  | 62.5  | 62.5  | 62.5  | 62.5  | 62.5  | 62.5  | 62.5  |

| 1.024        | 31.25 | 31.25 | 31.25 | 31.25 | 31.25 | 31.25 | 31.25 | 31.25 |

| 0.512        | 15.62 | 15.62 | 15.62 | 15.62 | 15.62 | 15.62 | 15.62 | 15.62 |

| 0.256        | 7.81  | 7.81  | 7.81  | 7.81  | 7.81  | 7.81  | 7.81  | 7.81  |

Table 2. ADC ENOB (ENOB = In (FSR/V<sub>RMS-Noise</sub>)/In (2))

| Table 2. ADC | Table 2. ADC ENOB (ENOB - III (F3R/V <sub>RMS-Noise</sub> )/III (2)) |     |     |     |    |    |    |    |

|--------------|----------------------------------------------------------------------|-----|-----|-----|----|----|----|----|

| DR<br>FS (V) | 960                                                                  | 480 | 200 | 100 | 50 | 20 | 10 | 5  |

| 6.144        | 16                                                                   | 16  | 16  | 16  | 16 | 16 | 16 | 16 |

| 4.096        | 16                                                                   | 16  | 16  | 16  | 16 | 16 | 16 | 16 |

| 2.048        | 16                                                                   | 16  | 16  | 16  | 16 | 16 | 16 | 16 |

| 1.024        | 16                                                                   | 16  | 16  | 16  | 16 | 16 | 16 | 16 |

| 0.512        | 16                                                                   | 16  | 16  | 16  | 16 | 16 | 16 | 16 |

| 0.256        | 16                                                                   | 16  | 16  | 16  | 16 | 16 | 16 | 16 |

#### Multiplexer

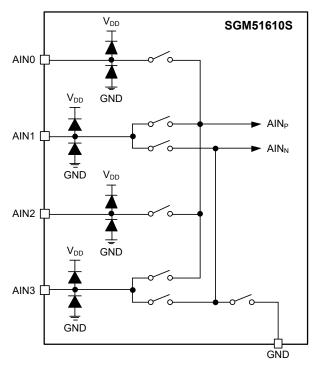

The SGM51610S has an input multiplexer (MUX) shown in Figure 4, which can measure up to four single-ended or two differential signals. Additionally, the differential measurement of AIN0, AIN1, and AIN2 to AIN3 is possible. The MUX[2:0] bits in the Config register are responsible for configuring the multiplexer. In the case of single-ended signals, the ADC's negative input is internally connected to GND via the multiplexer's switch.

Figure 4. Input Multiplexer

In the event of measuring single-ended inputs, negative codes are not generated by the device, as they signify negative differential signals where  $(V_{AINP} - V_{AINN}) < 0$ . The SGM51610S inputs are safeguarded by ESD diodes to VDD and GND. To prevent the activation of ESD diodes, it is crucial to keep the voltage on each input within the specified limits defined in Equation 3.

$$GND - 0.3V < V_{AINx} < V_{DD} + 0.3V$$

(3)

If there is a possibility of the voltages on the input pins violating these conditions, it is advisable to use external Schottky diodes and series resistors to limit the input current to safe levels, as stated in the Absolute Maximum Ratings table. Overdriving an unused input on the SGM51610S can affect ongoing conversions on other input pins, so if overdriving unused inputs cannot be avoided, it is recommended to use external Schottky diodes to control the signal.

#### **Analog Inputs**

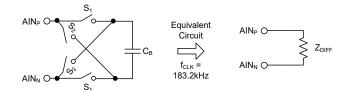

The SGM51610S has a switched capacitor input stage. There are charge and discharge current when ADC is working. The equal effective input impedance can be estimated by  $R_{\text{EFF}} = V_{\text{IN}}/I_{\text{AVERAGE}}$ .

The differential input impedance is  $Z_{DIFF}$  in Figure 5. Table 3 shows the typical differential input impedance.

Figure 5. Simplified Analog Input Circuit

Table 3. Differential Input Impedance

| Table 3. Differential input impedance |                                   |  |  |  |  |  |

|---------------------------------------|-----------------------------------|--|--|--|--|--|

| FS (V)                                | Differential Input Impedance (MΩ) |  |  |  |  |  |

| ±6.144 <sup>(1)</sup>                 | 3.3                               |  |  |  |  |  |

| ±4.096 <sup>(1)</sup>                 | 2.7                               |  |  |  |  |  |

| ±2.048                                | 1.8                               |  |  |  |  |  |

| ±1.024                                | 1.8                               |  |  |  |  |  |

| ±0.512                                | 1                                 |  |  |  |  |  |

| ±0.256                                | 0.6                               |  |  |  |  |  |

#### NOTE:

1. FS = Full-scale range of the ADC scaling. In any event, it should not exceed  $V_{DD}$  + 0.3V applied to this device.

#### **Full-Scale Input**

The SGM51610S has an internal PGA. The PGA can be set to gains of 2/3, 1, 2, 4, 8 or 16. Table 4 shows the corresponding full-scale (FS) ranges. Analog input voltages can never exceed the analog input voltage limits.

Table 4. PGA Gain Full-Scale Range with Internal Reference

| PGA Setting | FS (V)                |

|-------------|-----------------------|

| 2/3         | ±6.144 <sup>(1)</sup> |

| 1           | ±4.096 <sup>(1)</sup> |

| 2           | ±2.048                |

| 4           | ±1.024                |

| 8           | ±0.512                |

| 16          | ±0.256                |

#### NOTE:

1. FS = Full-scale range of the ADC scaling. In any event, it should not exceed  $V_{DD}$  + 0.3V applied to this device.

#### **Output Data Rate (ODR)**

Table 5. ADC Output Data Rate (SPS)

| DR[2:0] Bits       |          |  |  |  |  |

|--------------------|----------|--|--|--|--|

| in Config Register | ODR (Hz) |  |  |  |  |

| 000                | 5        |  |  |  |  |

| 001                | 10       |  |  |  |  |

| 010                | 20       |  |  |  |  |

| 011                | 50       |  |  |  |  |

| 100                | 100      |  |  |  |  |

| 101                | 200      |  |  |  |  |

| 110                | 480      |  |  |  |  |

| 111                | 960      |  |  |  |  |

#### **Voltage Reference**

The SGM51610S features an integrated voltage reference, and it is unsuitable for use with an external reference. The gain error and gain drift specifications in the Electrical Characteristics section take into consideration any errors related to the initial voltage reference accuracy and reference drift with temperature.

#### Internal Oscillator

The SGM51610S comes equipped with an integrated oscillator that runs at 1MHz, eliminating the need for an external clock to operate the device. However, it is important to note that the internal oscillator may experience drift over time and temperature. The output data rate will adjust accordingly in proportion to the oscillator frequency.

#### **Temperature Sensor**

The SGM51610S is equipped with an integrated precision temperature sensor. To activate the temperature sensor mode, configure bit TS\_MODE = 1 in the Config register. The temperature data is presented as a 14-bit outcome, aligned to the left within the 16-bit conversion result, with the most significant byte (MSB) being output first. The temperature measurement result can be determined by examining the first 14 bits when reading the two data bytes. Each 14-bit LSB is equivalent to 0.03125°C. Binary two's complement format is used to represent negative numbers, and Table 6 provides an illustration of this representation.

Table 6. 14-Bit Temperature Data Format

| Tomporature (%)  | Digital Output    |      |  |  |  |  |

|------------------|-------------------|------|--|--|--|--|

| Temperature (°C) | Binary            | Hex  |  |  |  |  |

| 128              | 01 0000 0000 0000 | 1000 |  |  |  |  |

| 127.96875        | 00 1111 1111 1111 | 0FFF |  |  |  |  |

| 100              | 00 1100 1000 0000 | 0C80 |  |  |  |  |

| 75               | 00 1001 0110 0000 | 0960 |  |  |  |  |

| 50               | 00 0110 0100 0000 | 0640 |  |  |  |  |

| 25               | 00 0011 0010 0000 | 0320 |  |  |  |  |

| 0.25             | 00 0000 0000 1000 | 0008 |  |  |  |  |

| 0.03125          | 00 0000 0000 0001 | 0001 |  |  |  |  |

| 0                | 00 0000 0000 0000 | 0000 |  |  |  |  |

| -0.25            | 11 1111 1111 1000 | 3FF8 |  |  |  |  |

| -25              | 11 1100 1110 0000 | 3CE0 |  |  |  |  |

| -40              | 11 1011 0000 0000 | 3B00 |  |  |  |  |

## **Converting from Temperature to Digital Codes**

For positive temperatures:

When dealing with positive numbers, there is no need to use two's complement. Instead, the number can be converted to binary code using a 14-bit, left justified format with the most significant bit (MSB) set to 0 to indicate a positive sign.

Example:  $50^{\circ}$ C/(0.03125°C/count) = 1600 = 0640h = 00 0110 0100 0000

For negative temperatures:

To obtain the two's complement of a negative number, invert all the bits of the absolute binary number and add 1, and indicate the negative sign by setting the most significant bit (MSB) to 1.

Example:  $|-25^{\circ}C|/(0.03125^{\circ}C/count) = 800 = 0320h = 0001100100000$

Two's complement format: 11 1100 1101 1111 + 1 = 11 1100 1110 0000

#### **Converting from Digital Codes to Temperature**

To convert from digital codes to temperature, the first step is to check the value of the MSB. If the MSB is 0, the decimal code can be multiplied by  $0.03125\,^{\circ}\mathrm{C}$  to obtain the temperature value. However, if the MSB is 1, the result must be complemented and 1 must be subtracted before multiplying by  $-0.03125\,^{\circ}\mathrm{C}$  to obtain the temperature value.

Example: The device reads back 0960h: 0960h has an MSB = 0.  $0960h \times 0.03125^{\circ}C = 2400 \times 0.03125^{\circ}C = 75^{\circ}C$

Example: The device reads back 3CE0h: 3CE0h has an MSB = 1. Subtract 1 and complement the result: 3CE0h  $\rightarrow$  0320h 0320h  $\times$  (-0.03125°C) = 800  $\times$  (-0.03125°C) = -25°C

## Device Functional Modes Reset and Power-Up

Upon power-up, the SGM51610S undergoes a reset process that results in all bits in the Config register being set to their default values. The default behavior of the SGM51610S is to enter a power-down state upon start-up, where the device interface and digital blocks are active but no data conversions are performed. This initial power-down state is designed to prevent power surges during start-up, particularly for systems with strict power supply requirements.

#### **Operating Modes**

The operating mode of the SGM51610S can be either continuous-conversion or single-shot, and it is determined by the state of the MODE bit in the Config register.

#### Single-Shot Mode and Power-Down

When the MODE bit in the Config register is set to 1, the SGM51610S goes into a power-saving mode and performs a single conversion when the SS bit in the Config register is set to 1. This is the default state when the device is first powered on, but it still responds to commands. The SGM51610S will stay in this power-saving mode until the SS bit is set to 1. Once the SS bit is set, the device powers up, performs a single conversion, and then powers down again. If a conversion is already in progress, setting the SS bit to 1 will have no effect. In order to switch to continuous conversion mode, the MODE bit in the Config register should be set to 0.

#### **Continuous-Conversion Mode**

When the MODE bit in the Config register is set to 0, the SGM51610S operates in continuous-conversion mode, performing conversions continuously. After each conversion, the result is stored in the Conversion register, and the device immediately starts another conversion. To activate the single-shot mode, either set the MODE bit to 1 in the Config register or perform a device reset.

#### **Duty Cycling for Low Power**

Lowering the output data rate of a  $\Sigma$ - $\Delta$  ADC can improve its noise performance because more samples of the internal modulator can be averaged to produce a single conversion result. However, for applications focused on power efficiency, the enhanced noise performance at lower data rates may not be a critical requirement. To address this, the SGM51610S supports duty cycling, which can significantly reduce power consumption by periodically requesting high data rate readings at an effectively lower data rate. For example, an SGM51610S with a data rate set to 960SPS can be instructed by a microcontroller to perform a single-shot conversion every 200ms (5SPS) while in power-down state. Since a conversion at 960SPS takes only about 1.1ms, the SGM51610S can enter power-down state for the remaining 198.9ms. This configuration reduce consumption can power approximately 1/200<sup>th</sup> of what is consumed in continuous conversion mode. The duty cycling rate is entirely up to the master controller and can be adjusted as needed. The SGM51610S also offers lower data rates without duty cycling and improved noise performance if required.

## Programming Serial Interface

The SPI-compatible serial interface can be configured with either four signals (nCS, SCLK, DIN, and DOUT/nDRDY) or three signals (with nCS tied low). This interface enables various functions including reading conversion data, reading and writing registers, and controlling device operation.

#### **Chip Select (nCS)**

The SGM51610S can be selected for SPI communication using the chip select pin (nCS), which is particularly useful when multiple devices share the same serial bus. During communication, nCS should be kept low. Raising nCS resets the serial interface, causing SCLK to be ignored and DOUT/nDRDY to enter a high-impedance state, preventing it from providing data-ready indication. To monitor DOUT/ nDRDY in situations where multiple devices are present, nCS should be lowered periodically. When this occurs, DOUT/nDRDY will either instantly go high to indicate the absence of new data or instantly go low to indicate the presence of new data in the Conversion register, ready for transfer. Data can be transferred without concern about data corruption. Throughout the transmission process, the current result remains locked in the output shift register and remains unchanged until the communication is completed, ensuring data integrity and preventing any potential data corruption.

#### Serial Clock (SCLK)

The SCLK is a Schmitt-triggered input that is responsible for clocking data on the DIN and DOUT/nDRDY pins into and out of the SGM51610S. Although the input features hysteresis, it is recommended to keep SCLK as clean as possible to prevent glitches from accidentally shifting the data. By holding SCLK low for 28ms, the serial interface resets, and a new

communication cycle starts with the next SCLK pulse, providing an opportunity to recover interrupted serial interface transmissions using this time-out feature. When the serial interface is idle, SCLK should be held low.

#### Data Input (DIN)

The DIN pin is used in conjunction with SCLK to transmit data to the SGM51610S. The SGM51610S latches data on DIN during the falling edge of SCLK, with the crucial distinction that the device never actively drives the DIN pin.

#### Data Output and Data Ready (DOUT/nDRDY)

The DOUT/nDRDY pin is utilized in conjunction with SCLK to extract conversion and register data from the SGM51610S. On the SCLK rising edge, the data is shifted out through DOUT/nDRDY. Additionally, DOUT/nDRDY indicates the completion of a conversion and the availability of new data. When new data is ready for retrieval, DOUT/nDRDY transitions low. It can also initiate the reading of data from the SGM51610S by triggering a microcontroller. In continuous-conversion mode, if no data is retrieved from the device, DOUT/nDRDY transitions high 8µs before the next data ready signal (DOUT/nDRDY low). This transition is depicted in Figure 6. It is important to complete the data transfer before DOUT/nDRDY returns high.

When nCS is set to a high state, DOUT/nDRDY is equipped with a weak internal pull-up resistor as a default configuration. By incorporating this functionality, the aim is to reduce the likelihood of DOUT/nDRDY floating around the midsupply level, which could potentially cause leakage current in the master device. To deactivate this pull-up resistor and switch the device to a high-impedance state, the PULL\_UP\_EN bit in the Config register should be set to 0.

#### NOTE:

1. nCS may be held low. When nCS is in a low state, DOUT/nDRDY is also low, indicating the availability of new data.

Figure 6. DOUT/nDRDY Behavior without Data Retrieval in Continuous Conversion Mode

#### **Data Format**

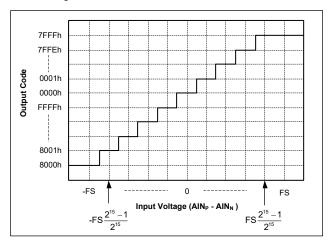

The SGM51610S produces data in a 16-bit binary two's complement format. An input signal at full-scale produces an output code with a positive value of 7FFFh and a negative value of 8000h. When the input signal exceeds full-scale, the output clips at these codes. Table 7 provides an overview of the ideal output codes for various input signals.

Table 7. Input Signal versus Ideal Output Code

| Input Signal, V <sub>IN</sub> (AIN <sub>P</sub> - AIN <sub>N</sub> ) | Ideal Output Code (1) |

|----------------------------------------------------------------------|-----------------------|

| ≥ +FS (2 <sup>15</sup> - 1)/2 <sup>15</sup>                          | 7FFFh                 |

| +FS/2 <sup>15</sup>                                                  | 0001h                 |

| 0                                                                    | 0                     |

| -FS/2 <sup>15</sup>                                                  | FFFFh                 |

| ≤-FS                                                                 | 8000h                 |

#### NOTE:

1. Except for the impact of noise, integral nonlinearity (INL), offset, and gain errors.

Figure 7. Code Transition Diagram

#### **Data Retrieval**

Data transfer to and from the SGM51610S is performed in the same way for both single-shot and continuous conversion modes, without requiring any commands to be issued. The MODE bit in the Config register is used to select the operating mode for the SGM51610S.

To activate continuous-conversion mode, set the MODE bit to 0. In this mode, the device initiates new conversions continuously, even when nCS is high.

Activate single-shot mode by setting the MODE bit to 1, and initiate a new conversion by setting the SS bit to 1.

The conversion data is continuously buffered and remains unchanged until new conversion data replaces it. Therefore, there is no risk of data corruption when reading the data at any time. When DOUT/nDRDY goes low, it indicates the availability of new conversion data. This data is obtained by shifting it out on DOUT/nDRDY, with the most significant bit (bit 15) being clocked out on the first SCLK rising edge. Additionally, new configuration register data is latched on DIN during the SCLK falling edge, simultaneously with the conversion result being clocked out of DOUT/nDRDY.

The SGM51610S offers the added advantage of direct readback of Config register settings within the same data transmission cycle, which can be either 32 bits (when Config register data readback is enabled) or 16 bits (when nCS line is controllable and not tied low permanently).

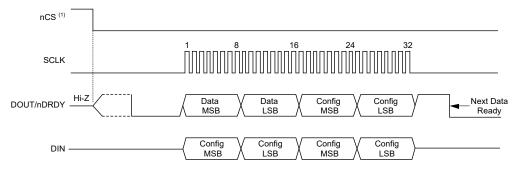

#### 32-Bit Data Transmission Cycle

In a 32-bit data transmission cycle, the data is comprised of four bytes. Two bytes are for the conversion result, and the remaining two bytes are for the Config register readback. The device always reads the most significant byte (MSB) first.

To write the same Config register setting twice within one transmission cycle, follow the procedure shown in Figure 8. During the transmission cycle, it is possible to conveniently write the Config register setting in the first half and then maintain the DIN pin either low or high in the second half, as shown in Figure 9. If there is no need to update the Config register, keep the DIN pin low or high throughout the entire transmission cycle. The Config register setting is written in the initial two bytes of a 32-bit transmission cycle and is subsequently read back in the final two bytes of the same cycle.

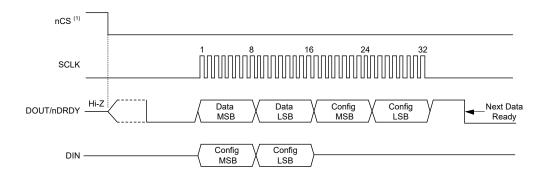

#### 16-Bit Data Transmission Cycle

If the Config register data does not need to be read back, the SGM51610S conversion data can be transmitted in a short 16-bit cycle, as illustrated in Figure 10. It is essential to set nCS high after the 16<sup>th</sup> SCLK cycle to reset the SPI interface. Data transmission begins with the current buffered conversion result on the first rising edge of SCLK when nCS is set low again. If DOUT/nDRDY is low during data retrieval, the conversion buffer has been updated with a new result. However, if DOUT/nDRDY is high, the result from the previous data transmission cycle is read instead.

#### NOTE:

1. If the SGM51610S is the only device on the serial bus, nCS can be kept low. In this case, DOUT/nDRDY will go low to indicate the availability of new data.

Figure 8. 32-Bit Data Transmission Cycle with Config Register Readback

#### NOTE:

1. If the SGM51610S is the only device on the serial bus, nCS can be kept low. In this case, DOUT/nDRDY will go low to indicate the availability of new data.

Figure 9. 32-Bit Data Transmission Cycle: DIN Held Low

Figure 10. 16-Bit Data Transmission Cycle

#### **REGISTER MAPS**

The SGM51610S can be controlled and monitored through the SPI interface, which provides access to two registers. The Conversion register stores the outcome of the latest conversion, while the Config register allows users to modify the device's operating modes and obtain its status information.

#### Conversion Register [Reset = 0x0000]

The Conversion register of the SGM51610S is a 16-bit register that stores the result of the latest conversion in binary two's complement format. When the device is powered on,

the Conversion register is set to 0 and remains at 0 until the first conversion is finished. Table 8 displays the register format.

#### Config1 Register [Reset = 0x058B]

Table 10 displays the details of the 16-bit Config register, which allows users to control various aspects of the SGM51610S operation, such as input selection, data rate, full-scale range, temperature sensor mode, and operating mode.

Table 8. 16-Bit Conversion Register (Read-Only) MSB

LSB

| Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| D15    | D14    | D13    | D12    | D11    | D10    | D9    | D8    | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

**Table 9. Conversion Register Details**

| BITS    | BIT NAME        | DEFAULT | TYPE | DESCRIPTION               |

|---------|-----------------|---------|------|---------------------------|

| D[15:0] | Bit 15 to Bit 0 | 0000h   | R    | 16-bit conversion result. |

Table 10. 16-Bit Config1 Register Details

| BITS     | BIT NAME | DEFAULT | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|----------|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[15]    | SS       | 0       | R/W  | Single-Shot Conversion Start The SS bit is used to initiate a single conversion and can only be modified when the device is powered down, without affecting an ongoing conversion. When writing: 0 = No effect (default) 1 = Start a single conversion (when in power-down state) Always reads back 0 (default).                                                                                                                                                                                                                                                                                                                                |

| D[14:12] | MUX[2:0] | 000     | R/W  | Input Multiplexer Configuration These bits are responsible for configuring the input multiplexer. $000 = AIN_P \text{ is }AIN0 \text{ and }AIN_N \text{ is }AIN1 \text{ (default)}$ $001 = AIN_P \text{ is }AIN0 \text{ and }AIN_N \text{ is }AIN3$ $010 = AIN_P \text{ is }AIN1 \text{ and }AIN_N \text{ is }AIN3$ $011 = AIN_P \text{ is }AIN2 \text{ and }AIN_N \text{ is }AIN3$ $100 = AIN_P \text{ is }AIN0 \text{ and }AIN_N \text{ is }GND$ $101 = AIN_P \text{ is }AIN1 \text{ and }AIN_N \text{ is }GND$ $110 = AIN_P \text{ is }AIN2 \text{ and }AIN_N \text{ is }GND$ $111 = AIN_P \text{ is }AIN3 \text{ and }AIN_N \text{ is }GND$ |

| D[11:9]  | PGA[2:0] | 010     | R/W  | Programmable Gain Amplifier Configuration These bits are responsible for configuring the programmable gain amplifier. 000 = FSR is ±6.144V <sup>(1)</sup> 001 = FSR is ±4.096V <sup>(1)</sup> 010 = FSR is ±2.048V (default) 011 = FSR is ±1.024V 100 = FSR is ±0.512V 101 = FSR is ±0.256V 110 = FSR is ±0.256V 111 = FSR is ±0.256V                                                                                                                                                                                                                                                                                                           |

| D[8]     | MODE     | 1       | R/W  | Device Operating Mode This bit is responsible for controlling the SGM51610S operating mode. 0 = Continuous conversion mode 1 = Power-down and single-shot mode (default)                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

#### NOTE:

1. This parameter specifies the full-scale range of the ADC scaling and indicates the maximum voltage that can be applied to the device, which is  $V_{DD}$  + 0.3V.

## **REGISTER MAPS (continued)**

Table 10. 16-Bit Config1 Register Details (continued)

| BITS   | BIT NAME   | DEFAULT | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|------------|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[7:5] | DR[2:0]    | 100     | R/W  | Data Rate These bits are responsible for controlling the data rate setting. 000 = 5SPS 001 = 10SPS 010 = 20SPS 011 = 50SPS 100 = 100SPS (default) 101 = 200SPS 110 = 480SPS 111 = 960SPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| D[4]   | TS_MODE    | 0       | R/W  | Temperature Sensor Mode This bit is responsible for configuring the ADC to convert temperature or input signals.  0 = ADC mode (default) 1 = Temperature sensor mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| D[3]   | PULL_UP_EN | 1       | R/W  | Pull-Up Enable When the nCS is high, this bit enables a weak internal pull-up resistor specifically on the DOUT/nDRDY pin, connecting the bus line to the power supply with a $400k\Omega$ internal resistor. When disabled, the DOUT/nDRDY pin remains unconnected. $0$ = Pull-up resistor disabled on DOUT/nDRDY pin $1$ = Pull-up resistor enabled on DOUT/nDRDY pin (default)                                                                                                                                                                                                                                                                                                                                                     |

| D[2:1] | NOP[1:0]   | 01      | R/W  | No Operation The NOP[1:0] bits determine whether data is written to the Config register or not, based on their specific configuration. To write data to the Config register, the NOP[1:0] bits must be set to '01'. Any different value will lead to a NOP command. It is possible to hold DIN high or low during SCLK pulses without any data being written to the Config register.  00 = The data is invalid and should not be used to update the contents of the Config register 01 = Valid data, update the Config register (default) 10 = The data is invalid and should not be used to update the contents of the Config register 11 = The data is invalid and should not be used to update the contents of the Config register |

| D[0]   | Reserved   | 1       | R    | Reserved Writing a value of either 0 or 1 to this bit will not have any effect. The bit will always read back as 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

## **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes | from | Original | (APRII | 2025) | to | RFV A  |

|---------|------|----------|--------|-------|----|--------|

| Onanges |      | Original | (A)    | 20201 | w  | 11-4.7 |

Page

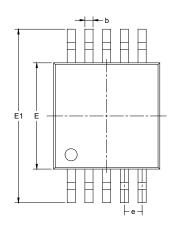

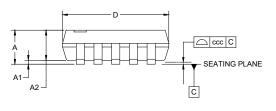

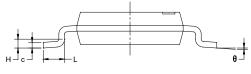

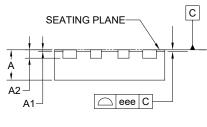

## **PACKAGE OUTLINE DIMENSIONS** MSOP-10

#### RECOMMENDED LAND PATTERN (Unit: mm)

| Cymphal | Di    | Dimensions In Millimeters |       |  |  |  |  |  |  |

|---------|-------|---------------------------|-------|--|--|--|--|--|--|

| Symbol  | MIN   | NOM                       | MAX   |  |  |  |  |  |  |

| Α       | -     | -                         | 1.100 |  |  |  |  |  |  |

| A1      | 0.000 | -                         | 0.150 |  |  |  |  |  |  |

| A2      | 0.750 | -                         | 0.950 |  |  |  |  |  |  |

| b       | 0.170 | 0.170 -                   |       |  |  |  |  |  |  |

| С       | 0.080 | -                         | 0.230 |  |  |  |  |  |  |

| D       | 2.900 | -                         | 3.100 |  |  |  |  |  |  |

| Е       | 2.900 | -                         | 3.100 |  |  |  |  |  |  |

| E1      | 4.750 | -                         | 5.050 |  |  |  |  |  |  |

| е       |       | 0.500 BSC                 |       |  |  |  |  |  |  |

| Н       |       | 0.250 TYP                 |       |  |  |  |  |  |  |

| L       | 0.400 | 0.400 - 0.800             |       |  |  |  |  |  |  |

| θ       | 0°    | 0° - 8°                   |       |  |  |  |  |  |  |

| ccc     | 0.100 |                           |       |  |  |  |  |  |  |

#### NOTES:

- This drawing is subject to change without notice.

The dimensions do not include mold flashes, protrusions or gate burrs.

Reference JEDEC MO-187.

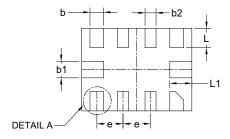

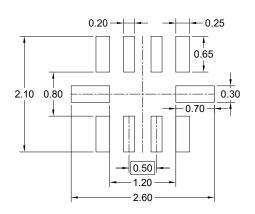

## **PACKAGE OUTLINE DIMENSIONS** UTQFN-2×1.5-10L

#### **TOP VIEW**

#### **SIDE VIEW**

DETAIL A ALTERNATE TERMINAL CONSTRUCTION

#### RECOMMENDED LAND PATTERN (Unit: mm)

| Complete al | Di        | Dimensions In Millimeters |       |  |  |  |  |  |  |

|-------------|-----------|---------------------------|-------|--|--|--|--|--|--|

| Symbol      | MIN       | NOM                       | MAX   |  |  |  |  |  |  |

| Α           | 0.500     | 0.550                     | 0.600 |  |  |  |  |  |  |

| A1          | 0.000     | -                         | 0.050 |  |  |  |  |  |  |

| A2          |           | 0.152 REF                 |       |  |  |  |  |  |  |

| b           | 0.200     | 0.250                     | 0.300 |  |  |  |  |  |  |

| b1          | 0.250     | 0.300                     | 0.350 |  |  |  |  |  |  |

| b2          | 0.150     | 0.200                     | 0.250 |  |  |  |  |  |  |

| D           | 1.900     | 2.000                     | 2.100 |  |  |  |  |  |  |

| Е           | 1.400     | 1.500                     | 1.600 |  |  |  |  |  |  |

| L           | 0.250     | 0.350                     | 0.450 |  |  |  |  |  |  |

| L1          | 0.300     | 0.400                     | 0.500 |  |  |  |  |  |  |

| е           | 0.500 BSC |                           |       |  |  |  |  |  |  |

| eee         |           | 0.050                     |       |  |  |  |  |  |  |

NOTE: This drawing is subject to change without notice.

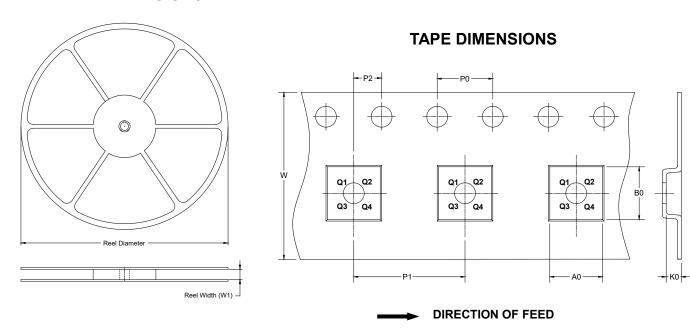

## TAPE AND REEL INFORMATION

#### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type    | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| MSOP-10         | 13"              | 12.4                     | 5.20       | 3.30       | 1.50       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

| UTQFN-2×1.5-10L | 7"               | 9.5                      | 1.70       | 2.30       | 0.75       | 4.0        | 4.0        | 2.0        | 8.0       | Q1               |

## **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type   | Length<br>(mm) |     |     | Pizza/Carton |

|-------------|----------------|-----|-----|--------------|

| 7" (Option) | 368            | 227 | 224 | 8            |

| 7"          | 442            | 410 | 224 | 18           |

| 13"         | 386            | 280 | 370 | 5            |