# SGM7300AN 3.3V, Differential 2-Channel, 2:1 Multiplexer/Demultiplexer Switch

## GENERAL DESCRIPTION

The SGM7300AN is a differential 2-channel switch which can be used for both multiplexer (MUX) and demultiplexer (DEMUX) configurations. The device can be used for PCI Express Generation 3, USB 3.1 and other high-speed serial interface applications.

The product can switch dual differential signals to 1 of 2 locations. The SGM7300AN minimizes the impedance of the switch so that the attenuation observed through the switch can be ignored and minimizes the inter-channel skew and inter-channel crosstalk required for high-speed serial interfaces. The SGM7300AN can achieve extremely low power consumption by extending existing high-speed ports. In order to achieve high ESD tolerance, the ESD protection circuits are integrated into ICs.

The SGM7300AN optimizes the pins to match the product to different application layouts. It is suitable for edge connectors with different signal sources on the motherboard, with input and output pins on opposite sides of the package. The impedances of all Ports are Hi-Z relative to GND pin.

No external DC blocking capacitors are required on the RF paths as long as no external DC voltage is applied, which can save PCB area and cost.

The SGM7300AN is available in a Green TLGA-2.5×4.5-20L package.

## **FEATURES**

- High Bandwidth: 9GHz

- Support 10Gbps Signal Transmission

- Support USB 3.1 Gen1 and Gen2 Data Rates

- Low Insertion Loss:

- -0.36dB at 0.1GHz

- + -0.71dB at 4.0GHz

- Low Off-State Isolation: -21dB at 4.0GHz

- Low Return Loss: -20dB at 4.0GHz

- Available in a Green TLGA-2.5×4.5-20L Package

## **APPLICATIONS**

**USB 3.1**

PCI Express Generation 3

DisplayPort 1.2

SATA 6Gbit/s

High-Speed Differential Signals Routing

## PACKAGE/ORDERING INFORMATION

| MODEL     | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER  | PACKAGE<br>MARKING    | PACKING<br>OPTION   |  |

|-----------|------------------------|-----------------------------------|---------------------|-----------------------|---------------------|--|

| SGM7300AN | TLGA-2.5×4.5-20L       | -40°C to +85°C                    | SGM7300ANYTLN20G/TR | 1TY<br>TLN20<br>XXXXX | Tape and Reel, 5000 |  |

### **MARKING INFORMATION**

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### ABSOLUTE MAXIMUM RATINGS

| Supply Voltage, V <sub>DD</sub>   | 0.3V to 3.7V   |

|-----------------------------------|----------------|

| Package Thermal Resistance        |                |

| TLGA-2.5×4.5-20L, θ <sub>JA</sub> | 105.6°C/W      |

| TLGA-2.5×4.5-20L, θ <sub>JB</sub> | 78.3°C/W       |

| TLGA-2.5×4.5-20L, θ <sub>JC</sub> | 100.5°C/W      |

| Junction Temperature              | +150°C         |

| Storage Temperature Range         | 55°C to +150°C |

| Lead Temperature (Soldering, 10s) | +260°C         |

| ESD Susceptibility (1) (2)        |                |

| HBM                               | ±1000V         |

| CDM                               | ±2000V         |

|                                   |                |

#### NOTES:

- 1. For human body model (HBM), all pins comply with ANSI/ESDA/JEDEC JS-001 specifications.

- 2. For charged device model (CDM), all pins comply with ANSI/ESDA/JEDEC JS-002 specifications.

#### RECOMMENDED OPERATING CONDITIONS

| Supply Voltage, V <sub>DD</sub>                      | 3.0V to 3.6V  |

|------------------------------------------------------|---------------|

| Control Voltage, V <sub>XSD</sub> , V <sub>SEL</sub> | 0V to 3.6V    |

| Operating Temperature Range                          | 40°C to +85°C |

## **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

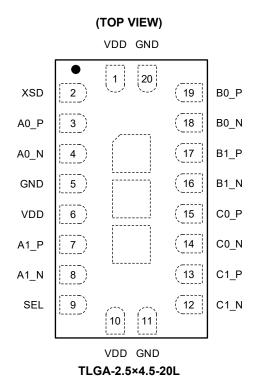

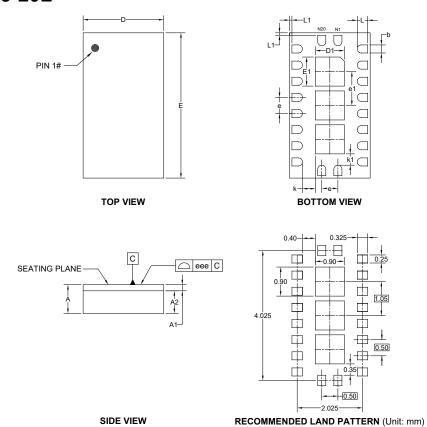

# **PIN CONFIGURATION**

# **PIN DESCRIPTION**

| PIN         | NAME | TYPE                    | FUNCTION                                                      |

|-------------|------|-------------------------|---------------------------------------------------------------|

| 3           | A0_P | I/O                     | Channel 0, Port A, Positive/Negative Signal.                  |

| 4           | A0_N | I/O                     | Charmer 0, Fort A, Fositive/Negative Signal.                  |

| 7           | A1_P | I/O                     | Channel 1 Part A Positive/Negative Signal                     |

| 8           | A1_N | I/O                     | Channel 1, Port A, Positive/Negative Signal.                  |

| 19          | B0_P | I/O                     | Channel 0, Port B, Positive/Negative Signal.                  |

| 18          | B0_N | I/O                     | Charmer 0, Port B, Positive/Negative Signal.                  |

| 17          | B1_P | I/O                     | Channel 1 Part P. Pasitive/Negative Signal                    |

| 16          | B1_N | I/O                     | Channel 1, Port B, Positive/Negative Signal.                  |

| 15          | C0_P | I/O                     | Channel O Part C Positive/Negative Signal                     |

| 14          | C0_N | I/O                     | Channel 0, Port C, Positive/Negative Signal.                  |

| 13          | C1_P | I/O                     | Channel 1 Part C. Pasitiva/Negative Signal                    |

| 12          | C1_N | I/O                     | Channel 1, Port C, Positive/Negative Signal.                  |

| 9           | SEL  | CMOS Single-Ended Input | Operation Mode Select Pin. SEL = Low: A ↔ B SEL = High: A ↔ C |

| 2           | XSD  | CMOS Single-Ended Input | XSD = Low: Normal Operation<br>XSD = High: Hi-Z Operation     |

| 1, 6, 10    | VDD  | Power                   | Positive Supply Voltage.                                      |

| 5, 11, 20   | GND  | Power                   | Ground.                                                       |

| Exposed Pad |      | Power                   | Exposed pad must be connected to ground.                      |

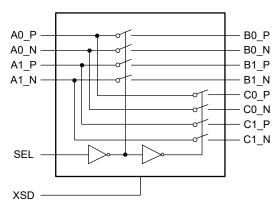

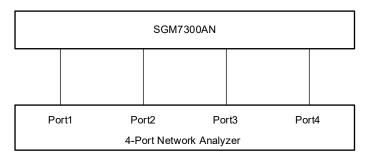

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. Block Diagram

# **FUNCTIONAL DESCRIPTION**

| XSD  | SEL  | FUNCTION            |

|------|------|---------------------|

| High | X    | All channel off     |

| Low  | Low  | Channel on An to Bn |

| Low  | High | Channel on An to Cn |

X = Don't care.

# **ELECTRICAL CHARACTERISTICS**

$(T_A = +25^{\circ}C, V_{DD} = 3.3V \pm 0.3V, \text{ typical values are at } V_{DD} = 3.3V \text{ and maximum loading, unless otherwise noted.})$

| PARAMETER                         | SYMBOL               | CONDITIONS                                  |                                                  | MIN | TYP   | MAX               | UNITS |

|-----------------------------------|----------------------|---------------------------------------------|--------------------------------------------------|-----|-------|-------------------|-------|

| Static Characteristics            | •                    |                                             |                                                  | _   | •     |                   | •     |

| Committee Command                 |                      | Normal mode, V <sub>DD</sub> = max,         |                                                  | 80  | 100   |                   |       |

| Supply Current                    | I <sub>VDD</sub>     | Hi-Z mode, V <sub>DD</sub> = max, XS        | D = high                                         |     | 80    | 100               | μA    |

| High-Level Input Current          | I <sub>IH</sub>      | $V_{DD} = max, V_I = V_{DD}$                |                                                  |     |       | ±30               | μΑ    |

| Low-Level Input Current           | I <sub>IL</sub>      | V <sub>DD</sub> = max, V <sub>I</sub> = GND | ' <sub>DD</sub> = max, V <sub>i</sub> = GND      |     |       | ±30               | μΑ    |

| High-Level Input Voltage          | V <sub>IH</sub>      | SEL, XSD pins                               |                                                  | 1.4 |       | $V_{DD}$          | V     |

| Low-Level Input Voltage           | V <sub>IL</sub>      | SEL, XSD pins                               |                                                  |     |       | 0.45              | V     |

|                                   | .,                   | Differential pins                           |                                                  |     |       | 2.4               | .,    |

| Input Voltage                     | V <sub>IN</sub>      | SEL, XSD pins                               |                                                  |     |       | $V_{DD}$          | V     |

| Common-Mode Input Voltage         | V <sub>IC</sub>      |                                             |                                                  |     |       | 2                 | V     |

| Differential Input Voltage        | V <sub>ID</sub>      | Peak to peak                                |                                                  |     |       | 1.6               | V     |

| Dynamic Characteristics           |                      |                                             |                                                  | •   | •     | 1                 |       |

|                                   | DDIL                 | Channel is off                              | f <sub>0</sub> = 0.1GHz                          |     | -47   |                   | - dB  |

| D.W                               |                      |                                             | f <sub>0</sub> = 4.0GHz                          |     | -21   |                   |       |

| Differential Insertion Loss       |                      | Channel is on                               | f <sub>0</sub> = 0.1GHz                          |     | -0.36 |                   |       |

|                                   |                      |                                             | f <sub>0</sub> = 4.0GHz                          |     | -0.71 |                   |       |

| Differential New Food Occasion    | DDMENT               | A 1:                                        | f <sub>0</sub> = 0.1GHz                          |     | -60   |                   | 40    |

| Differential Near-End Crosstalk   | DDNEXT               | Adjacent channels are on                    | f <sub>0</sub> = 4.0GHz                          |     | -36   |                   | dB    |

| -3dB Bandwidth                    | BW                   |                                             |                                                  |     | 9     |                   | GHz   |

| Differential Date and Land        | DDDI                 | f <sub>0</sub> = 0.1GHz                     |                                                  |     | -31   |                   | i.    |

| Differential Return Loss          | DDRL                 | f <sub>0</sub> = 4.0GHz                     |                                                  | -20 |       | dB                |       |

| On-State Resistance               | R <sub>on</sub>      | $V_{DD} = 3.3V, V_{IN} = 2V, I_{IN} = 3.3V$ | 19mA                                             |     | 5.5   | 9                 | Ω     |

| On-State Input/Output Capacitance | C <sub>IO_ON</sub>   |                                             |                                                  |     | 2.0   |                   | pF    |

| Propagation Delay                 | t <sub>PD</sub>      | An to Bn or An to Cn, frequ                 | uency = 4.0GHz                                   |     |       | 100 (1)           | ps    |

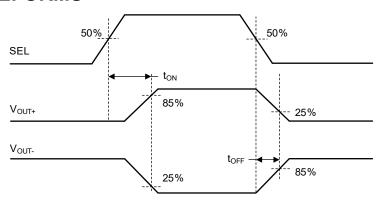

| Switching Characteristics         |                      |                                             |                                                  |     | •     |                   |       |

| Start-Up Time                     | t <sub>STARTUP</sub> | V <sub>DD</sub> = 3.3V and XSD is turn      | V <sub>DD</sub> = 3.3V and XSD is turning to low |     |       | 1000              | ns    |

| Turn-On Time                      | t <sub>ON</sub>      |                                             |                                                  |     |       | 150               | ns    |

| Turn-Off Time                     | t <sub>OFF</sub>     |                                             |                                                  |     |       | 150               | ns    |

| Differential Skew Time            | t <sub>SK_DIF</sub>  | Intra-pair                                  |                                                  |     |       | 15 <sup>(1)</sup> | ps    |

| Skew Time                         | t <sub>sk</sub>      | Inter-pair                                  |                                                  |     |       | 25 <sup>(1)</sup> | ps    |

#### NOTE:

1. Guaranteed by design, not tested in production.

# **VOLTAGE WAVEFORMS**

Figure 2. Voltage Waveforms for Enable and Disable Times

Figure 3. Test Circuit

## **DETAILED DESCRIPTION**

The SGM7300AN is a 4-channel, high-speed bidirectional passive switch. The device provides switching on differential channels between A port and B port or C port according to the control pin SEL. The SGM7300AN has a common voltage range from 0V to 2V and differential signaling amplitude up to  $1600 \text{mV}_{PP}$ . It can be flexibly applied in many interface applications. Besides, the impedances of all Ports are Hi-Z relative to GND pin. For more detailed descriptions, please refer to Table 1 and Table 2.

Table 1. Port Impedance at V<sub>DD</sub> Power-Off

| XSD  | SEL  | Port Impedance State |        |        |  |  |

|------|------|----------------------|--------|--------|--|--|

| ASD  | SEL  | A Port               | B Port | C Port |  |  |

| High | Х    |                      |        |        |  |  |

| Low  | Low  | Hi-Z                 | Hi-Z   | Hi-Z   |  |  |

| Low  | High |                      |        |        |  |  |

Table 2. Port Impedance at V<sub>DD</sub> Power-On

| XSD  | SEL  | Port Impedance State |        |        |  |  |  |

|------|------|----------------------|--------|--------|--|--|--|

|      | SEL  | A Port               | B Port | C Port |  |  |  |

| High | Х    | Hi-Z                 | Hi-Z   | Hi-Z   |  |  |  |

| Low  | Low  | Hi-Z                 | Hi-Z   | Hi-Z   |  |  |  |

| Low  | High | Hi-Z                 | Hi-Z   | Hi-Z   |  |  |  |

X = Don't care.

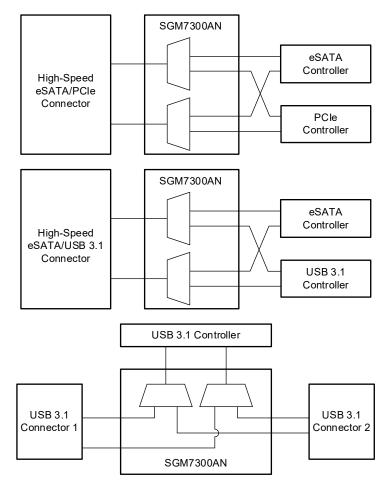

### APPLICATION INFORMATION

The SGM7300AN is a generic analog differential passive switch that can work for both multiplexer (MUX) and demultiplexer (DEMUX) configurations for any high-speed interface application, such as PCI Express Generation 3, USB 3.1. This device allows high-speed switching with minimum attenuation to the signal eye diagram with very little added jitter due to its excellent dynamic characteristics. The typical application diagram of SGM7300AN is shown in the Figure 4.

Figure 4. Typical Application Scenario

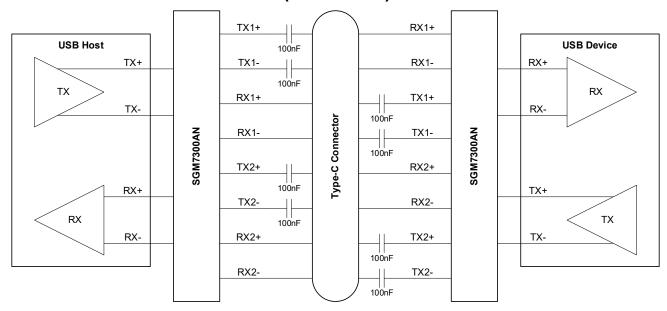

Most interfaces require AC coupling between the transmitter and receiver. The recommended providing AC coupling packaging is 0402. The 0805 size capacitors may be avoided. The AC coupling capacitors should be symmetrically placed and the value should match for the lane pair. The SGM7300AN can be used with the USB Type-C connector to support the connector's flip. Figure 5 provides the generic location for the AC coupling capacitors for this application.

# **APPLICATION INFORMATION (continued)**

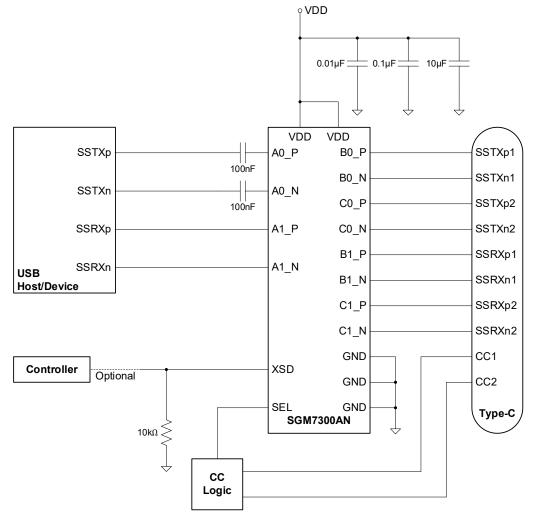

Figure 5. AC Coupling Capacitors for USB Type-C

Figure 6. USB 3.1 Type-C Connector

# 3.3V, Differential 2-Channel, 2:1 Multiplexer/Demultiplexer Switch

Page

# SGM7300AN

# **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Original to REV.A (JULY 2025)

# PACKAGE OUTLINE DIMENSIONS TLGA-2.5×4.5-20L

| Obl    | Dimensions In Millimeters |           |       |  |  |  |  |

|--------|---------------------------|-----------|-------|--|--|--|--|

| Symbol | MIN                       | NOM       | MAX   |  |  |  |  |

| А      | 0.840                     | -         | 0.940 |  |  |  |  |

| A1     | 0.160                     | -         | 0.220 |  |  |  |  |

| A2     |                           | 0.700 REF |       |  |  |  |  |

| b      | 0.200                     | -         | 0.300 |  |  |  |  |

| D      | 2.400                     | -         | 2.600 |  |  |  |  |

| E      | 4.400                     | -         | 4.600 |  |  |  |  |

| D1     | 0.800                     | 0.900     | 1.000 |  |  |  |  |

| E1     | 0.800                     | 0.900     | 1.000 |  |  |  |  |

| е      | 0.500 BSC                 |           |       |  |  |  |  |

| e1     | 1.050 BSC                 |           |       |  |  |  |  |

| L      | 0.275                     | -         | 0.375 |  |  |  |  |

| L1     | 0.025                     | -         | 0.125 |  |  |  |  |

| k      | 0.400 REF                 |           |       |  |  |  |  |

| k1     |                           | 0.350 REF |       |  |  |  |  |

| eee    |                           | 0.100     |       |  |  |  |  |

NOTE: This drawing is subject to change without notice.

# TAPE AND REEL INFORMATION

## **REEL DIMENSIONS**

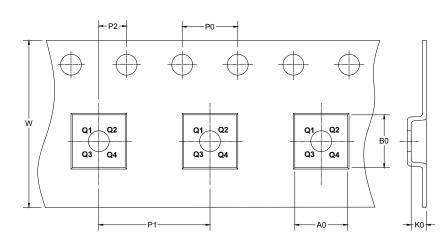

## **TAPE DIMENSIONS**

DIRECTION OF FEED

NOTE: The picture is only for reference. Please make the object as the standard.

## **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type     | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| TLGA-2.5×4.5-20L | 13″              | 12.4                     | 2.8        | 4.8        | 1.15       | 4          | 8          | 2          | 12        | Q1               |

## **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

# **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |        |

|-----------|----------------|---------------|----------------|--------------|--------|

| 13″       | 386            | 280           | 370            | 5            | DD0002 |