## SGM4522Q Automotive, Bidirectional 8:1, 5V, 1-Channel Multiplexer with Injection Current Control

### **GENERAL DESCRIPTION**

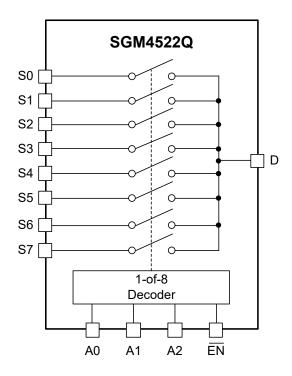

The SGM4522Q is a single 8-channel CMOS analog multiplexer with injection current control. The device has three control inputs that can be used as selecting one of the 8 channels (Sx) to connect to the common terminal (Dx). The multiplexer supports bidirectional signal transmission in the voltage range from GND to  $V_{\text{DD}}$ .

All logic inputs of the SGM4522Q are allowed to be equal to the power supply voltage and compatible with TTL and CMOS logic thresholds standards during normal operation of the power supply. Besides, all control inputs are also designed with fail-safe function. It allows the voltage of all control pins within the maximum absolute withstand voltage range to exceed the  $V_{\text{DD}}$  without damaging the device.

The injection current control function of the SGM4522Q allows signals on disabled signal channels to exceed the  $V_{DD}$  without affecting the enabled signal channel. In addition, all pins of the SGM4522Q except GND are not designed with internal diodes path to the  $V_{DD}$  pin, so as not to damage the components connected to the power pin and avoid injecting reverse current into the power supply.

The device is AEC-Q100 qualified (Automotive Electronics Council (AEC) standard Q100 Grade 1) and it is suitable for automotive applications.

The SGM4522Q is available in Green TSSOP-16 and TQFN-2.5×3.5-16AL packages. It operates over an operating temperature range of -40°C to +125°C.

#### **FEATURES**

- AEC-Q100 Qualified for Automotive Applications

Device Temperature Grade 1

- $T_A = -40^{\circ}C$  to +125°C

- V<sub>DD</sub> Operation Range: 1.62V to 5.5V

- Injection Current Control

- Back-Powering Protection

No ESD Diodes between All Ports and V<sub>DD</sub>

- Bidirectional Signal Path

- Rail-to-Rail Operation

- Control Pin Fail-Safe Function

- Break-Before-Make Switching

- -40°C to +125°C Operating Temperature Range

- Available in Green TSSOP-16 and TQFN-2.5×3.5-16AL Packages

### **APPLICATIONS**

Automotive System

Battery Management Systems (BMS)

Signal Multiplexing and Demultiplexing

Diagnostics and Monitoring in Automotive

ADC and DAC System

## **PACKAGE/ORDERING INFORMATION**

| MODEL    | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>TOP<br>MARKING | PACKING<br>OPTION   |

|----------|------------------------|-----------------------------------|--------------------|---------------------------|---------------------|

| 00145000 | TSSOP-16               | -40°C to +125°C                   | SGM4522QTS16G/TR   | 0DNTS16<br>XXXXX          | Tape and Reel, 4000 |

| SGM4522Q | TQFN-2.5×3.5-16AL      | -40°C to +125°C                   | SGM4522QTVF16G/TR  | 0NGTVF<br>XXXXX<br>YYYYYY | Tape and Reel, 8000 |

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage Range, V <sub>DD</sub><br>Logic Control Input Pin Voltage (EN, A0, A | $\lambda$ 1, A2), $V_{SEL}$ or $V_{EN}$ |

|-------------------------------------------------------------------------------------|-----------------------------------------|

| Source or Drain Voltage, V <sub>S</sub> or V <sub>D</sub> 0                         |                                         |

| Continuous Current through Switch (Sx, D                                            | •                                       |

| -40°C to +125°C                                                                     | 50mA to 50mA                            |

| Continuous Current through GND, I <sub>GND</sub>                                    | -100mA to 100mA                         |

| Package Thermal Resistance                                                          |                                         |

| TSSOP-16, θ <sub>JA</sub>                                                           | 130.8°C/W                               |

| TSSOP-16, θ <sub>JB</sub>                                                           | 88.2°C/W                                |

| TSSOP-16, θ <sub>JC</sub>                                                           | 53.6°C/W                                |

| TQFN-2.5×3.5-16AL, θ <sub>JA</sub>                                                  | 63.8°C/W                                |

| TQFN-2.5×3.5-16AL, θ <sub>JB</sub>                                                  | 25.4°C/W                                |

| TQFN-2.5×3.5-16AL, θ <sub>JC(TOP)</sub>                                             | 51.3°C/W                                |

| TQFN-2.5×3.5-16AL, $\theta_{JC(BOT)}$                                               | 7.3°C/W                                 |

| Junction Temperature                                                                | +150°C                                  |

| Storage Temperature Range                                                           | 65°C to +150°C                          |

| Lead Temperature (Soldering, 10s)                                                   | +260°C                                  |

| ESD Susceptibility (1)(2)                                                           |                                         |

| HBM                                                                                 |                                         |

| CDM                                                                                 | ±1000V                                  |

|                                                                                     |                                         |

#### NOTES:

- 1. For human body model (HBM), all pins comply with AEC-Q100-002 specification.

- 2. For charged device model (CDM), all pins comply with AEC-Q100-011 specification.

#### RECOMMENDED OPERATING CONDITIONS

| Supply Voltage Range, V <sub>DD</sub> 1.62V to 5.5V                                      |

|------------------------------------------------------------------------------------------|

| Signal Path Input/Output Voltage, $V_{\text{S}}$ or $V_{\text{D}}$ 0V to $V_{\text{DD}}$ |

| Logic Control Input Pin Voltage ( $\overline{EN},$ A0, A1, A2), $V_{SEL}$ or $V_{EN}$    |

| 0V to 5.5V                                                                               |

| Continuous Current through Switch (Sx, D Pins), $I_{S}$ or $I_{D(\text{CONT})}$          |

| -40°C to +125°C50mA to 50mA                                                              |

| Current per Input into Source or Drain Pins when Signal                                  |

| Voltage Exceeds Recommended Operating Voltage, I <sub>OK</sub>                           |

| 50mA to 50mA                                                                             |

| Injected Current into Single Off Switch Input, I <sub>INJ</sub>                          |

| 50mA to 50mA                                                                             |

| Total Injected Current into All Off Switch Inputs Combined,                              |

| I <sub>INJ_ALL</sub> 100mA to 100mA                                                      |

| Operating Ambient Temperature Range40°C to +125°C                                        |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

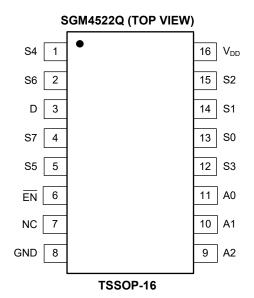

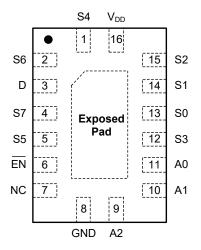

## **PIN CONFIGURATIONS**

### SGM4522Q (TOP VIEW)

TQFN-2.5×3.5-16AL

## **PIN DESCRIPTION**

| PIN      |                   | NAME        | FUNCTION                                                                                                                                         |

|----------|-------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| TSSOP-16 | TQFN-2.5×3.5-16AL | NAME        | FUNCTION                                                                                                                                         |

| 1        | 1                 | S4          | Source Pin 4. Signal input or output path.                                                                                                       |

| 2        | 2                 | S6          | Source Pin 6. Signal input or output path.                                                                                                       |

| 3        | 3                 | D           | Drain Pin (Common Terminal). Signal input or output path.                                                                                        |

| 4        | 4                 | S7          | Source Pin 7. Signal input or output path.                                                                                                       |

| 5        | 5                 | S5          | Source Pin 5. Signal input or output path.                                                                                                       |

| 6        | 6                 | ĒN          | Enable Control Input Pin (Active Low). When $\overline{EN}$ is set to high, common terminal is disconnected to any other signal ports.           |

| 7        | 7                 | NC          | No Connection.                                                                                                                                   |

| 8        | 8                 | GND         | Ground Pin.                                                                                                                                      |

| 9        | 9                 | A2          | Digital Address A2 Pin.                                                                                                                          |

| 10       | 10                | A1          | Digital Address A1 Pin.                                                                                                                          |

| 11       | 11                | A0          | Digital Address A0 Pin.                                                                                                                          |

| 12       | 12                | S3          | Source Pin 3. Signal input or output path.                                                                                                       |

| 13       | 13                | S0          | Source Pin 0. Signal input or output path.                                                                                                       |

| 14       | 14                | S1          | Source Pin 1. Signal input or output path.                                                                                                       |

| 15       | 15                | S2          | Source Pin 2. Signal input or output path.                                                                                                       |

| 16       | 16                | $V_{DD}$    | Power Supply Pin. It is recommended to connect a $0.1\mu F$ to $10\mu F$ capacitor between $V_{DD}$ and GND to get good power supply decoupling. |

| _        | Exposed Pad       | Exposed Pad | Exposed Pad. It can be connected to GND or be left floating.                                                                                     |

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. Block Diagram

## **FUNCTION TABLE**

| ENI | SE       | LECT INPU | ITS | SELECTED SIGNAL DATH CONNECTED TO DRAIN (D) DIN |  |  |  |

|-----|----------|-----------|-----|-------------------------------------------------|--|--|--|

| ĒN  | A2 A1 A0 |           | A0  | SELECTED SIGNAL PATH CONNECTED TO DRAIN (D) PIN |  |  |  |

| 0   | 0        | 0         | 0   | S0                                              |  |  |  |

| 0   | 0        | 0         | 1   | S1                                              |  |  |  |

| 0   | 0        | 1         | 0   | S2                                              |  |  |  |

| 0   | 0        | 1         | 1   | S3                                              |  |  |  |

| 0   | 1        | 0         | 0   | S4                                              |  |  |  |

| 0   | 1        | 0         | 1   | S5                                              |  |  |  |

| 0   | 1        | 1         | 0   | S6                                              |  |  |  |

| 0   | 1        | 1         | 1   | S7                                              |  |  |  |

| 1   | X        | X         | X   | All Channels are OFF                            |  |  |  |

NOTE: X = Don't care.

## **ELECTRICAL CHARACTERISTICS**

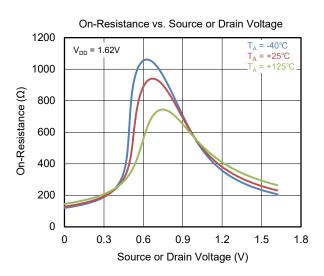

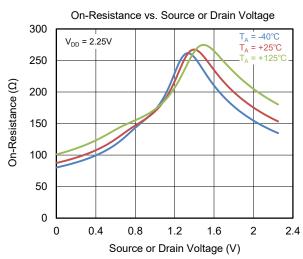

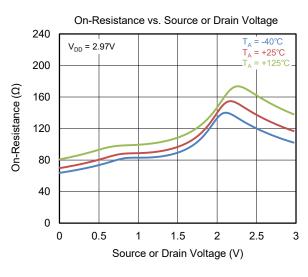

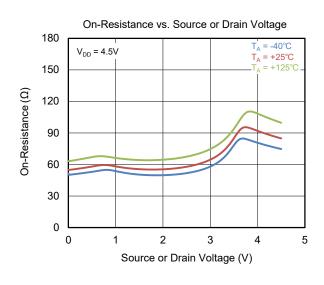

(At specified  $V_{DD}$  ±10%, typical values measured at nominal  $V_{DD}$ ,  $T_A$  = +25°C, unless otherwise noted.)

| PARAMETER                      | SYMBOL              | CONDITIONS                                                           |                        | TEMP  | MIN | TYP  | MAX  | UNITS      |

|--------------------------------|---------------------|----------------------------------------------------------------------|------------------------|-------|-----|------|------|------------|

|                                |                     |                                                                      | \/ - 4.0\/             | +25°C |     | 950  | 1600 |            |

|                                |                     |                                                                      | $V_{DD} = 1.8V$        | Full  |     |      | 1800 |            |

|                                |                     |                                                                      | ., 0.51/               | +25°C |     | 260  | 385  |            |

|                                |                     | $V_{S} = 0V \text{ to } V_{DD}, I_{SD} = 0.5\text{mA},$              | $V_{DD} = 2.5V$        | Full  |     |      | 420  |            |

| On-Resistance                  | R <sub>on</sub>     | Test Circuit 1                                                       |                        | +25°C |     | 150  | 210  | Ω          |

|                                |                     |                                                                      | $V_{DD} = 3.3V$        | Full  |     |      | 240  |            |

|                                |                     |                                                                      |                        | +25°C |     | 93   | 120  |            |

|                                |                     |                                                                      | $V_{DD} = 5V$          | Full  |     |      | 150  |            |

|                                |                     |                                                                      |                        | +25°C |     | 11   | 90   |            |

|                                |                     |                                                                      | $V_{DD} = 1.8V$        | Full  |     |      | 95   |            |

|                                |                     |                                                                      | ., 0.51/               | +25°C |     | 2.5  | 18   |            |

| On-Resistance Matching         |                     | $V_{\rm S} = 0 \text{V to } V_{\rm DD}, I_{\rm SD} = 0.5 \text{mA},$ | $V_{DD} = 2.5V$        | Full  |     |      | 20   |            |

| between Inputs                 | $\Delta R_{ON}$     | Test Circuit 1                                                       |                        | +25°C |     | 1.2  | 8.5  | Ω          |

|                                |                     |                                                                      | $V_{DD} = 3.3V$        | Full  |     |      | 10   |            |

|                                |                     |                                                                      |                        | +25°C |     | 1    | 6    |            |

|                                |                     |                                                                      | $V_{DD} = 5V$          | Full  |     |      | 7    |            |

|                                |                     | $V_S$ = 0V to $V_{DD}$ , $I_{SD}$ = 0.5mA, Test Circuit 1            |                        | +25°C |     | 825  | 1400 | Ω          |

|                                |                     |                                                                      | $V_{DD} = 1.8V$        | Full  |     |      | 1500 |            |

|                                |                     |                                                                      |                        | 25°C  |     | 175  | 270  |            |

|                                |                     |                                                                      | $V_{DD} = 2.5V$        | Full  |     |      | 310  |            |

| On-Resistance Flatness         | R <sub>FLAT</sub>   |                                                                      | V <sub>DD</sub> = 3.3V | +25°C |     | 83   | 125  |            |

|                                |                     |                                                                      |                        | Full  |     |      | 130  |            |

|                                |                     |                                                                      | V <sub>DD</sub> = 5V   | +25°C |     | 40   | 60   |            |

|                                |                     |                                                                      |                        | Full  |     |      | 70   |            |

|                                |                     |                                                                      | V <sub>DD</sub> = 1.8V | Full  |     | ±10  | ±800 |            |

| Channel On Leakage             | I <sub>D(ON)</sub>  | Switch On $V_D = V_S = 0.8 \times V_{DD}$ or                         | V <sub>DD</sub> = 2.5V | Full  |     | ±10  | ±800 |            |

| Current                        | I <sub>S(ON)</sub>  | $V_D = V_S = 0.2 \times V_{DD}$                                      | V <sub>DD</sub> = 3.3V | Full  |     | ±10  | ±800 | nA         |

|                                |                     | Test Circuit 2                                                       | $V_{DD} = 5V$          | Full  |     | ±10  | ±800 |            |

|                                |                     | Switch Off                                                           | V <sub>DD</sub> = 1.8V | Full  |     | ±10  | ±800 |            |

| Source Off Leakage             |                     | $V_D = 0.8 \times V_{DD} / 0.2 \times V_{DD},$                       | V <sub>DD</sub> = 2.5V | Full  |     | ±10  | ±800 | <b>~</b> Λ |

| Current                        | I <sub>S(OFF)</sub> | $V_S = 0.2 \times V_{DD} / 0.8 \times V_{DD}$                        | $V_{DD} = 3.3V$        | Full  |     | ±10  | ±800 | nA         |

|                                |                     | Test Circuit 3                                                       | $V_{DD} = 5V$          | Full  |     | ±10  | ±800 |            |

|                                |                     | Switch Off                                                           | $V_{DD} = 1.8V$        | Full  |     | ±10  | ±800 |            |

| Drain Off Leakage Current      | I <sub>D(OFF)</sub> | $V_D = 0.8 \times V_{DD} / 0.2 \times V_{DD},$                       | $V_{DD} = 2.5V$        | Full  |     | ±10  | ±800 | nA         |

| (Common Drain Pin)             | ·D(OFF)             | $V_S = 0.2 \times V_{DD} / 0.8 \times V_{DD}$ ,<br>Test Circuit 3    | $V_{DD} = 3.3V$        | Full  |     | ±10  | ±800 | 10.        |

|                                |                     | 1 Got Girouit G                                                      | $V_{DD} = 5V$          | Full  |     | ±10  | ±800 |            |

|                                |                     |                                                                      | $V_{DD} = 1.8V$        | Full  |     | 0.01 | 1    |            |

| V <sub>DD</sub> Supply Current | I <sub>DDH</sub>    | Logic Inputs = V <sub>DD</sub>                                       | $V_{DD} = 2.5V$        | Full  |     | 0.01 | 1    | μA         |

|                                | 35                  |                                                                      | $V_{DD} = 3.3V$        | Full  |     | 0.01 | 1    | •          |

|                                |                     |                                                                      | $V_{DD} = 5V$          | Full  |     | 0.01 | 1    |            |

|                                |                     |                                                                      | $V_{DD} = 1.8V$        | Full  |     | 0.2  | 1    |            |

| V <sub>DD</sub> Supply Current | I <sub>DDL</sub>    | Logic Inputs = 0V                                                    | V <sub>DD</sub> = 2.5V | Full  |     | 0.3  | 1    | - μΑ       |

| -                              |                     |                                                                      | $V_{DD} = 3.3V$        | Full  |     | 0.4  | 1    |            |

|                                | <u> </u>            |                                                                      | $V_{DD} = 5V$          | Full  |     | 0.6  | 1    |            |

## **ELECTRICAL CHARACTERISTICS (continued)**

(At specified  $V_{DD}$  ±10%, typical values measured at nominal  $V_{DD}$ ,  $T_A$  = +25°C, unless otherwise noted.)

| PARAMETER              | SYMBOL            | CONDITIONS                      |                 | TEMP | MIN | TYP  | MAX (1) | UNITS |

|------------------------|-------------------|---------------------------------|-----------------|------|-----|------|---------|-------|

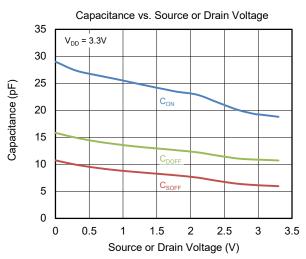

|                        |                   |                                 | $V_{DD} = 1.8V$ | Full |     | 10   | 15      | . [   |

| Source Off Capacitance | C <sub>SOFF</sub> | $V_{S} = V_{DD} / 2$ , f = 1MHz | $V_{DD} = 2.5V$ | Full |     | 10   | 15      |       |

| Source On Capacitance  | OSOFF             | VS - VDD / Z, I - IIVII IZ      | $V_{DD} = 3.3V$ | Full |     | 9.5  | 15      | pF    |

|                        |                   |                                 | $V_{DD} = 5V$   | Full |     | 9    | 15      |       |

|                        | C <sub>DOFF</sub> | $V_S = V_{DD} / 2$ , $f = 1MHz$ | $V_{DD} = 1.8V$ | Full |     | 15   | 20      | pF    |

| Drain Off Capacitance  |                   |                                 | $V_{DD} = 2.5V$ | Full |     | 15   | 20      |       |

| Diain On Capacitance   |                   |                                 | $V_{DD} = 3.3V$ | Full |     | 14.5 | 20      |       |

|                        |                   |                                 | $V_{DD} = 5V$   | Full |     | 14   | 20      |       |

|                        |                   |                                 | $V_{DD} = 1.8V$ | Full |     | 27.5 | 35      | pF    |

| On Capacitance         |                   | $V_S = V_{DD} / 2$ , $f = 1MHz$ | $V_{DD} = 2.5V$ | Full |     | 27.5 | 35      |       |

|                        | Con               |                                 | $V_{DD} = 3.3V$ | Full |     | 27   | 35      |       |

|                        |                   |                                 | $V_{DD} = 5V$   | Full |     | 26   | 35      |       |

#### NOTE:

1. Specified by design and characterization, not production tested.

## LOGIC AND DYNAMIC CHARACTERISTICS

(At specified  $V_{DD}$  ±10%, typical values measured at nominal  $V_{DD}$ ,  $T_A$  = +25°C, unless otherwise noted.)

| PARAMETER                           | SYMBOL             | CONDITIONS                                                                                                            |                        | TEMP  | MIN  | TYP   | MAX  | UNITS |

|-------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------|-------|------|-------|------|-------|

| Logic Inputs (EN, A0, A1,           | A2)                |                                                                                                                       |                        |       |      |       |      |       |

|                                     |                    | V <sub>DD</sub> = 1.8V                                                                                                |                        | Full  | 1.0  |       | 5.5  |       |

| Input Logic High                    | \                  | V <sub>DD</sub> = 2.5V                                                                                                |                        | Full  | 1.1  |       | 5.5  | 1 ,   |

| input Logic High                    | V <sub>IH</sub>    | V <sub>DD</sub> = 3.3V                                                                                                |                        | Full  | 1.15 |       | 5.5  | V     |

|                                     |                    | $V_{DD} = 5V$                                                                                                         |                        | Full  | 1.25 |       | 5.5  |       |

|                                     |                    | V <sub>DD</sub> = 1.8V                                                                                                |                        | Full  | 0    |       | 0.55 |       |

| Input Logic Low                     | V <sub>IL</sub>    | V <sub>DD</sub> = 2.5V                                                                                                |                        | Full  | 0    |       | 0.65 | V     |

| input Logic Low                     | VIL                | V <sub>DD</sub> = 3.3V                                                                                                |                        | Full  | 0    |       | 0.8  | V     |

|                                     |                    | $V_{DD} = 5V$                                                                                                         |                        | Full  | 0    |       | 0.9  |       |

| Logic High Input Leakage<br>Current | I <sub>IH</sub>    | $V_{LOGIC}$ = 1.8V or $V_{DD}$                                                                                        |                        | Full  |      | 0.01  | 1    | μA    |

| - Currona                           | I <sub>IL_AI</sub> | $V_{LOGIC}$ = 0V, $V_{DD}$ = 1.8V to 5V                                                                               |                        | Full  | -1   | -0.01 |      |       |

|                                     |                    |                                                                                                                       | V <sub>DD</sub> = 1.8V | Full  | -1   | -0.2  |      |       |

| Logic Low Input Leakage<br>Current  |                    |                                                                                                                       | V <sub>DD</sub> = 2.5V | Full  | -1   | -0.3  |      | μΑ    |

| Current                             | I <sub>IL_EN</sub> | V <sub>LOGIC</sub> = 0V                                                                                               | V <sub>DD</sub> = 3.3V | Full  | -1   | -0.4  |      | -     |

|                                     |                    |                                                                                                                       | V <sub>DD</sub> = 5V   | Full  | -1   | -0.6  |      | 1     |

| Logic Input Capacitance             | C <sub>IN</sub>    | $V_{LOGIC} = 0V$ , 1.8V or $V_{DD}$ , f = 1N                                                                          | 1Hz                    | Full  |      | 6.5   | 10   | pF    |

| Dynamic Characteristics             | •                  |                                                                                                                       |                        | '     |      |       | •    |       |

| -                                   | Q <sub>INJ</sub>   | $V_S = V_{DD} / 2$ , $R_S = 0\Omega$ , $C_L = 100 pF$ , Test Circuit 4                                                | V <sub>DD</sub> = 1.8V | +25°C |      | -2    |      | pC    |

| Oh anna Inda athan                  |                    |                                                                                                                       | V <sub>DD</sub> = 2.5V | +25°C |      | -6    |      |       |

| Charge Injection                    |                    |                                                                                                                       | V <sub>DD</sub> = 3.3V | +25°C |      | -10   |      |       |

|                                     |                    |                                                                                                                       | V <sub>DD</sub> = 5V   | +25°C |      | -18   |      |       |

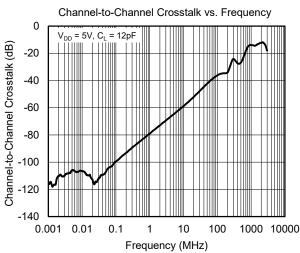

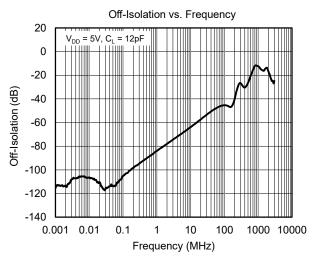

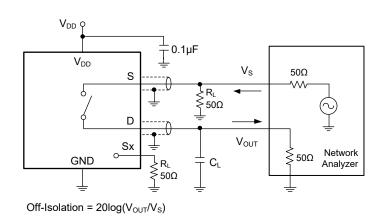

|                                     |                    | $V_{BIAS} = V_{DD} / 2$ , $V_{S} = 200 mVpp$ , $R_{L} = 50 \Omega$ , $C_{L} = 12 pF$ , $f = 100 kHz$ , Test Circuit 5 | $V_{DD} = 1.8V$        | +25°C |      | -100  |      | - dB  |

|                                     |                    |                                                                                                                       | V <sub>DD</sub> = 2.5V | +25°C |      | -100  |      |       |

|                                     |                    |                                                                                                                       | $V_{DD} = 3.3V$        | +25°C |      | -100  |      |       |

| Off-Isolation                       |                    |                                                                                                                       | $V_{DD} = 5V$          | +25°C |      | -100  |      |       |

| On-isolation                        | O <sub>ISO</sub>   |                                                                                                                       | $V_{DD} = 1.8V$        | +25°C |      | -80   |      |       |

|                                     |                    | $V_{BIAS} = V_{DD} / 2$ , $V_{S} = 200 \text{mVpp}$ , $R_{L} = 50 \Omega$ , $C_{L} = 12 \text{pF}$ ,                  | $V_{DD} = 2.5V$        | +25°C |      | -80   |      | dB    |

|                                     |                    | f = 1MHz, Test Circuit 5                                                                                              | $V_{DD} = 3.3V$        | +25°C |      | -80   |      | _ ub  |

|                                     |                    |                                                                                                                       | $V_{DD} = 5V$          | +25°C |      | -80   |      |       |

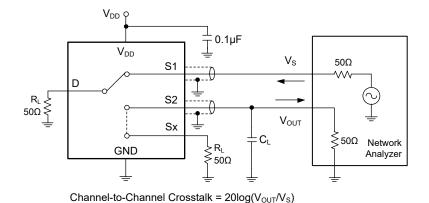

|                                     |                    |                                                                                                                       | $V_{DD} = 1.8V$        | +25°C |      | -95   |      | _     |

|                                     |                    | $V_{BIAS} = V_{DD} / 2$ , $V_{S} = 200 \text{mVpp}$ , $R_{L} = 50 \Omega$ , $C_{L} = 12 \text{pF}$ ,                  | $V_{DD} = 2.5V$        | +25°C |      | -95   |      | dB    |

|                                     |                    | f = 100kHz, Test Circuit 6                                                                                            | $V_{DD} = 3.3V$        | +25°C |      | -95   |      | ub    |

| Channel-to-Channel                  | X <sub>TALK</sub>  |                                                                                                                       | $V_{DD} = 5V$          | +25°C |      | -95   |      |       |

| Crosstalk                           | TIALK              |                                                                                                                       | $V_{DD} = 1.8V$        | +25°C |      | -75   |      |       |

|                                     |                    | $V_{BIAS} = V_{DD} / 2$ , $V_{S} = 200 \text{mVpp}$ , $R_{L} = 50 \Omega$ , $C_{L} = 12 \text{pF}$ ,                  | $V_{DD} = 2.5V$        | +25°C |      | -75   |      | dB    |

|                                     |                    | f = 1MHz, Test Circuit 6                                                                                              | $V_{DD} = 3.3V$        | +25°C |      | -75   |      | ub.   |

|                                     | 1                  |                                                                                                                       | $V_{DD} = 5V$          | +25°C |      | -75   |      |       |

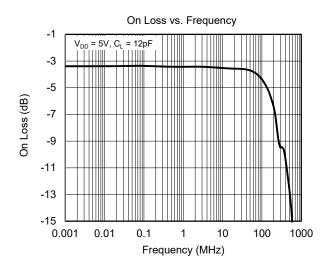

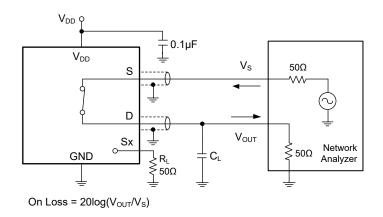

|                                     |                    |                                                                                                                       | $V_{DD} = 1.8V$        | +25°C |      | 215   |      |       |

| -3dB Bandwidth                      | BW                 | $V_{BIAS} = V_{DD} / 2$ , $V_{S} = 200 \text{mVpp}$ , $R_{c} = 500$ , $C_{c} = 12 \text{pF}$                          | $V_{DD} = 2.5V$        | +25°C |      | 200   |      | - MHz |

| -Jub Balluwiulli                    | DVV                | $R_L = 50\Omega$ , $C_L = 12pF$ ,<br>Test Circuit 7                                                                   | $V_{DD} = 3.3V$        | +25°C |      | 190   |      |       |

|                                     |                    |                                                                                                                       | $V_{DD} = 5V$          | +25°C |      | 190   |      |       |

#### TIMING CHARACTERISTICS

(At specified  $V_{DD} \pm 10\%$ , typical values measured at nominal  $V_{DD}$ ,  $T_A = +25$ °C, unless otherwise noted.)

| PARAMETER                      | SYMBOL                  | CONDITIONS                                                                                           |                        | TEMP | MIN (1) | TYP  | MAX (1) | UNITS |  |

|--------------------------------|-------------------------|------------------------------------------------------------------------------------------------------|------------------------|------|---------|------|---------|-------|--|

| Switching Characteristics      | •                       |                                                                                                      |                        | •    |         |      |         |       |  |

| <u> </u>                       |                         |                                                                                                      | V <sub>DD</sub> = 1.8V | Full |         | 25   | 35      |       |  |

|                                |                         | $C_L = 50pF$ ,                                                                                       | V <sub>DD</sub> = 2.5V | Full |         | 13.5 | 25      |       |  |

| Propagation Delay Time         | t <sub>PD</sub>         | Sx to D, D to Sx                                                                                     | V <sub>DD</sub> = 3.3V | Full |         | 9.5  | 20      | ns    |  |

|                                |                         |                                                                                                      | V <sub>DD</sub> = 5V   | Full |         | 6.5  | 17      |       |  |

|                                |                         | C <sub>L</sub> = 15pF, V <sub>DD</sub> = 5V                                                          |                        | Full |         | 3.5  | 12      |       |  |

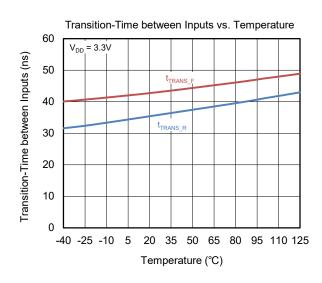

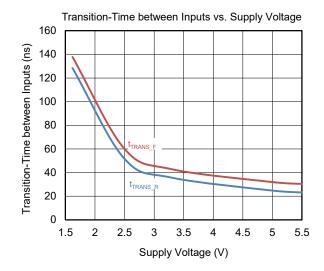

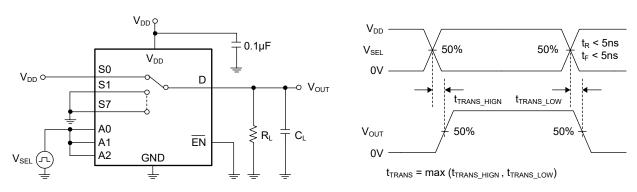

|                                |                         |                                                                                                      | V <sub>DD</sub> = 1.8V | Full |         | 140  | 175     |       |  |

|                                |                         | $R_L = 10k\Omega$ , $C_L = 50pF$ ,                                                                   | V <sub>DD</sub> = 2.5V | Full |         | 70   | 100     |       |  |

| Transition-Time between Inputs | t <sub>TRANS</sub> (2)  | Ax to D, Ax to Sx,<br>Test Circuit 8                                                                 | V <sub>DD</sub> = 3.3V | Full |         | 48   | 75      | ns    |  |

| mpato                          |                         |                                                                                                      | V <sub>DD</sub> = 5V   | Full |         | 35   | 60      |       |  |

|                                |                         | $R_L = 10k\Omega, C_L = 15pF, V_{DD} = 5V,$                                                          | Test Circuit 8         | Full |         | 32   | 55      |       |  |

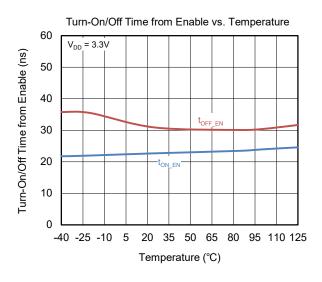

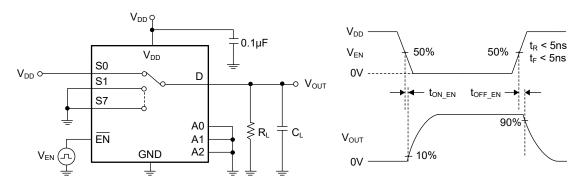

|                                | t <sub>ON_EN</sub> (3)  | $R_L = 10k\Omega$ , $C_L = 50pF$ ,<br>$\overline{EN}$ to D, $\overline{EN}$ to Sx,<br>Test Circuit 9 | V <sub>DD</sub> = 1.8V | Full |         | 62   | 75      | ns    |  |

|                                |                         |                                                                                                      | V <sub>DD</sub> = 2.5V | Full |         | 35   | 50      |       |  |

| Turn-On Time from Enable       |                         |                                                                                                      | $V_{DD} = 3.3V$        | Full |         | 25   | 42      |       |  |

|                                |                         |                                                                                                      | $V_{DD} = 5V$          | Full |         | 20   | 35      |       |  |

|                                |                         | $R_L = 10k\Omega$ , $C_L = 15pF$ , $V_{DD} = 5V$ , Test Circuit 9                                    |                        | Full |         | 20   | 48      |       |  |

|                                |                         |                                                                                                      | $V_{DD} = 1.8V$        | Full |         | 110  | 135     |       |  |

|                                |                         | $R_L = 10k\Omega$ , $C_L = 50pF$ ,                                                                   | V <sub>DD</sub> = 2.5V | Full |         | 60   | 100     |       |  |

| Turn-Off Time from Enable      | t <sub>OFF_EN</sub> (4) | EN to D, EN to Sx,<br>Test Circuit 9                                                                 | V <sub>DD</sub> = 3.3V | Full |         | 35   | 70      | ns    |  |

|                                |                         |                                                                                                      | V <sub>DD</sub> = 5V   | Full |         | 20   | 45      |       |  |

|                                |                         | $R_L = 10k\Omega$ , $C_L = 15pF$ , $V_{DD} = 5V$ ,                                                   | Test Circuit 9         | Full |         | 15   | 40      |       |  |

|                                |                         |                                                                                                      | V <sub>DD</sub> = 1.8V | Full | 2       | 48   |         |       |  |

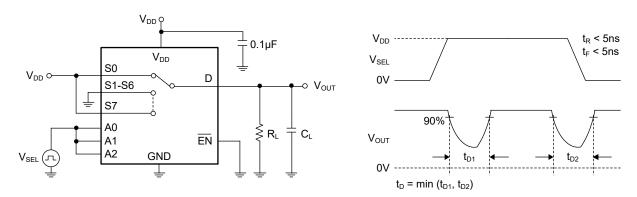

| Break-Before-Make Delay        |                         | $R_L = 10k\Omega$ , $C_L = 15pF$ ,                                                                   | $V_{DD} = 2.5V$        | Full | 0.5     | 19   |         | - ns  |  |

| Time                           | t <sub>D</sub>          | Sx to D, D to Sx,<br>Test Circuit 10                                                                 | $V_{DD} = 3.3V$        | Full | 0.5     | 14   |         |       |  |

|                                |                         |                                                                                                      | V <sub>DD</sub> = 5V   | Full | 0.5     | 10   |         |       |  |

#### NOTES:

- 1. Specified by design and characterization, not production tested.

- 2. If the input logic signal's high level amplitude is  $V_{IH}(MIN)$  and low level amplitude is  $V_{IL}(MAX)$ , the  $t_{TRANS}$  will be 1.5 $\mu$ s.

- 3. If the input logic signal's high level amplitude is  $V_{IH}(MIN)$  and low level amplitude is  $V_{IL}(MAX)$ , the  $t_{ON\_EN}$  will be 1.5 $\mu$ s.

- 4. If the input logic signal's high level amplitude is V<sub>IH</sub>(MIN) and low level amplitude is V<sub>IL</sub>(MAX), the t<sub>OFF</sub> EN will be 0.5µs.

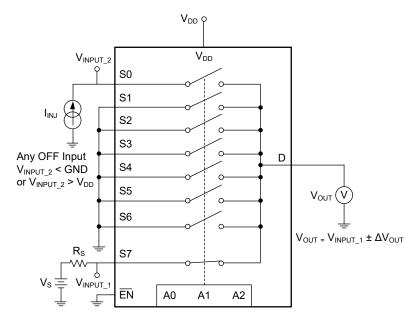

#### INJECTION CURRENT COUPLING

(At specified  $V_{DD} \pm 10\%$ , typical values measured at nominal  $V_{DD}$  and  $T_A = +25$ °C, unless otherwise noted.)

| PARAMETER                                            | SYMBOL            | CONDITIONS                                | TEMP            | MIN  | TYP | MAX  | UNITS |    |  |  |

|------------------------------------------------------|-------------------|-------------------------------------------|-----------------|------|-----|------|-------|----|--|--|

| Injection Current Coupling, Test Circuit 11          |                   |                                           |                 |      |     |      |       |    |  |  |

|                                                      |                   | D < 20k0 L < 1mA                          | $V_{DD} = 1.8V$ | Full |     | 0.01 | 1     |    |  |  |

|                                                      |                   | $R_S \le 3.9k\Omega$ , $I_{INJ} \le 1mA$  | $V_{DD} = 5V$   | Full |     | 0.01 | 0.5   |    |  |  |

|                                                      | ΔV <sub>OUT</sub> | $R_S \le 3.9k\Omega$ , $I_{INJ} \le 10mA$ | $V_{DD} = 1.8V$ | Full |     | 0.01 | 1     | mV |  |  |

| Maximum Shift of Output<br>Voltage of Enabled Analog |                   |                                           | $V_{DD} = 5V$   | Full |     | 0.01 | 0.5   |    |  |  |

| Input                                                |                   | $R_S \le 20k\Omega$ , $I_{INJ} \le 1mA$   | $V_{DD} = 1.8V$ | Full |     | 0.01 | 1     |    |  |  |

|                                                      |                   |                                           | $V_{DD} = 5V$   | Full |     | 0.01 | 0.5   |    |  |  |

|                                                      |                   | $R_s \le 20k\Omega$ . $I_{IN,I} \le 10mA$ | $V_{DD} = 1.8V$ | Full |     | 0.01 | 1     |    |  |  |

|                                                      |                   |                                           | $V_{DD} = 5V$   | Full |     | 0.01 | 0.5   |    |  |  |

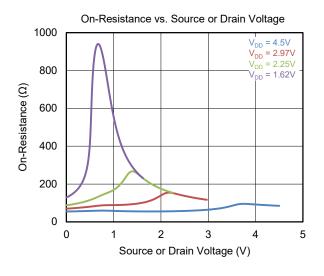

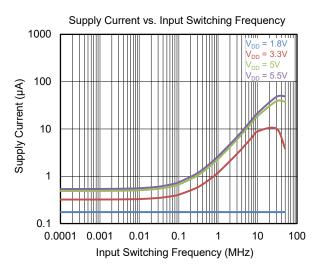

## TYPICAL PERFORMANCE CHARACTERISTICS

$T_A$  = +25°C, unless otherwise noted.

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_A$  = +25°C, unless otherwise noted.

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_A$  = +25°C, unless otherwise noted.

## **TEST CIRCUITS**

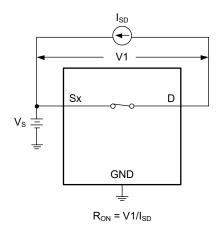

Test Circuit 1. On-Resistance

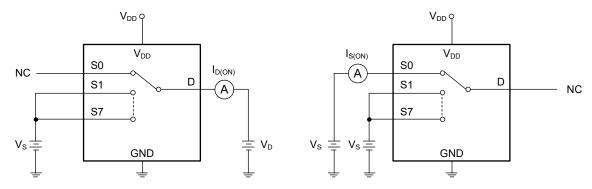

Test Circuit 2. On Leakage

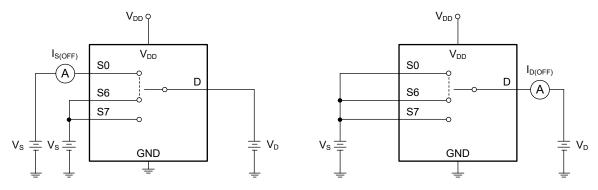

Test Circuit 3. Off Leakage

## **TEST CIRCUITS (continued)**

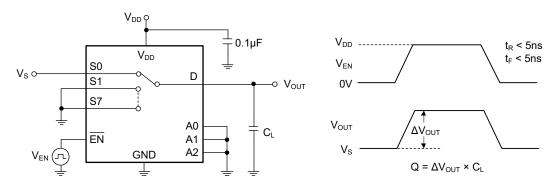

Test Circuit 4. Charge Injection (Q)

**Test Circuit 5. Off-Isolation**

Test Circuit 6. Channel-to-Channel Crosstalk

## **TEST CIRCUITS (continued)**

**Test Circuit 7. On Loss**

Test Circuit 8. Transition Time (trrans)

Test Circuit 9. Switching Times (ton, toff)

## **TEST CIRCUITS (continued)**

Test Circuit 10. Break-Before-Make Delay Time (t<sub>D</sub>)

**Test Circuit 11. Injection Current**

#### APPLICATION INFORMATION

The SGM4522Q is a single 8-channel CMOS analog multiplexer and all signal paths support rail-to-rail operation. All control input pins are also designed with fail-safe function and operate up to 5.5V withstand voltage regardless of the supply voltage. This function can prevent reverse current injection to  $V_{\rm DD}$  pin from control pins even though the voltage of control pins already exceeds the  $V_{\rm DD}$  pin. All signal ports of the SGM4522Q have injection current control circuit between signal inputs and  $V_{\rm DD}$  or GND. It can prevent the signal path from back feeding, and also prevent GND pin from back leaking to signal inputs when the voltage of signal inputs is below the GND pin.

Based on the above special features, the SGM4522Q can be used to simplify circuit design and decrease overall system cost in automotive applications.

#### **Logic Control**

The logic control input pins include  $\overline{\text{EN}}$ , A0, A1, and A2. The logic input thresholds of the SGM4522Q are related to the power supply. The thresholds will increase as the power supply voltage increases. This feature allows the logic control inputs of the SGM4522Q to be connected to processors with lower logic I/O rails and no additional level shifters are required.

#### **Fail-Safe Function**

All control input pins ( $\overline{EN}$ , A0, A1 and A2) of the SGM4522Q are designed with fail-safe function and operate up to 5.5V withstand voltage regardless of the supply voltage. This special design eliminates the need for strict timing control for the SGM4522Q between the V<sub>DD</sub> pin and control input pins. All control pins are allowed to be powered on earlier than the power supply and without damage. The fail-safe function reduces the complexity of system circuit design. For instance, when  $V_{DD} = 0V$ , the fail-safe function allows the control pins of the SGM4522Q to be connected to 5.5V. In this case, the switch is disabled because there is no power supply. Another application, when  $V_{DD}$  = 1.8V, the switch is enabled. The feature allows the control pins to be connected to interface with a logic level of another device up to 5.5V and without the need for additional level shifter.

#### **Enable Control**

The SGM4522Q has an enable control pin  $(\overline{EN})$ . When the  $\overline{EN}$  pin is driven to high and power supply is normal, all the signal paths are disabled and the drain pin is open to any source pins. On the contrary, when the  $\overline{EN}$  pin is driven to low, one of the signal paths is closed according to the logic of address pins (A0, A1 and A2).

#### **Injection Current Control**

Injection current is defined as the current flowing into the input pin when the input voltage is higher than power supply ( $V_{DD} + \Delta V$ ) or lower than ground ( $V_{SS}$ ). Typical CMOS switches are designed with ESD diodes between the input pin and the  $V_{DD}/GND$  pin. These diodes will form a leakage path when the input voltage exceeds the power supply or below ground. This leakage may affect the reliability of the power system. Different applications determine that the injection current can come from different sources.

The current injected by switches or transient events is easy to occur in harsh environments of automotive systems or factory automation.

When the input signals are from various sensors or current sources, the injection current can also affect other self-contained systems.

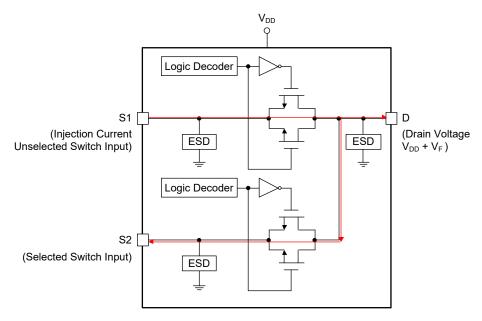

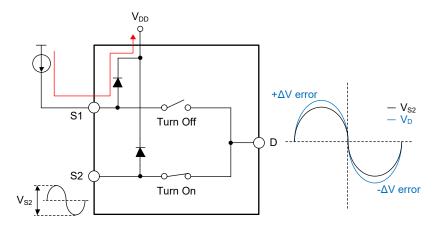

## Injected Current Impact to Typical CMOS Switches

The unexpected injected current may affect the common terminal voltage in application. Typical CMOS switches adopt a parallel structure of NMOS and PMOS and have designed with ESD diodes at the input as shown in Figure 2. These ESD diodes have the function of clamping input voltage. When current is injected into a disabled signal path and the forward diode voltage of the ESD diode (V<sub>F</sub>) is higher than the PMOS threshold voltage (V<sub>T</sub>), the PMOS in the circuit will be turned ON from OFF and form a leakage path between source and drain on disabled signal path. This situation causes the drain voltage to be changed by the source voltage in disabled signal path and it is not expected in applications. The simplified architecture of typical CMOS switch and the associated injected current path are shown in Figure 2.

## **APPLICATION INFORMATION (continued)**

For typical CMOS switch structures, the injected current path is difficult to eliminate. In applications, the impact of injected current can be reduced by adding additional diodes with low forward voltage or resistors network externally at input pin. All signal terminals are not allowed to exceed the voltage of the ESD diode ( $V_T$ ) higher than  $V_{DD}$ .

#### **RON Changes Caused by Current Injection**

On-resistance ( $R_{ON}$ ) of typical CMOS switches is affected by the power supply voltage for enabled switch paths. Assuming the source pin voltage in disabled signal path is higher than the supply voltage by a forward diode voltage ( $V_F$ ). This will cause an error ( $\Delta V$ )

at the drain pin. Figure 3 shows the injected current impact on  $R_{\text{ON}}.$  For example, when S2 is selected for conduction to D, there is an injection current at the disabled S1 pin and the voltage of S1 pin increases above  $V_{\text{DD}}$  to the ESD protection diode is forward biased, the  $V_{\text{DD}}$  voltage will be changed. Changes in supply voltage cause changes in on-resistance ( $R_{\text{ON}}$ ) between S2 and D, thereby causing a  $\Delta V$  error at the D pin. This unexpected error in the output can cause some trouble related to false trigger events, incorrect signal acquisition or abnormal signal detection, thus potentially compromising the accuracy and reliability of the system.

Figure 2. Typical CMOS Switch and Associated Injected Current Path

Figure 3. Injected Current Impact on Ron

## **APPLICATION INFORMATION (continued)**

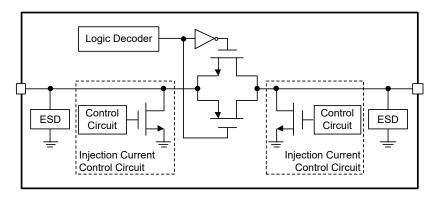

To simplify circuit design and avoid adding additional protection in the system, the SGM4522Q is designed with an internal injection current control function. It allows signals on disabled signal channels to exceed the power supply voltage without affecting the enabled signal channel and typical CMOS switches do not have this feature. There is no need to add additional diodes and resistor networks to keep the input signals within the supply voltage in applications. In addition, there is no internal diode path from all pins except GND to the  $V_{\rm DD}$  pin. This design eliminates the risk of damaging components connected to the supply pin or reverse current injection to the power supply. Figure 4 shows a design block diagram of injection current control circuit of the SGM4522Q.

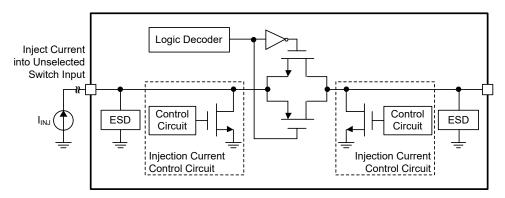

Each source or drain pin (Sx, D) of the SGM4522Q has completely independent injection current control circuit. It includes a control circuit and a FET, which is enabled and shunts unexpected current from the inputs to GND once over-voltage or current injection at the inputs

occurs. The prerequisite for enabling this current control circuit is that the input terminal (Sx, D) is disabled by the control pins and the injected current causes the voltage at the pin to be higher than  $V_{DD}$  or less than GND. Figure 5 shows injected current at input pin when over-voltage or current injection at the inputs occurs

Each injection current circuit can handle a maximum rated current of 50mA and the SGM4522Q can accept a maximum injection current of 100mA at any time. Assuming multiple source terminals are injected at the same time, the SGM4522Q can only accept a total current of 100mA. If the current injected exceeds 100mA, the SGM4522Q is at risk of damage. So a series current limiting resistor may be required and must be sized appropriately based on the system application. Figure 6 shows an application circuit of using a series current limiting resistors when over-voltage event occurs.

Figure 4. Design Block Diagram of Injection Current Control

Figure 5. Injected Current at Input Pin

## **APPLICATION INFORMATION (continued)**

Figure 6. Over-Voltage Event with Series Resistor

Once the voltage at the source or drain pins exceeds  $V_{DD}$  or falls below GND, the FET is enabled for any disabled signal path and shunts unexpected current from the inputs to GND. In this scene, a series of resistors is required to limit the total current injected into the input to within 100mA. An example is as follow:

## SGM4522Q is Powered and the Input Signal is Higher than $V_{DD}$ ( $V_{DD}$ = 5V, $V_{INPUT}$ = 5.5V)

For the typical CMOS switch with an internal ESD diode, when the input signal exceeds the V<sub>DD</sub> pin, the internal ESD diode will be forward biased and the current injected into the power supply from the input. In this case, if the inputs have no additional protective devices, the power supply system may be at risk of damage. Even though the use of limiting resistors can reduce the risk to a certain extent, this risk cannot be completely eliminated due to the architecture of the typical CMOS switch. When the input voltage is too high and exceeds V<sub>DD</sub>, the application circuit still requires a series of limiting resistors, because the injected current control circuit of the SGM4522Q can only handle injection current less than 100mA. The current path of the SGM4522Q is from inputs to GND and does not have the same problems as the current injected into the power rail.

In addition, the injection current control circuit of the SGM4522Q can work well in both unselected and selected paths. It should be noted when the injection current occurs in the selected path, the injection current will also flow through the source to drain path not just flow into ground.

#### **Power Supply and Decoupling**

Power supply range of the  $V_{DD}$  pin is from 1.62V to 5.5V. Besides, the  $V_{DD}$  pin is not allowed to exceed the maximum absolute withstand voltage because over-voltage will cause damage to the SGM4522Q.

In general, the V<sub>DD</sub> pin should be installed with a 0.1µF to 10µF ceramic capacitor to prevent power disturbance from other power supply components and the bypass capacitor should be placed as close as possible to the  $V_{\text{DD}}$  pin for the best power supply Multiple with decoupling. capacitors different capacitance values can also be placed to reject noise of different frequencies in applications with high requirements for noise. One end of this decoupling capacitor should be directly connected to the GND pin of the SGM4522Q as short as possible in PCB layout design.

## **SGM4522Q**

## Automotive, Bidirectional 8:1, 5V, 1-Channel Multiplexer with Injection Current Control

## **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| OCTOBER 2025 – REV.A to REV.A.1                 | Page |

|-------------------------------------------------|------|

| Updated Absolute Maximum Ratings section        | 3    |

| Updated Electrical Characteristics section      | 6    |

| Updated Test Circuits section                   |      |

| Changes from Original (JULY 2024) to REV.A      | Page |

| Changed from product preview to production data | All  |

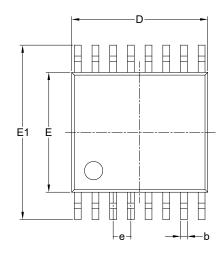

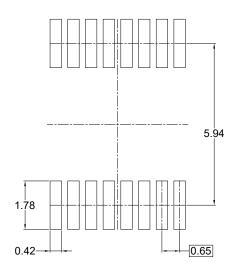

## **PACKAGE OUTLINE DIMENSIONS** TSSOP-16

RECOMMENDED LAND PATTERN (Unit: mm)

| Cumbal | Dimensions In Millimeters |             |       |  |  |  |  |

|--------|---------------------------|-------------|-------|--|--|--|--|

| Symbol | MIN                       | NOM         | MAX   |  |  |  |  |

| А      | -                         | -           | 1.200 |  |  |  |  |

| A1     | 0.050                     | -           | 0.150 |  |  |  |  |

| A2     | 0.800                     | -           | 1.050 |  |  |  |  |

| b      | 0.190                     | 0.190 - 0.3 |       |  |  |  |  |

| С      | 0.090                     | 0.090 -     |       |  |  |  |  |

| D      | 4.860                     | -           | 5.100 |  |  |  |  |

| Е      | 4.300                     | -           | 4.500 |  |  |  |  |

| E1     | 6.200                     | -           | 6.600 |  |  |  |  |

| е      |                           | 0.650 BSC   |       |  |  |  |  |

| L      | 0.450                     | -           | 0.750 |  |  |  |  |

| Н      | 0.250 TYP                 |             |       |  |  |  |  |

| θ      | 0° - 8°                   |             |       |  |  |  |  |

| ccc    | 0.100                     |             |       |  |  |  |  |

- This drawing is subject to change without notice.

The dimensions do not include mold flashes, protrusions or gate burrs.

- 3. Reference JEDEC MO-153.

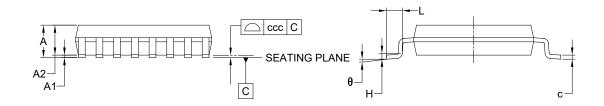

# PACKAGE OUTLINE DIMENSIONS TQFN-2.5×3.5-16AL

| Cumbal | Dimensions In Millimeters |     |       |  |  |

|--------|---------------------------|-----|-------|--|--|

| Symbol | MIN                       | NOM | MAX   |  |  |

| Α      | 0.700                     | -   | 0.800 |  |  |

| A1     | 0.000                     | -   | 0.050 |  |  |

| A2     | 0.203 REF                 |     |       |  |  |

| b      | 0.200                     | -   | 0.300 |  |  |

| D      | 2.400                     | -   | 2.600 |  |  |

| D1     | 0.900                     | -   | 1.100 |  |  |

| E      | 3.400                     | -   | 3.600 |  |  |

| E1     | 1.900                     | -   | 2.100 |  |  |

| е      | 0.500 BSC                 |     |       |  |  |

| k      | 0.350 REF                 |     |       |  |  |

| L      | 0.300                     | -   | 0.500 |  |  |

| eee    | 0.080                     |     |       |  |  |

NOTE: This drawing is subject to change without notice.

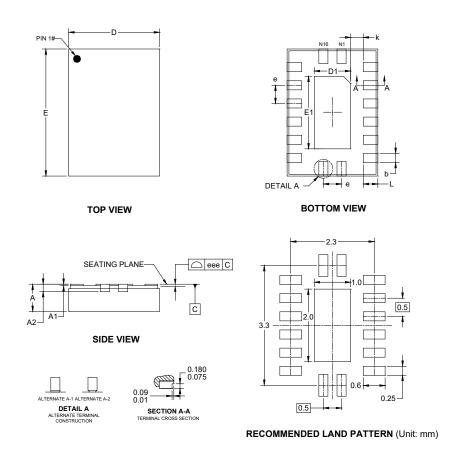

## TAPE AND REEL INFORMATION

#### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type      | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| TSSOP-16          | 13"              | 12.4                     | 6.80       | 5.40       | 1.50       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

| TQFN-2.5×3.5-16AL | 13"              | 12.4                     | 2.80       | 3.80       | 1.13       | 4.0        | 4.0        | 2.0        | 12.0      | Q1               |

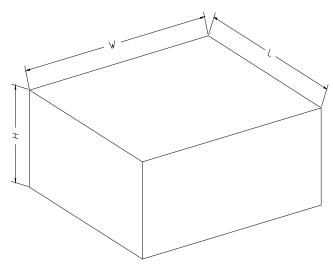

## **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

## **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type | Reel Type Length (mm) |     | Height<br>(mm) | Pizza/Carton |        |  |

|-----------|-----------------------|-----|----------------|--------------|--------|--|

| 13″       | 386                   | 280 | 370            | 5            | DD0002 |  |