# 40V, 500mA, Low Quiescent Current and Low Dropout Voltage Linear Regulator

#### **GENERAL DESCRIPTION**

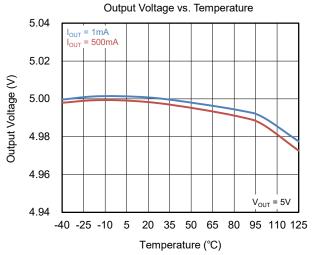

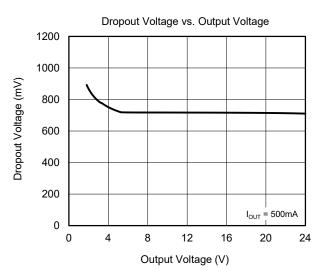

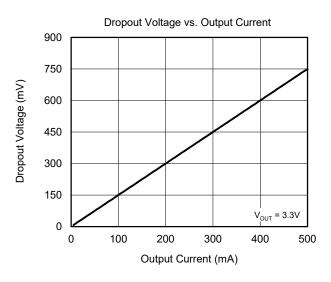

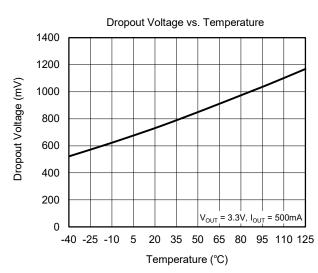

The SGM2242 is a high voltage, low quiescent current and low dropout voltage linear regulator. It is capable of supplying 500mA output current with typical dropout voltage of 750mV. The operating input voltage range is from 3V to 40V. The fixed output voltage range is from 1.8V to 12V and the adjustable output voltage range is from 1.25V to 24V.

Other features include current limit and thermal shutdown protection. The SGM2242 has automatic discharge function to quickly discharge  $V_{\text{OUT}}$  in the disabled status.

The SGM2242 is available in a Green SOIC-8 (Exposed Pad) package. It operates over an operating temperature range of -40°C to +125°C.

#### **FEATURES**

- Operating Input Voltage Range: 3V to 40V

- Enable Pin Accept Voltages Higher than the Supply Voltage and up to 40V

- Fixed Output from 1.8V to 12V

- Adjustable Output from 1.25V to 24V

- 500mA Output Current

- Output Voltage Accuracy: ±1% at +25℃

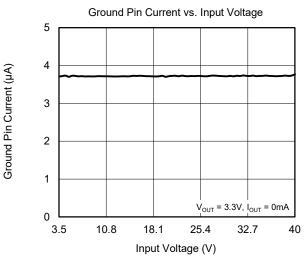

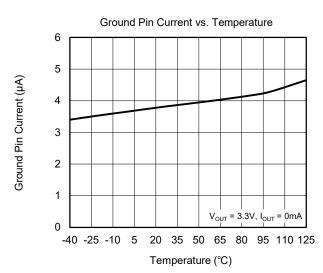

- Low Quiescent Current: 3.8μA (TYP)

- Low Dropout Voltage: 750mV (TYP) at 500mA

- Current Limiting and Thermal Protection

- Support Power-Good Indicator Function

- With Output Automatic Discharge

- Stable with Small Case Size Ceramic Capacitors

- -40°C to +125°C Operating Temperature Range

- Available in a Green SOIC-8 (Exposed Pad)

Package

#### **APPLICATIONS**

Battery-Powered Equipment

Ultra-Low Power System

Medical Equipment

Industrial Equipment

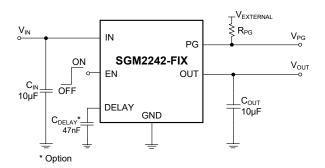

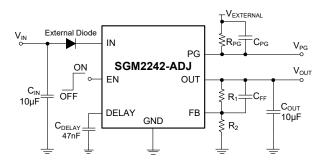

#### TYPICAL APPLICATION

**Fixed Output Voltage Version**

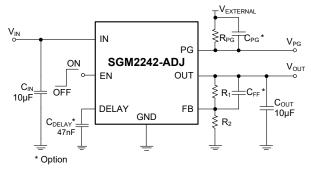

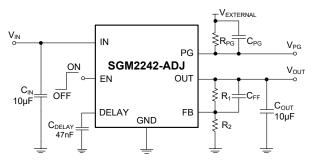

Adjustable Output Voltage Version

**Figure 1. Typical Application Circuits**

## PACKAGE/ORDERING INFORMATION

| MODEL       | PACKAGE<br>DESCRIPTION  | SPECIFIED<br>TEMPERATURE<br>RANGE | TEMPERATURE ORDERING |                         | PACKING<br>OPTION   |

|-------------|-------------------------|-----------------------------------|----------------------|-------------------------|---------------------|

| SGM2242-1.8 | SOIC-8<br>(Exposed Pad) | -40°C to +125°C                   | SGM2242-1.8XPS8G/TR  | SGM<br>24ZXPS8<br>XXXXX | Tape and Reel, 4000 |

| SGM2242-2.5 | SOIC-8<br>(Exposed Pad) | -40°C to +125°C                   | SGM2242-2.5XPS8G/TR  | SGM<br>250XPS8<br>XXXXX | Tape and Reel, 4000 |

| SGM2242-3.0 | SOIC-8<br>(Exposed Pad) | -40°C to +125°C                   | SGM2242-3.0XPS8G/TR  | SGM<br>251XPS8<br>XXXXX | Tape and Reel, 4000 |

| SGM2242-3.3 | SOIC-8<br>(Exposed Pad) | -40°C to +125°C                   | SGM2242-3.3XPS8G/TR  | SGM<br>1X6XPS8<br>XXXXX | Tape and Reel, 4000 |

| SGM2242-3.6 | SOIC-8<br>(Exposed Pad) | -40°C to +125°C                   | SGM2242-3.6XPS8G/TR  | SGM<br>252XPS8<br>XXXXX | Tape and Reel, 4000 |

| SGM2242-4.2 | SOIC-8<br>(Exposed Pad) | -40°C to +125°C                   | SGM2242-4.2XPS8G/TR  | SGM<br>253XPS8<br>XXXXX | Tape and Reel, 4000 |

| SGM2242-5.0 | SOIC-8<br>(Exposed Pad) | -40°C to +125°C                   | SGM2242-5.0XPS8G/TR  | SGM<br>1X5XPS8<br>XXXXX | Tape and Reel, 4000 |

| SGM2242-8.0 | SOIC-8<br>(Exposed Pad) | -40°C to +125°C                   | SGM2242-8.0XPS8G/TR  | SGM<br>254XPS8<br>XXXXX | Tape and Reel, 4000 |

| SGM2242-9.0 | SOIC-8<br>(Exposed Pad) | -40°C to +125°C                   | SGM2242-9.0XPS8G/TR  | SGM<br>255XPS8<br>XXXXX | Tape and Reel, 4000 |

| SGM2242-12  | SOIC-8<br>(Exposed Pad) | -40°C to +125°C                   | SGM2242-12XPS8G/TR   | SGM<br>256XPS8<br>XXXXX | Tape and Reel, 4000 |

| SGM2242-ADJ | SOIC-8<br>(Exposed Pad) | -40°C to +125°C                   | SGM2242-ADJXPS8G/TR  | SGM<br>1X4XPS8<br>XXXXX | Tape and Reel, 4000 |

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### **ABSOLUTE MAXIMUM RATINGS**

| IN, EN to GND                              | 0.3V to 42V |

|--------------------------------------------|-------------|

| OUT, FB to GND                             | 0.3V to 42V |

| PG to GND                                  | 0.3V to 42V |

| DELAY to GND                               | 0.3V to 6V  |

| Package Thermal Resistance                 |             |

| SOIC-8 (Exposed Pad), θ <sub>JA</sub>      | 40°C/W      |

| SOIC-8 (Exposed Pad), θ <sub>JB</sub>      | 16.7°C/W    |

| SOIC-8 (Exposed Pad), θ <sub>JC(TOP)</sub> | 55.9°C/W    |

| SOIC-8 (Exposed Pad), θ <sub>JC(BOT)</sub> | 6°C/W       |

| Junction Temperature                       | +150°C      |

| Storage Temperature Range                  |             |

| Lead Temperature (Soldering, 10s)          | +260°C      |

| ESD Susceptibility (1)(2)                  |             |

| HBM                                        | ±2000V      |

| CDM                                        | ±1000V      |

#### NOTES:

- 1. For human body model (HBM), all pins comply with ANSI/ESDA/JEDEC JS-001 specifications.

- 2. For charged device model (CDM), all pins comply with ANSI/ESDA/JEDEC JS-002 specifications.

#### RECOMMENDED OPERATING CONDITIONS

| Supply Voltage Range, V <sub>IN</sub>          | 3V to 40V     |

|------------------------------------------------|---------------|

| Enable Input Voltage Range, V <sub>EN</sub>    | 3V to 40V     |

| Input Effective Capacitance, C <sub>IN</sub>   | 1µF (MIN)     |

| Output Effective Capacitance, C <sub>OUT</sub> | .1μF to 100μF |

| Operating Junction Temperature Range4          | 0°C to +125°C |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

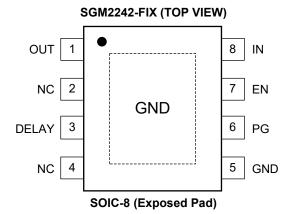

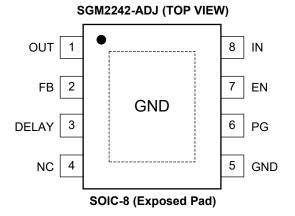

## **PIN CONFIGURATIONS**

## **PIN DESCRIPTION**

| PIN         | NAME  | FUNCTION                                                                                                                                                                                                                           |

|-------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | OUT   | Regulator Output Pin. It is recommended to use a ceramic capacitor with effective capacitance in the range of $1\mu F$ to $100\mu F$ to ensure stability. This ceramic capacitor should be placed as close as possible to OUT pin. |

|             | NC    | No Connection (Fixed Version Only).                                                                                                                                                                                                |

| 2           | FB    | Feedback Voltage Input Pin (adjustable voltage version only). Connect this pin to the midpoint of an external resistor divider to adjust the output voltage. Place the resistors as close as possible to this pin.                 |

| 3           | DELAY | Power-Good Delay Pin. Keep this pin floating when it is not in use.                                                                                                                                                                |

| 4           | NC    | No Connection.                                                                                                                                                                                                                     |

| 5           | GND   | Ground.                                                                                                                                                                                                                            |

| 6           | PG    | Power-Good Indicator Output Pin. An open-drain, active-high output that indicates the status of V <sub>OUT</sub> . When the output voltage reaches PG <sub>HTH</sub> of the target, the PG pin goes into a high-impedance state.   |

| 7           | EN    | Enable Pin. Drive EN high to turn on the regulator. Drive EN low to turn off the regulator.                                                                                                                                        |

| 8           | IN    | Input Supply Voltage Pin. It is recommended to use a 2.2µF or larger ceramic capacitor from IN pin to ground to get good power supply decoupling. This ceramic capacitor should be placed as close as possible to IN pin.          |

| Exposed Pad | GND   | Exposed Pad. Connect it to GND internally. Connect it to a large ground plane to maximize thermal performance. This pad is not an electrical connection point.                                                                     |

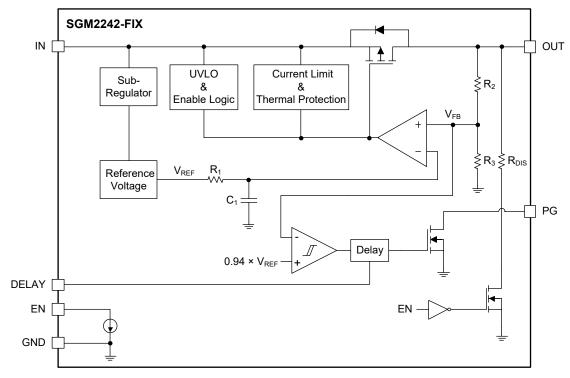

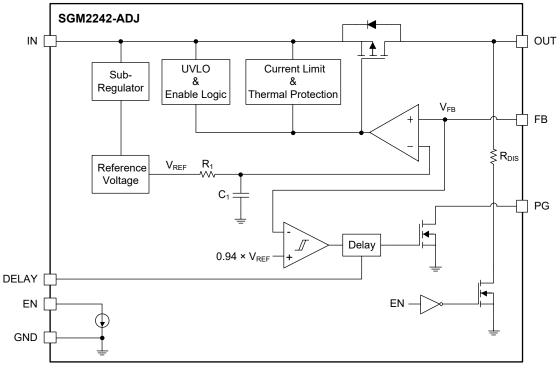

## **FUNCTIONAL BLOCK DIAGRAMS**

Figure 2. Block Diagram of Fixed Output Version

Figure 3. Block Diagram of Adjustable Output Version

## **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = (V_{OUT(NOM)} + 1.5V) \text{ or } 3V \text{ (whichever is greater)}, \ C_{IN} = 10 \mu F, \ C_{OUT} = 10 \mu F, \ C_{FF} = 0 nF, \ T_J = -40 ^{\circ} C \ \text{ to } +125 ^{\circ} C \ ^{(1)}, \ \text{typical values}$

are at  $T_A = +25$ °C, unless otherwise noted.)

| PARAMETER                          | SYMBOL                                                                      |                                                                    | CONDITION                                   |                                                      |       | TYP     | MAX    | UNITS     |

|------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------|------------------------------------------------------|-------|---------|--------|-----------|

| Input Voltage Range                | V <sub>IN</sub>                                                             |                                                                    |                                             |                                                      | 3     |         | 40     | V         |

| Output Voltage Range               | V <sub>out</sub>                                                            |                                                                    |                                             | 1.25                                                 |       | 24      | V      |           |

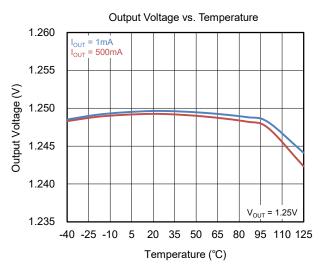

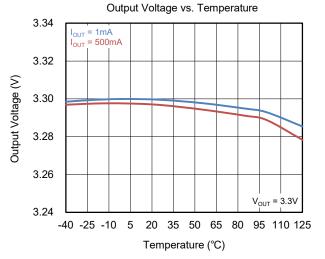

| Outsid Maltana Assuman             | .,                                                                          | $V_{IN} = (V_{OUT(NOM)} + 1.5V)$                                   | ) to 40V, T <sub>J</sub> = +25°C            |                                                      | -1    |         | +1     | 0/        |

| Output Voltage Accuracy            | V <sub>OUT</sub>                                                            | $I_{OUT} = 1 \text{mA} \text{ to } 500 \text{mA}$                  |                                             | $T_J = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | -2    |         | +1.5   | %         |

| Facility of the sec                | V                                                                           | $V_{IN} = (V_{OUT(NOM)} + 1.5V)$                                   | to 40V,                                     | T <sub>J</sub> = +25°C                               | 1.237 | 1.25    | 1.263  | V         |

| Feedback Voltage                   | $V_{FB}$                                                                    | I <sub>OUT</sub> = 1mA to 500mA                                    |                                             | $T_J = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | 1.225 | 1.25    | 1.269  |           |

| FB Pin Input Current               | I <sub>FB</sub>                                                             | V <sub>FB</sub> = 1.3V                                             |                                             |                                                      |       | 1       | 100    | nA        |

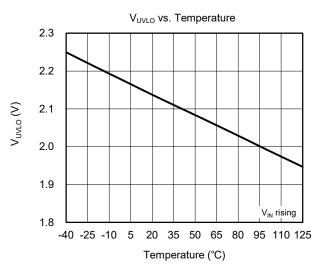

| Under-Voltage Lockout              | V <sub>UVLO</sub>                                                           | V <sub>IN</sub> rising                                             |                                             |                                                      | 1.75  | 2.12    | 2.5    | V         |

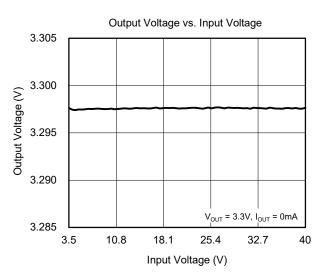

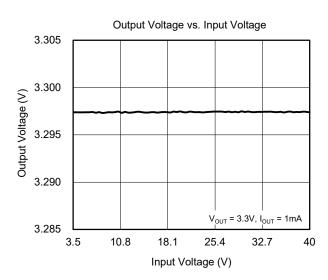

| Line Regulation                    | $\frac{\Delta V_{\text{OUT}}}{\Delta V_{\text{IN}} \times V_{\text{OUT}}}$  | $V_{IN} = (V_{OUT(NOM)} + 1.5V)$                                   | to 40V, I <sub>OU</sub>                     | <sub>Γ</sub> = 1mA                                   |       | 0.0003  | 0.01   | %/V       |

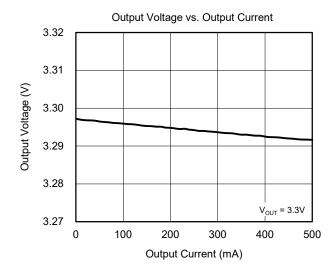

| Load Regulation                    | $\frac{\Delta V_{\text{OUT}}}{\Delta I_{\text{OUT}} \times V_{\text{OUT}}}$ | I <sub>OUT</sub> = 1mA to 500mA                                    |                                             |                                                      |       | 0.00005 | 0.0015 | %/mA      |

|                                    |                                                                             |                                                                    | 1.8V ≤ V <sub>OUT</sub>                     | $I_{(NOM)} < 3.3V, I_{OUT} = 500mA$                  |       | 860     | 1500   |           |

| Dropout Voltage                    | $V_{DROP}$                                                                  | $V_{OUT} = 95\% \times V_{OUT(NOM)}$                               | V <sub>OUT(NOM)</sub> ≥                     | 3.3V, I <sub>OUT</sub> = 150mA                       |       | 220     | 450    | mV        |

|                                    |                                                                             |                                                                    | $V_{OUT(NOM)} \ge 3.3V$ , $I_{OUT} = 500mA$ |                                                      |       | 750     | 1400   |           |

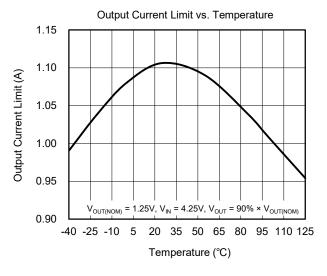

| Output Current Limit               | I <sub>LIMIT</sub>                                                          | $V_{IN} = V_{OUT} + 3V, V_{OUT} =$                                 | 90% × V <sub>OU</sub>                       | Γ(NOM)                                               | 0.51  | 1.1     |        | Α         |

| Output Short-Circuit Current       | I <sub>SHORT</sub>                                                          | $V_{IN} = V_{OUT(NOM)} + 3V, V_{OU}$                               | $V_{IN} = V_{OUT(NOM)} + 3V, V_{OUT} = 0V$  |                                                      |       | 470     |        | mA        |

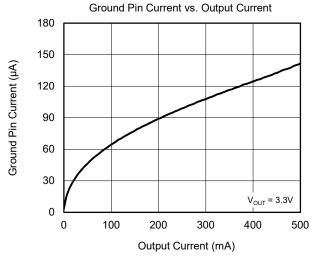

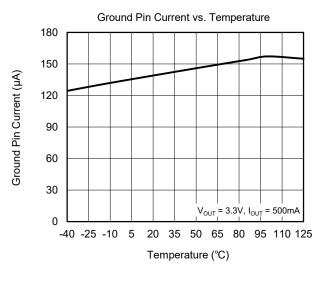

| Ground Pin Current                 | I <sub>GND</sub>                                                            | I <sub>OUT</sub> = 0mA                                             |                                             |                                                      |       | 3.8     | 8      | μA        |

| Ground i in Garrent                | IGND                                                                        | I <sub>OUT</sub> = 500mA                                           |                                             |                                                      | 140   | 300     | μ, ,   |           |

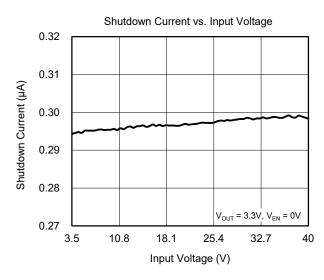

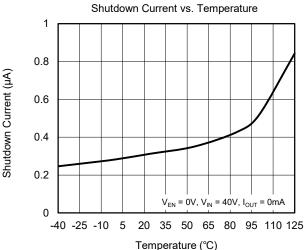

| Shutdown Supply Current            | I <sub>SHDN</sub>                                                           | $V_{EN} = 0V$ , $V_{IN} = 3V$ to $40V$                             |                                             |                                                      |       | 0.3     | 1.5    | μΑ        |

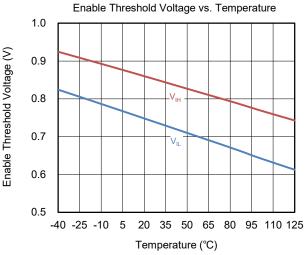

| EN Pin High-level Input Voltage    | $V_{IH}$                                                                    | V <sub>IN</sub> = 3V to 40V                                        |                                             |                                                      | 1.5   |         | 40     | V         |

| EN Pin Low-level Input Voltage     | $V_{IL}$                                                                    | V <sub>IN</sub> = 3V to 40V                                        |                                             |                                                      | 0     |         | 0.3    | V         |

| EN Pin Input Current               | I <sub>EN</sub>                                                             | $V_{EN} = 0V, V_{IN} = 40V$                                        |                                             |                                                      |       | 0.01    | 1      | μA        |

| ENT III III put Guireit            | IEN                                                                         | $V_{EN} = 40V, V_{IN} = 40V$                                       |                                             |                                                      |       | 0.1     | 1      | μΛ        |

| Output Discharge Resistance        | R <sub>DIS</sub>                                                            | V <sub>EN</sub> = 0V                                               |                                             |                                                      |       | 215     |        | Ω         |

|                                    |                                                                             |                                                                    |                                             |                                                      |       | 1.1     | 1.8    |           |

| Turn-On Time                       | t <sub>ON</sub>                                                             | From assertion of $V_{EN}$<br>$V_{OUT} = 90\% \times V_{OUT(NOM)}$ |                                             | $V_{OUT(NOM)} = 3.3V$                                |       | 1.1     | 2.0    | ms        |

|                                    |                                                                             |                                                                    |                                             | $V_{OUT(NOM)} = 5V$                                  |       | 1.4     | 2.5    |           |

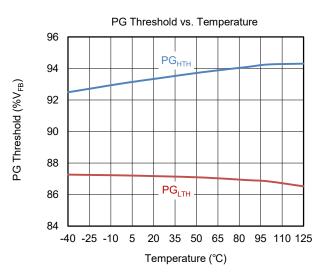

| PG High Threshold                  | PG <sub>HTH</sub>                                                           | V <sub>OUT</sub> rising                                            |                                             |                                                      | 90    | 94      | 97     | $%V_{FB}$ |

| PG Low Threshold                   | $PG_{LTH}$                                                                  | V <sub>OUT</sub> falling                                           |                                             |                                                      | 84    | 87      | 90     | $%V_{FB}$ |

| PG Pin Low-Level Output<br>Voltage | $V_{PG(LO)}$                                                                | I <sub>SINK</sub> = 1mA                                            |                                             |                                                      |       | 0.1     | 0.3    | V         |

| PG Pin Leakage Current             | $I_{PG(LKG)}$                                                               | V <sub>PG</sub> = 5V                                               |                                             |                                                      |       | 1       | 500    | nA        |

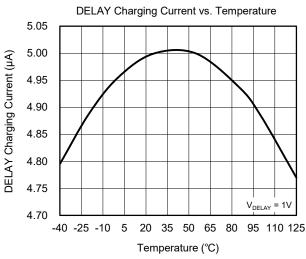

| DELAY Charging Current             | I <sub>DLY</sub>                                                            | $V_{DELAY} = 1V$                                                   |                                             |                                                      |       | 5       | 10     | μA        |

| DELAY Rising Threshold             | $V_{HDLY}$                                                                  |                                                                    |                                             |                                                      | 1.3   | 1.6     | 1.9    | V         |

| DELAY Falling Threshold            | $V_{LDLY}$                                                                  |                                                                    |                                             |                                                      | 0.2   | 0.35    | 0.7    | V         |

| PG Delay Time                      | t <sub>PGD</sub>                                                            | C <sub>DELAY</sub> = 47nF                                          |                                             |                                                      |       | 12      | 30     | ms        |

| PG Reaction Time                   | t <sub>PGR</sub>                                                            | C <sub>DELAY</sub> = 47nF                                          |                                             |                                                      |       | 0.6     |        | μs        |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = (V_{OUT(NOM)} + 1.5V)$  or 3V(whichever is greater),  $C_{IN} = 10\mu F$ ,  $C_{OUT} = 10\mu F$ ,  $C_{FF} = 0nF$ ,  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$  (1), typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                    | SYMBOL            | CONDITION                                                                  |            |  | TYP | MAX | UNITS                |

|------------------------------|-------------------|----------------------------------------------------------------------------|------------|--|-----|-----|----------------------|

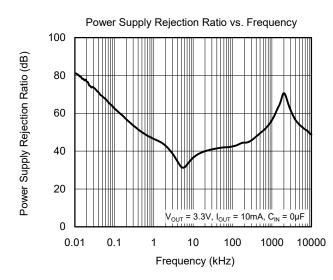

|                              |                   |                                                                            | f = 100Hz  |  | 62  |     |                      |

| Power Supply Rejection Ratio | PSRR              | $V_{OUT(NOM)} = 3.3V$ , $I_{OUT} = 10mA$                                   | f = 1kHz   |  | 46  |     | dB                   |

|                              |                   |                                                                            | f = 100kHz |  | 43  |     |                      |

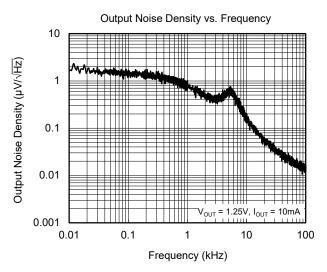

| Output Voltage Noise         | e <sub>n</sub>    | f = 10Hz to 100kHz, V <sub>OUT(NOM)</sub> = 1.25V, I <sub>OUT</sub> = 10mA |            |  | 58  |     | $\mu V_{\text{RMS}}$ |

| Thermal Shutdown Temperature | T <sub>SHDN</sub> |                                                                            |            |  | 160 |     | °C                   |

| Thermal Shutdown Hysteresis  | $\Delta T_{SHDN}$ |                                                                            |            |  | 30  |     | °C                   |

#### NOTE:

1. Tested under pulse load conditions, so  $T_J \approx T_A$ .

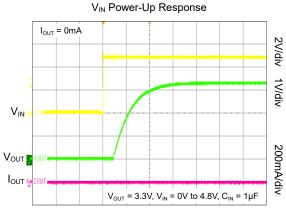

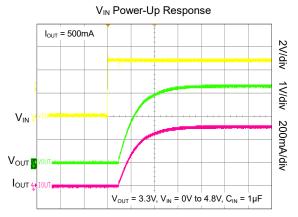

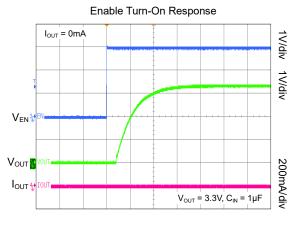

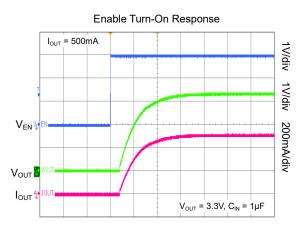

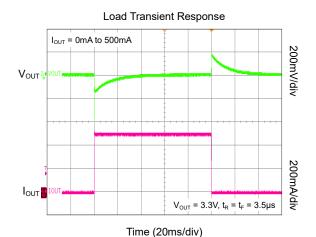

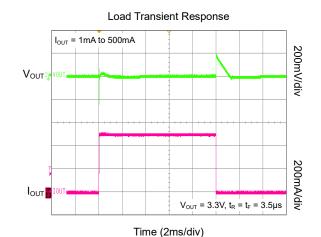

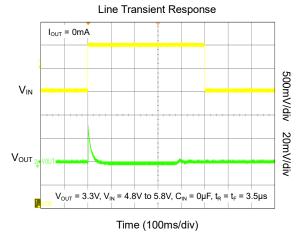

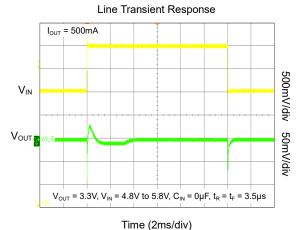

#### TYPICAL PERFORMANCE CHARACTERISTICS

Time (500µs/div)

Time (500µs/div)

Time (500µs/div)

#### APPLICATION INFORMATION

The SGM2242 is a high voltage, low quiescent current and low dropout LDO and provides 500mA output current. These features make the device a reliable solution to solve many challenging problems in the generation of clean and accurate power supply. The high performance also makes the SGM2242 useful in a variety of applications. The SGM2242 provides protection functions for output overload and overheating.

#### Input Capacitor Selection (C<sub>IN</sub>)

The input decoupling capacitor should be placed as close as possible to the IN pin to ensure the device stability.  $2.2\mu F$  or larger X7R or X5R ceramic capacitor is selected to get good dynamic performance.

When  $V_{\text{IN}}$  is required to provide large current instantaneously, a large effective input capacitor is required. Multiple input capacitors can limit the input tracking inductance. Adding more input capacitors is available to restrict the ringing and to keep it below the device absolute maximum ratings. For  $C_{\text{OUT}}$  with larger capacitance, it is recommended to choose the larger capacitance  $C_{\text{IN}}$ .

#### Output Capacitor Selection (C<sub>OUT</sub>)

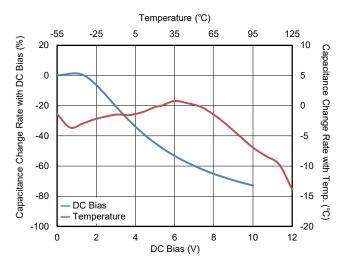

One or more output capacitors are required to maintain the stability of the LDO, and the output capacitors should be placed as close as possible to the OUT pin. In addition, in order to obtain the best transient performance, it is recommended to use X7R and X5R ceramic capacitors as output capacitors. Ceramic capacitors have low equivalent series resistance (ESR), excellent temperature and DC bias characteristics. However, it cannot be ignored that the effective capacitance of ceramic capacitors is affected by temperature, DC bias and package size.

For example, Figure 4 shows the capacitance and DC bias and temperature characteristics of 0805, 10V,  $10\mu F\pm 10\%$ , X7R capacitor. Therefore, it is necessary to evaluate whether the effective capacitance of the output capacitor can meet the stability requirements of the LDO in practical applications. In general, a capacitor in higher voltage rating and a larger package exhibits better stability, and the effective capacitance can be obtained from the manufacturer datasheet.

Figure 4. Capacitance vs. DC Bias and Temperature Characteristics

The SGM2242 requires a minimum effective capacitance of  $1\mu F$  for  $C_{OUT}$  to ensure stability. Additionally,  $C_{OUT}$  with larger capacitance and lower ESR will help increase the high frequency PSRR and improve the load transient response.

#### **Adjustable Regulator**

The output voltage of the SGM2242-ADJ can be adjusted from 1.25V to 24V. The FB pin will be connected to two external resistors as shown in Figure 5. The output voltage is determined by the following equation:

$$V_{OUT} = V_{FB} \times \left(1 + \frac{R_1}{R_2}\right) \tag{1}$$

where:

$V_{OUT}$  is output voltage and  $V_{FB}$  is the internal voltage reference,  $V_{FB}$  = 1.25V.  $R_1$  and  $R_2$  can be calculated for any output voltage range using equation 1. It is recommended that the  $R_2$  resistance be less than  $40k\Omega$  and  $C_{FF}$  = 1nF.

Figure 5. Adjustable Output Voltage Application

## **APPLICATION INFORMATION (continued)**

#### **Enable Operation**

The SGM2242 uses the EN pin to enable/disable the device and to deactivate/activate the output automatic discharge function.

When the EN pin voltage is lower than 0.3V, the device is in shutdown state. There is no current flowing from IN to OUT pins. In this state, the automatic discharge transistor is active to discharge the output voltage through a 215 $\Omega$  (TYP) resistor and the PG output is pulled down.

When the EN pin voltage is higher than 1.5V, the device is in active state. The output voltage is regulated to the expected value and the automatic discharge transistor is turned off.

#### **Power-Good Function**

The SGM2242 features PG function for monitoring the feedback voltage, so as to reflect the state of the output voltage. When the output voltage is lower than PG<sub>LTH</sub>, the PG pin open-drain engages and pulls the PG pin close to GND. When the output voltage is higher than PG<sub>HTH</sub>, the PG pin is indicated as high impedance. Connecting the PG pin to an external power supply via a pull-up resistor enables any downstream device to receive a power-good valid logic signal for sequencing. The resistance of the pull-up resistor is recommended to be between  $10k\Omega$  and  $100k\Omega$ .

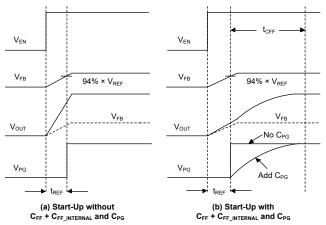

Both the fixed-voltage and adjustable-voltage versions of the SGM2242 integrate an internal feedforward capacitor ( $C_{FF\_INTERNAL}$ , typical value 10pF). When an external feed-forward capacitor ( $C_{FF}$ ) is added in application, the total LDO startup time constant increases by approximately  $3 \times R_1 \times (C_{FF} + C_{FF\_INTERNAL})$ .

If the Power-Good (PG) output time constant remains unchanged, the PG signal may not accurately indicate whether  $V_{\text{OUT}}$  has reached the expected voltage. To ensure a valid PG output, the following design configurations must be implemented to match the time constants.

Add a PG delay capacitor ( $C_{PG}$ ) and connect  $C_{PG}$  in parallel with the PG pull-up resistor ( $R_{PG}$ ) refer to Figure 5. Ensure the following condition is met:  $3 \times R_{PG} \times C_{PG} \ge 3 \times R_1 \times (C_{FF} + C_{FF})$  Internal).

For the adjustable version, refer to Figure 5 for  $R_1$  selection. For the fixed version, calculate  $R_1$  as follows:

$$R_1 = \left(\frac{V_{\text{OUT(NOM)}}}{1.25} - 1\right) \times 12M\Omega \tag{2}$$

Figure 6 shows the differences in PG signals when  $C_{\text{FF}}$  and  $C_{\text{PG}}$  are added. In Figure 6,  $t_{\text{REF}}$  is the time that takes for the  $V_{\text{FB}}$  voltage to rise from 0V to 94% ×  $V_{\text{REF}}$ ,  $t_{\text{CFF}}$  is the startup time contributed by  $C_{\text{FF}}$  and  $C_{\text{FF}}$  INTERNAL.

NOTE: Both (a) and (b) are under the condition of  $C_{DELAY} = 0$ nF.

Figure 6. Typical Power-Good Timing Diagram

The power-good (PG) delay period is determined by the external capacitor ( $C_{DELAY}$ ) connected to the DELAY pin. When the  $V_{FB}$  voltage reaches  $PG_{HTH}$  of the target, this adjustable delay function configures the required wait time before the PG pin asserts high and achieved by connecting an external capacitor between the DELAY pin and GND. When the DELAY pin is left floating, the delay time defaults to  $40\mu s$ . If a capacitor is connected between the DELAY pin and GND, the delay time is defined by the following equation:

$$t_{PGD} = 40\mu s + C_{DELAY} \times \frac{V_{HDLY}}{I_{DLY}}$$

(3)

Adjust the programmable PG delay ( $t_{PGD}$ ) (adjustable version only), if using the adjustable PG delay feature, set:  $t_{PGD} \ge 3 \times R_1 \times (C_{FF} + C_{FF} \text{ INTERNAL})$ .

The PG output is pulled down when the SGM2242 is in one of the following states, including disabled, thermal shutdown and UVLO.

## **APPLICATION INFORMATION (continued)**

#### **Reverse Current Protection**

The power transistor has an inherent body diode. This body diode will be forward biased when  $V_{OUT} > (V_{IN} + 0.3V)$ . When  $V_{OUT} > (V_{IN} + 0.3V)$ , the reverse current flowing from the OUT pin to the IN pin will damage the SGM2242. If  $V_{OUT} > (V_{IN} + 0.3V)$  event would happen in system, one external Schottky diode will be added between OUT pin and IN pin in circuit design to protect the SGM2242.

Figure 7. Reverse Protection Reference Design

#### **Output Current Limit Protection**

When overload events happen, the output current is internally limited to 1.1A (TYP). When the OUT pin is shorted to ground, the output current is internally limited to 470mA (TYP).

#### Thermal Shutdown

When the die temperature exceeds the threshold value of thermal shutdown, the SGM2242 will be in shutdown state and it will remain in this state until the die temperature decreases to +130°C. When the device enters thermal shutdown, the PG output is pulled low.

#### Power Dissipation (P<sub>D</sub>)

Power dissipation ( $P_D$ ) of the SGM2242 can be calculated by the equation  $P_D = (V_{IN} - V_{OUT}) \times I_{OUT}$ . The maximum allowable power dissipation ( $P_{D(MAX)}$ ) of the SGM2242 is affected by many factors, including the difference between junction temperature and ambient temperature ( $T_{J(MAX)} - T_A$ ), package thermal resistance from the junction to the ambient environment ( $\theta_{JA}$ ), the rate of ambient airflow and PCB layout.  $P_{D(MAX)}$  can be approximated by the following equation:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A)/\theta_{JA}$$

(4)

#### **Layout Guidelines**

To get good PSRR, low output noise and high transient response performance, the input and output bypass capacitors must be placed as close as possible to the IN pin and OUT pin separately.

## **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| AUGUST 2025 – REV.A.1 to REV.A.2                                  | Page |

|-------------------------------------------------------------------|------|

| Updated Electrical Characteristics section                        | 6    |

| JULY 2025 – REV.A to REV.A.1                                      | Page |

| Added SGM2242-1.8/2.5/3.3 to Package/Ordering Information section | 2    |

| Updated Absolute Maximum Ratings section                          | 3    |

| Updated Electrical Characteristics section                        | 6, 7 |

| Changes from Original (APRIL 2025) to REV.A                       | Page |

| Changed from product preview to production data                   | All  |

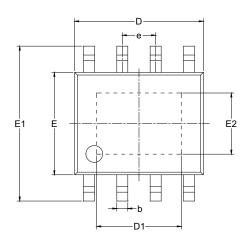

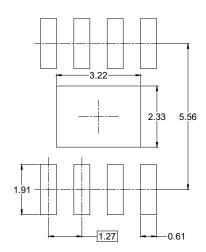

## **PACKAGE OUTLINE DIMENSIONS SOIC-8 (Exposed Pad)**

#### RECOMMENDED LAND PATTERN (Unit: mm)

| Symbol | Dimensions<br>In Millimeters |          |       |  |  |  |  |

|--------|------------------------------|----------|-------|--|--|--|--|

|        | MIN                          | NOM      | MAX   |  |  |  |  |

| А      |                              |          | 1.700 |  |  |  |  |

| A1     | 0.000                        | -        | 0.150 |  |  |  |  |

| A2     | 1.250                        | -        | 1.650 |  |  |  |  |

| b      | 0.330                        | -        | 0.510 |  |  |  |  |

| С      | 0.170                        | -        | 0.250 |  |  |  |  |

| D      | 4.700                        | -        | 5.100 |  |  |  |  |

| D1     | 3.020                        | -        | 3.420 |  |  |  |  |

| E      | 3.800                        | -        | 4.000 |  |  |  |  |

| E1     | 5.800                        | -        | 6.200 |  |  |  |  |

| E2     | 2.130                        | -        | 2.530 |  |  |  |  |

| е      |                              | 1.27 BSC |       |  |  |  |  |

| L      | 0.400                        | -        | 1.270 |  |  |  |  |

| θ      | 0°                           | -        | 8°    |  |  |  |  |

| ccc    |                              | 0.100    |       |  |  |  |  |

#### NOTES:

- This drawing is subject to change without notice.

The dimensions do not include mold flashes, protrusions or gate burrs.

- 3. Reference JEDEC MS-012.

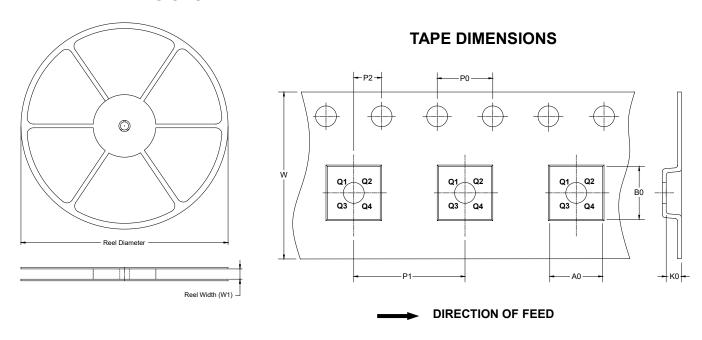

## TAPE AND REEL INFORMATION

#### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type         | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| SOIC-8 (Exposed Pad) | 13"              | 12.4                     | 6.40       | 5.40       | 2.10       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

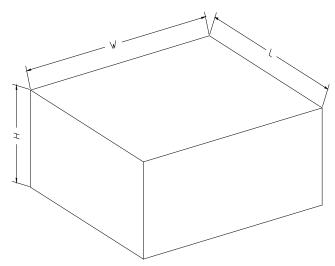

## **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

## **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |        |

|-----------|----------------|---------------|----------------|--------------|--------|

| 13″       | 386            | 280           | 370            | 5            | DD0002 |