## FEATURES

- 1- to 6-Cell Charging from a Variety of Input Types

- 3.5V to 30V Input Operating Voltage Range

- USB 2.0/3.0/3.1 (Type-C)/USB PD Input Current Support

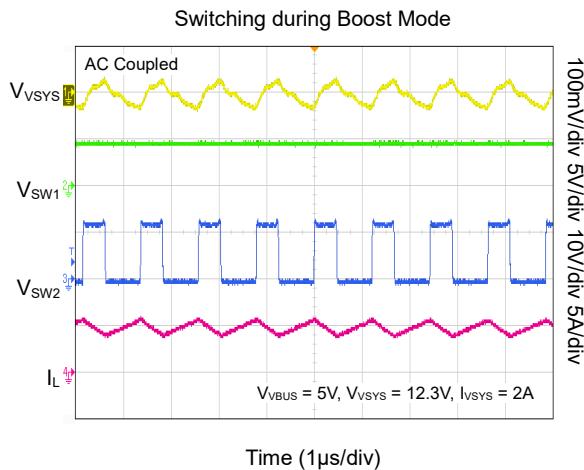

- Seamless Buck ↔ Buck-Boost ↔ Boost Transitions

- Input Overload Protection (IDPM and VDPM Regulation)

- Up to 16.2A/8.1A Charge Current with 128mA/64mA Resolution with 5mΩ/10mΩ Sensing Resistor

- Up to 10A/6.35A Input Current Limit with 100mA/50mA Resolution with 5mΩ/10mΩ Sensing Resistor

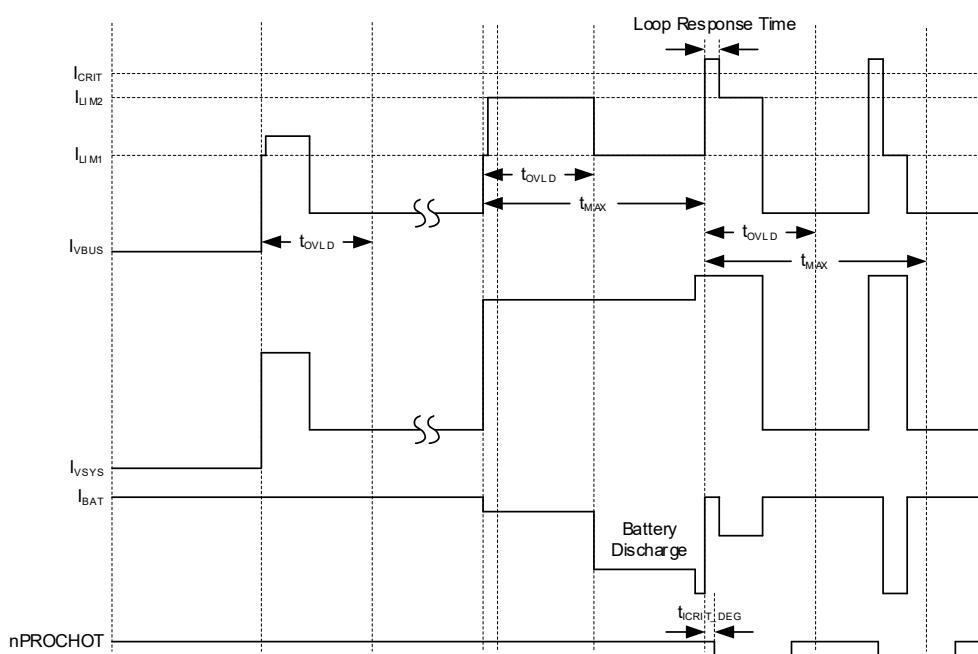

- CPU Throttling, Power and Current Monitoring

- Full nPROCHOT Profile

- Input Current Monitoring

- Battery Charge/Discharge Current Monitoring

- System Power Monitoring

- Narrow Voltage DC (NVDC) Power Path Management

- Instant-On with Depleted or No Battery

- Battery Supplementation if Adapter is Fully Loaded

- BATFET Ideal Diode Emulation in Supplement Mode

- Power-Up USB Port from Battery (USB OTG)

- 3V to 28.16V Adjustable OTG Voltage with 8mV Resolution

- Up to 12.7A/6.35A Output Current Limit with 100mA/50mA Resolution

- Programmable Switching Frequency Dithering to Improve EMI Performance

- Pass Through Mode (PTM) to Improve Efficiency

- V<sub>MIN</sub> Active Protection (VAP) Mode

- Fast Role Swap (FRS) Feature Following USB-PD Specification

- Input Current Optimizer Maximizes Power Extraction

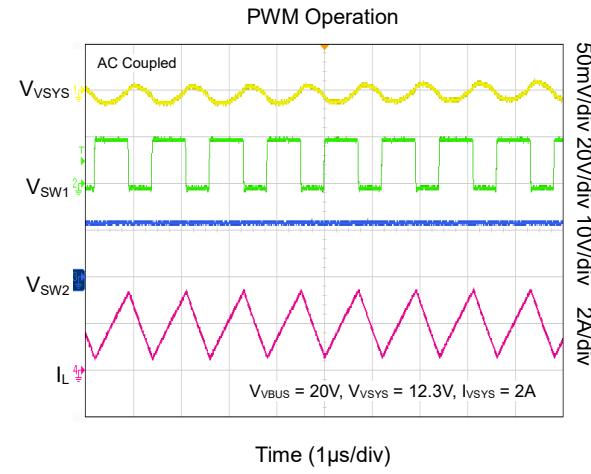

- 430kHz, 800kHz or 1.1MHz Selectable Switching Frequency

- Configurable Pure Buck Operation for Reduced External Component Cost

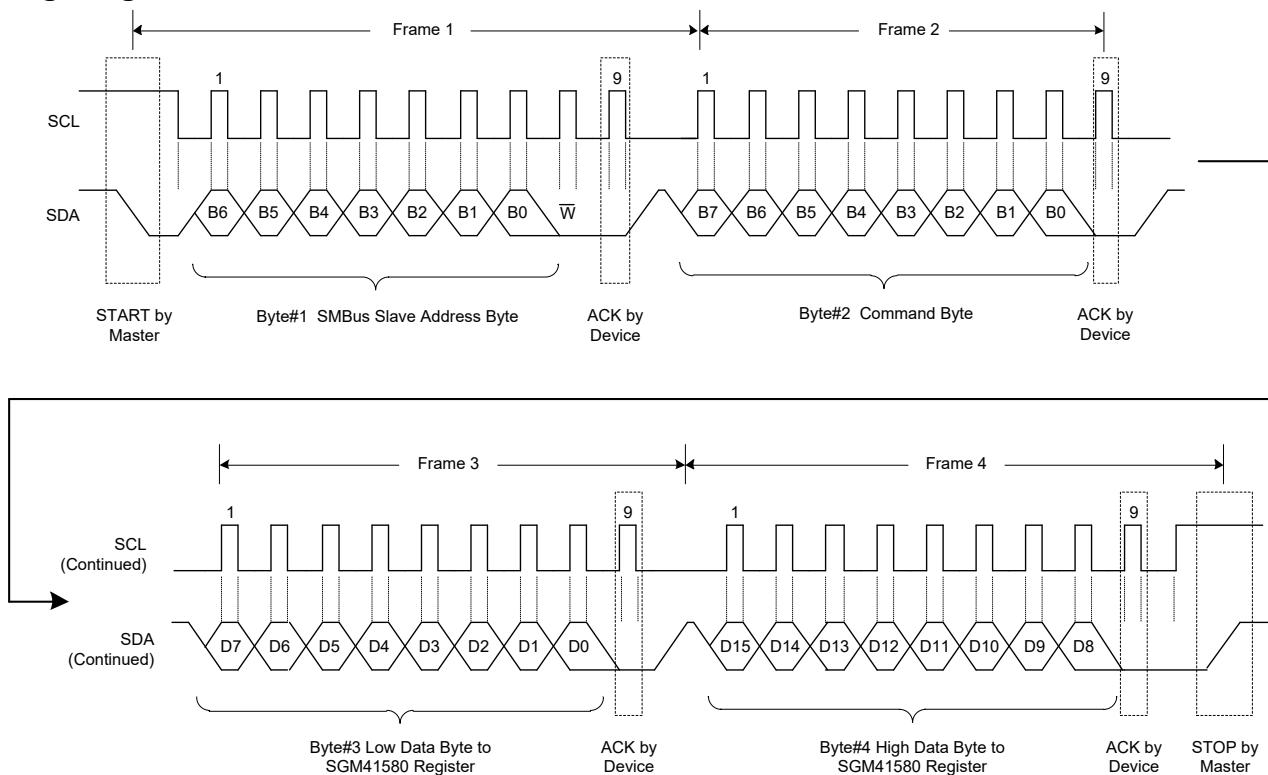

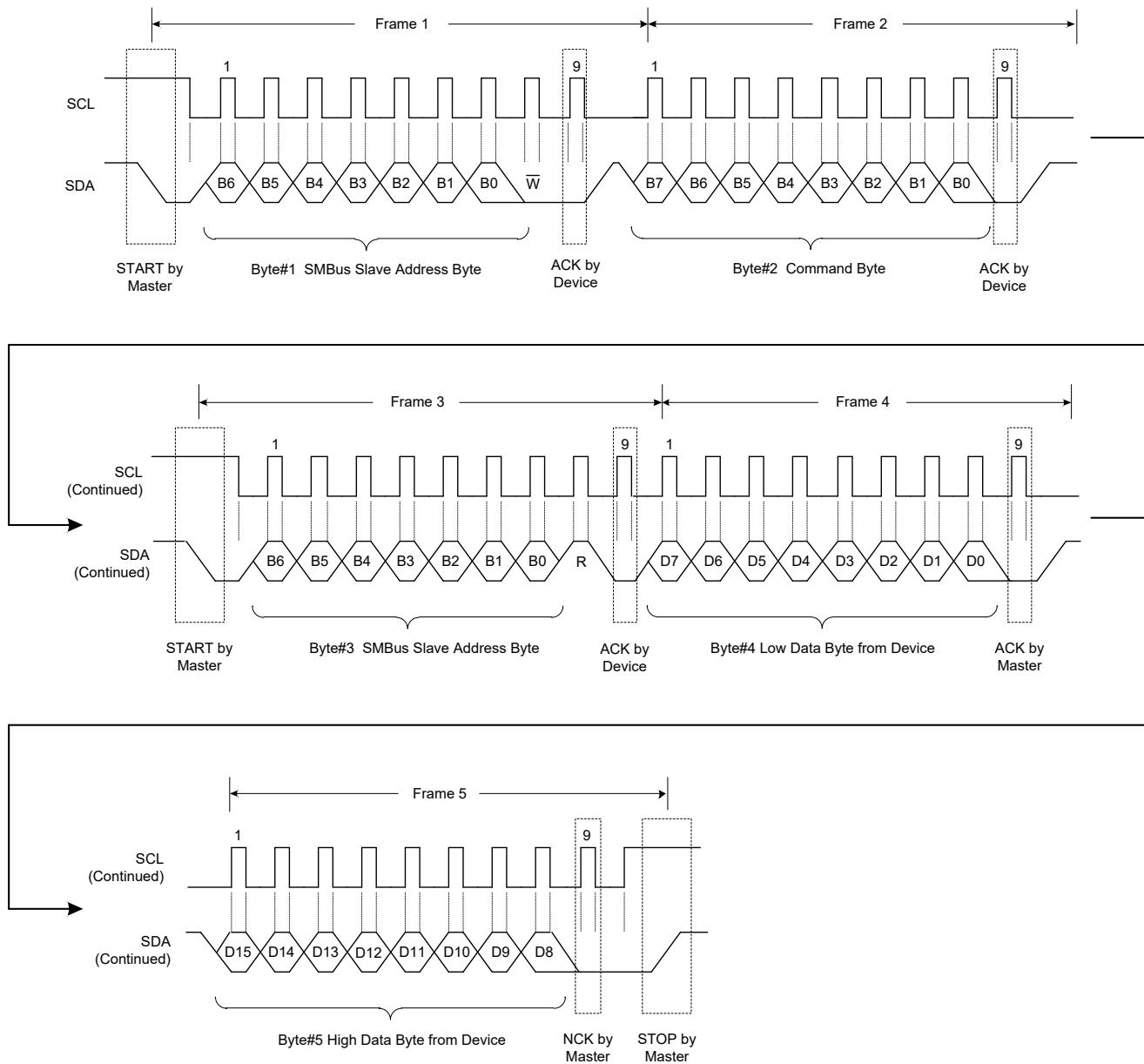

- SMBus Interface for Flexible System Configuration

- Input Current Limit Setting Pin (without SMBus)

- Integrated ADC for Voltage/Current/Power Monitoring

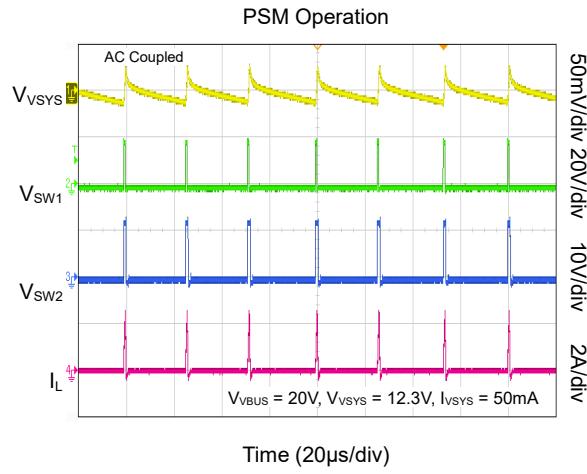

- Low Battery Quiescent Current

- High Accuracy

- ±0.4% for Charge Voltage Regulation

- ±2% for Charge Current Regulation

- ±2.5% for Input Current Regulation

- ±2.5% for Input/Charge Current Monitor

- ±3% for Power Monitor

- Safety

- Thermal Shutdown

- Input/System/Battery Over-Voltage Protection

- Input/MOSFET/Inductor Over-Current Protection

- Available in a Green TQFN-4x4-32AL Package

## APPLICATIONS

Bluetooth Speakers, Drones, IP Cameras, Detachable Power Supply

Portable Internet Devices and Accessory

Industrial and Medical Equipment

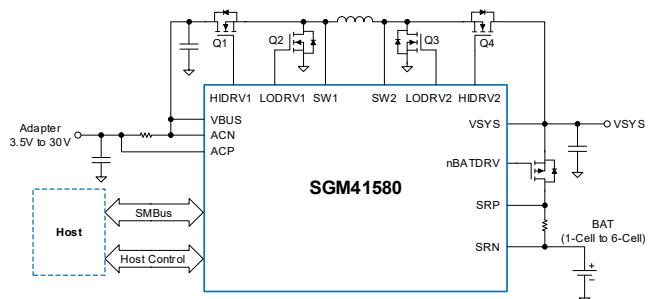

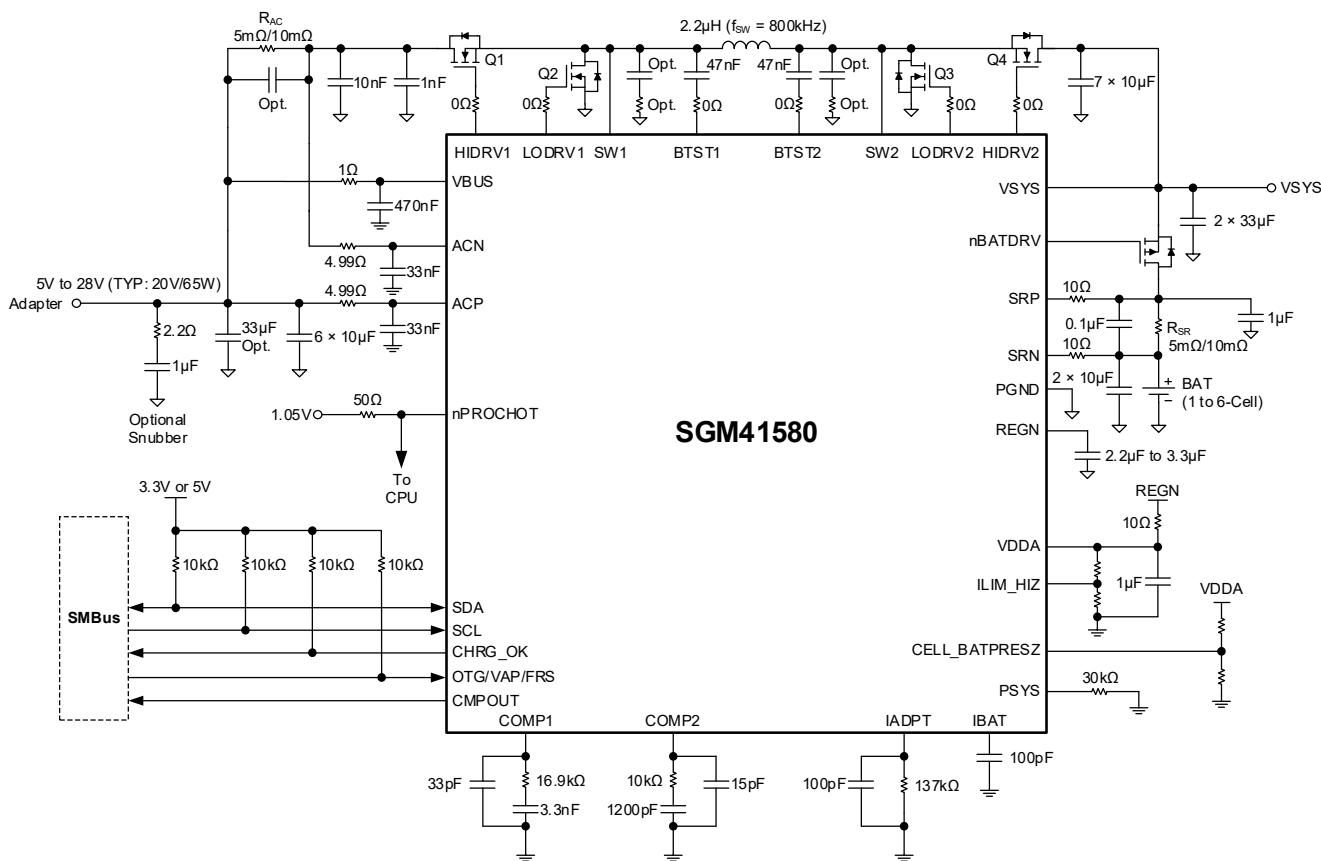

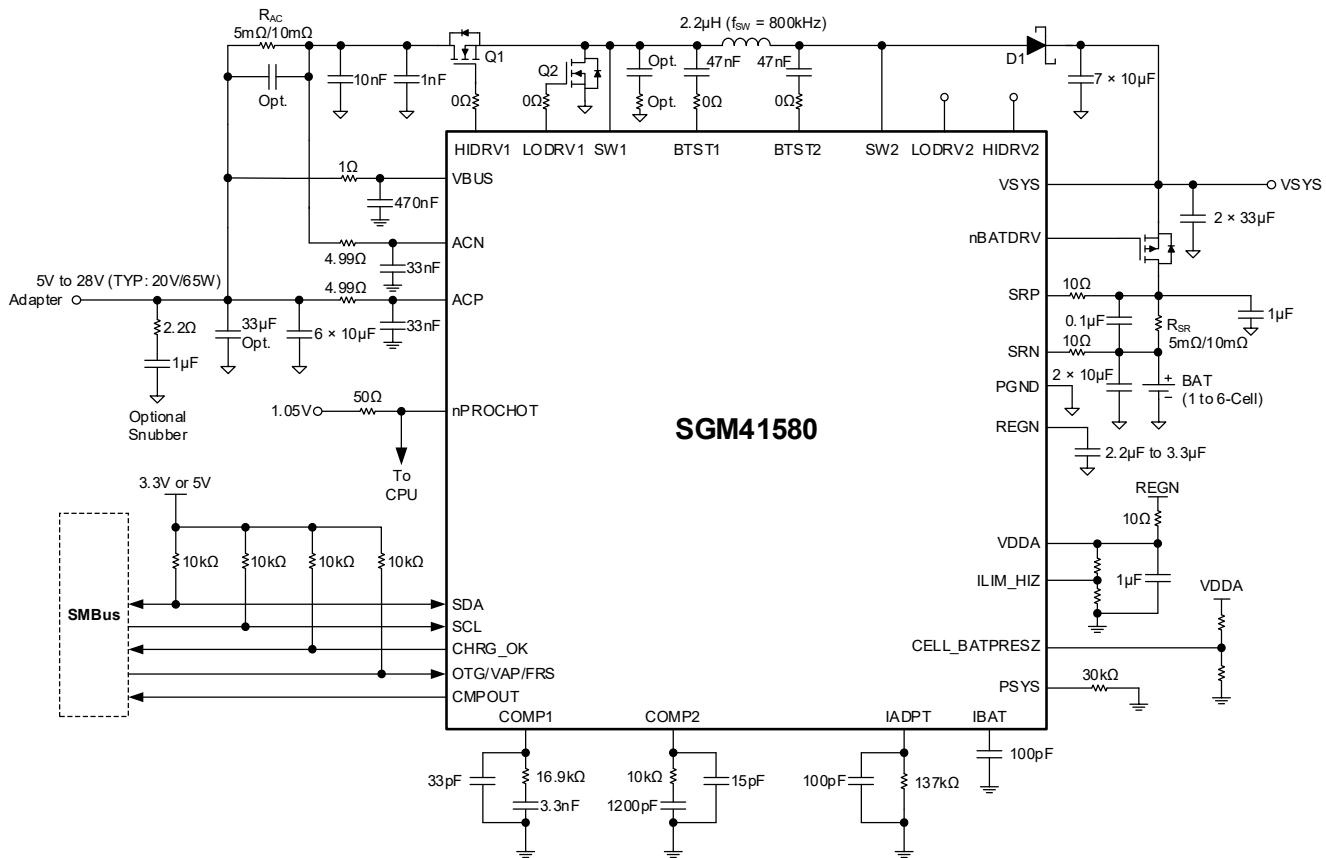

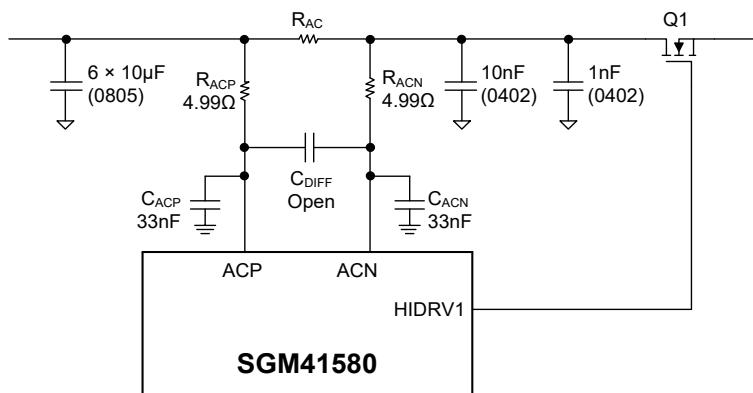

## SIMPLIFIED SCHEMATIC

Figure 1. Simplified Schematic

## GENERAL DESCRIPTION

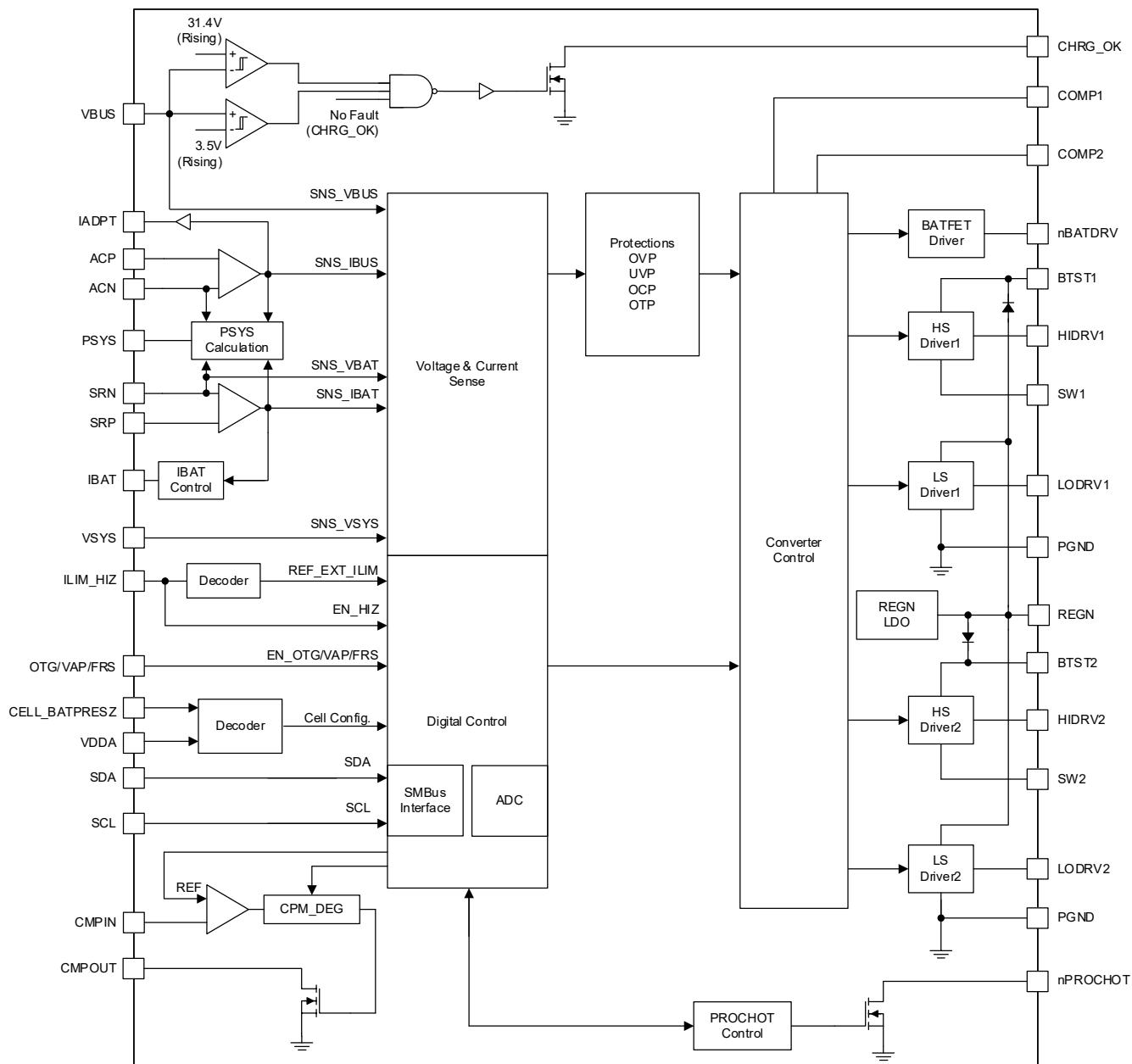

The SGM41580 is a synchronous Buck-Boost battery charge controller with NVDC power path management. It can provide high efficiency and low component count solution for 1-cell to 6-cell batteries charging applications.

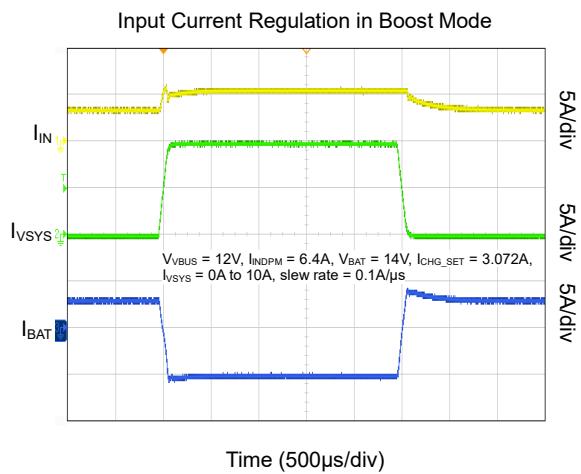

The system is regulated slightly to be higher than the battery voltage, but not lower than the programmable system minimum voltage. Therefore, the system power is maintained even if the battery is completely depleted or removed. Dynamic power management (DPM) feature is also included that automatically reduces the charge current if the input current or voltage limit is reached. If the system load continues to increase after reduction of charge current down to zero, the battery enters the supplement mode and both adapter and battery power the system.

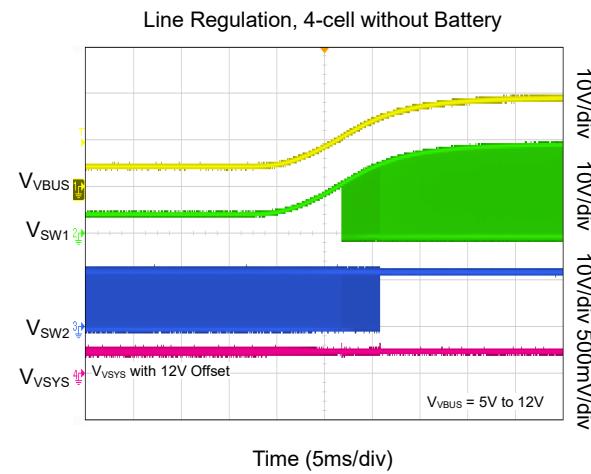

A wide range of input sources are supported for SGM41580, including traditional adapters, USB adapter and high voltage USB PD sources. The converter is configured as Buck, Boost or Buck-Boost during power-up, depending on the input source and battery conditions. The charger automatically switches among Buck, Boost and Buck-Boost without host control.

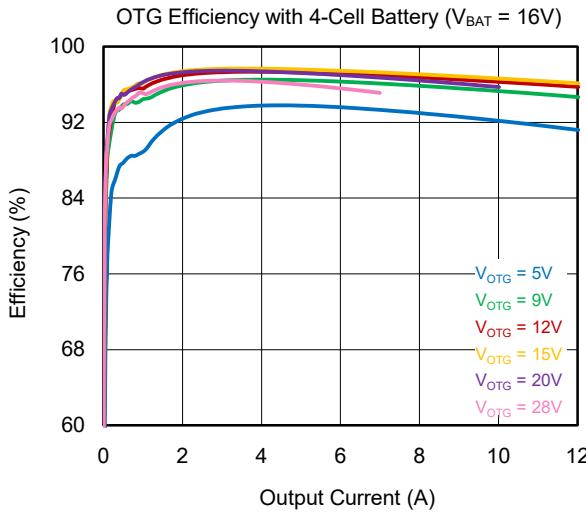

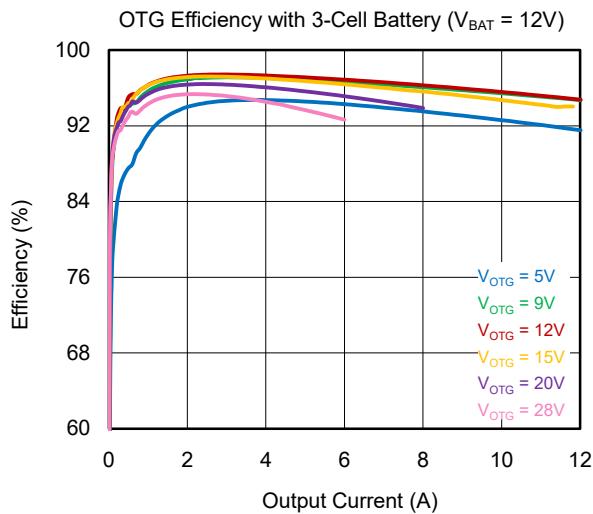

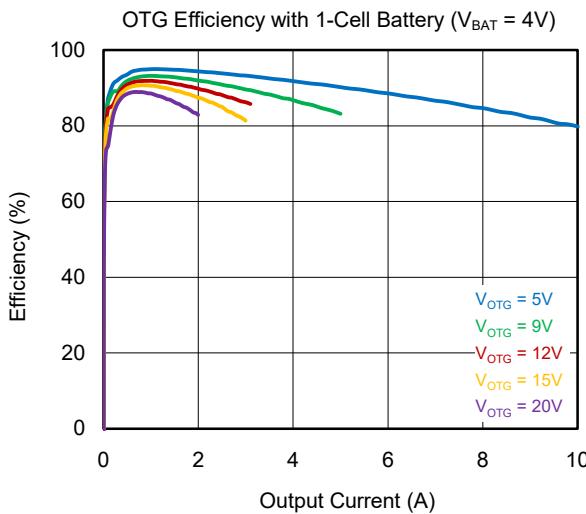

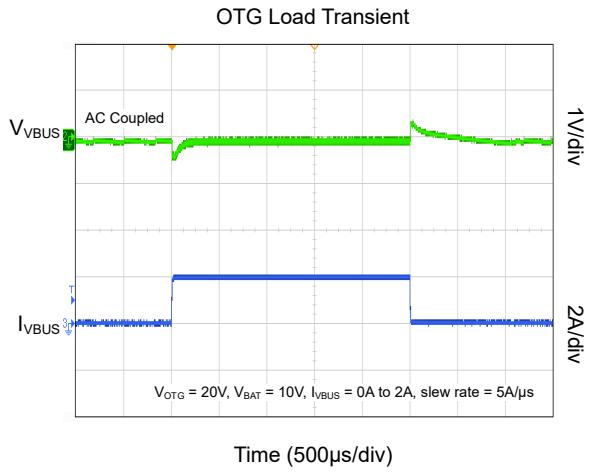

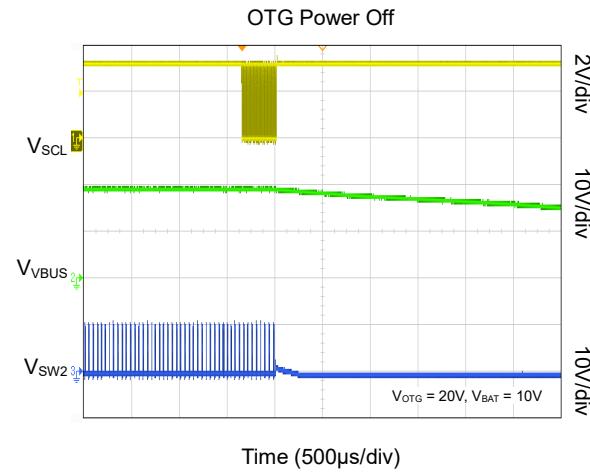

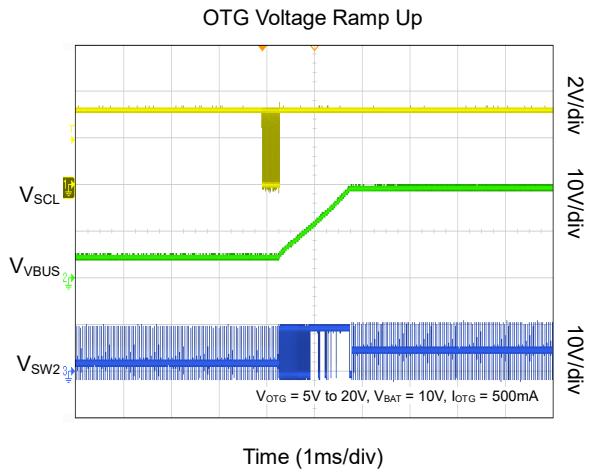

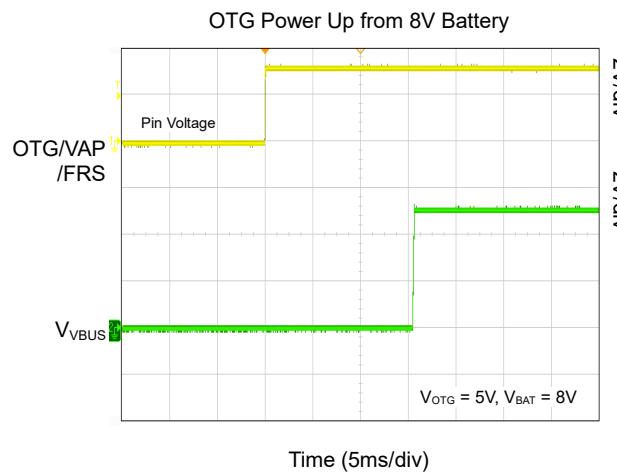

When the input source is absent, the SGM41580 can work in USB On-The-Go (OTG) mode to supply VBUS from battery. The OTG output voltage can be programmed from 3V to 28.16V with 8mV resolution. The slew rate of the output voltage transitions in OTG can be configured (by OTG current setting) to comply with the USB PD 3.0 PPS specifications and USB PD 3.1.

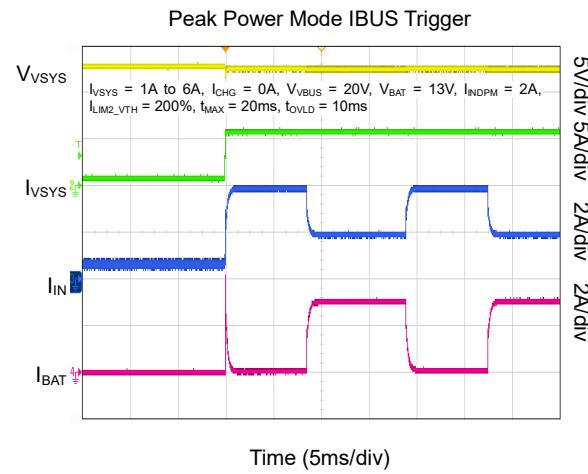

If there is no external load on the USB OTG port and the system is powered by battery-only, the  $V_{MIN}$  Active Protection (VAP) feature is supported. In VAP, the VBUS voltage is charged up by the battery and the energy is stored in the input decoupling capacitors. When the system requires peak power spike, the charge stored on the input capacitor discharges to maintain the system voltage at minimum system voltage.

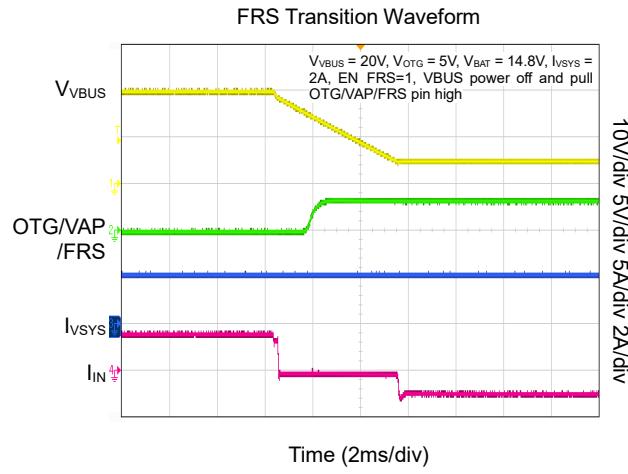

USB Type-C Power Delivery Fast Role Swap (FRS) allows fast power role transitions to prevent momentary power interruption to devices connected to a dock. Integrated FRS feature is provided by this device.

Switching frequency dithering helps reduce conducted EMI over the entire 150kHz to 30MHz range. Selectable dithering levels offer flexibility for various applications.

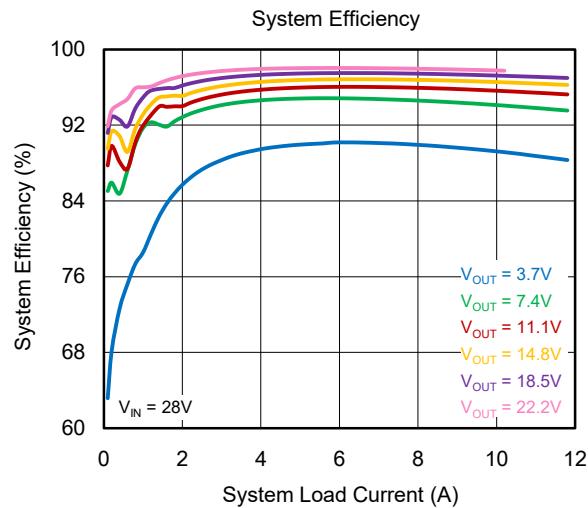

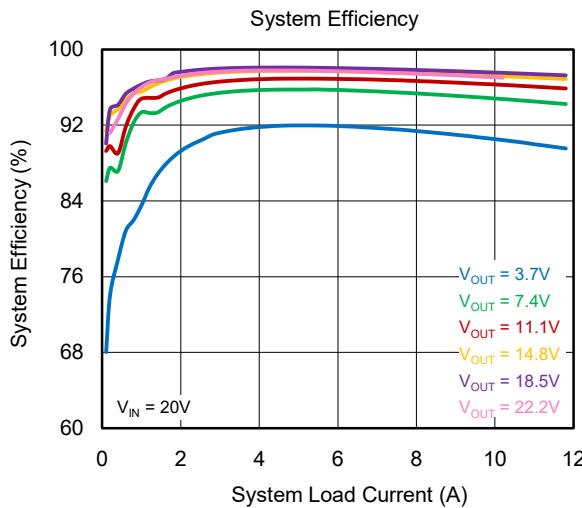

The SGM41580 supports pass through mode (PTM) that improves efficiency across the full load range. In this mode, input power is delivered directly to the system, reducing switching losses in the MOSFETs and minimizing inductor core losses for higher overall efficiency.

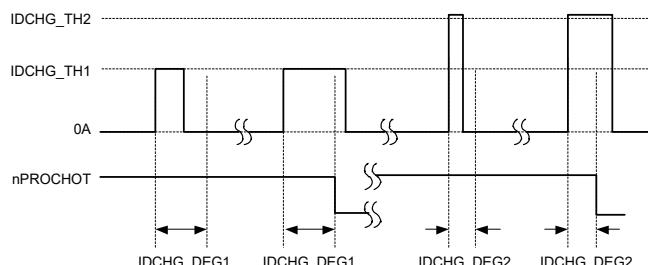

Adapter current, battery current and system power are monitored in SGM41580. When the system power is too high and exceeds available power from adapter and battery together, a flexibly programmed nPROCHOT pulse is asserted to inform CPU for throttle back.

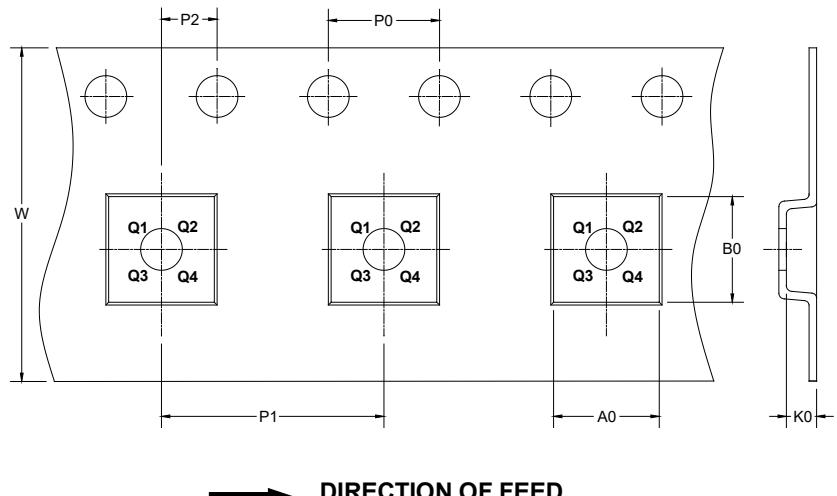

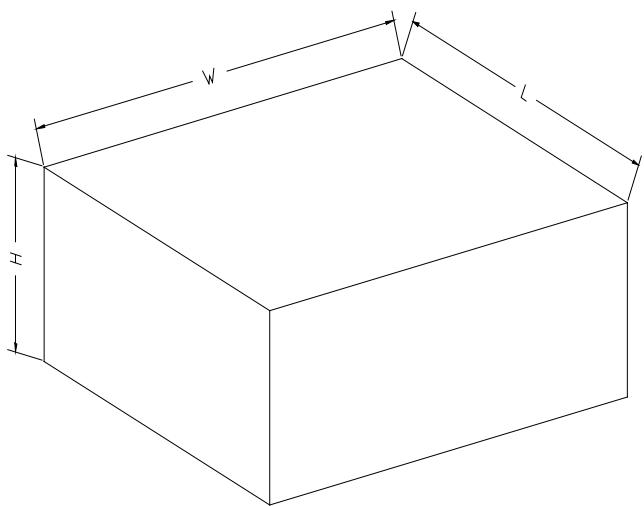

## PACKAGE/ORDERING INFORMATION

| MODEL    | PACKAGE DESCRIPTION | SPECIFIED TEMPERATURE RANGE | ORDERING NUMBER    | PACKAGE MARKING             | PACKING OPTION      |

|----------|---------------------|-----------------------------|--------------------|-----------------------------|---------------------|

| SGM41580 | TQFN-4x4-32AL       | -40°C to +125°C             | SGM41580XTSE32G/TR | SGM41580<br>XTSE32<br>XXXXX | Tape and Reel, 3000 |

## MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

**XXXXX**

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

## ABSOLUTE MAXIMUM RATINGS

Voltage Range (with Respect to GND)

|                                                                                                              |       |               |

|--------------------------------------------------------------------------------------------------------------|-------|---------------|

| ACN, ACP, VBUS                                                                                               | ..... | -0.3V to 32V  |

| ACN, ACP, VBUS (10μs)                                                                                        | ..... | -0.3V to 36V  |

| SRN, SRP, VSYS, nBATDRV                                                                                      | ..... | -0.3V to 32V  |

| SRN, SRP, VSYS, nBATDRV (25ns)                                                                               | ..... | -0.3V to 36V  |

| SW1, SW2                                                                                                     | ..... | -2V to 32V    |

| SW1, SW2 (25ns)                                                                                              | ..... | -4V to 36V    |

| BTST1, BTST2, HIDRV1, HIDRV2                                                                                 | ..... | -0.3V to 38V  |

| BTST1, BTST2, HIDRV1, HIDRV2 (25ns)                                                                          | ..... | -4V to 42V    |

| LODRV1, LODRV2 (25ns)                                                                                        | ..... | -4V to 7V     |

| SDA, SCL, REGN, CHRG_OK, OTG/VAP/FRS, ILIM_HIZ, VDDA, CELL_BATPRESZ, LODRV1, LODRV2, nPROCHOT, CMPIN, CMPOUT | ..... | -0.3V to 7V   |

| COMP1, COMP2                                                                                                 | ..... | -0.3V to 5.5V |

| IADPT, IBAT, PSYS                                                                                            | ..... | -0.3V to 3.6V |

Differential Voltage Range

|                                              |       |               |

|----------------------------------------------|-------|---------------|

| BTST1-SW1, BTST2-SW2, HIDRV1-SW1, HIDRV2-SW2 | ..... | -0.3V to 7V   |

| SRP-SRN, ACP-ACN                             | ..... | -0.5V to 0.5V |

Package Thermal Resistance

|                                      |       |          |

|--------------------------------------|-------|----------|

| TQFN-4x4-32AL, θ <sub>JA</sub>       | ..... | 28.5°C/W |

| TQFN-4x4-32AL, θ <sub>JB</sub>       | ..... | 8°C/W    |

| TQFN-4x4-32AL, θ <sub>JC (TOP)</sub> | ..... | 23.6°C/W |

| TQFN-4x4-32AL, θ <sub>JC (BOT)</sub> | ..... | 1.6°C/W  |

Junction Temperature.....+150°C

Storage Temperature Range.....-65°C to +150°C

Lead Temperature (Soldering, 10s).....+260°C

ESD Susceptibility <sup>(1)(2)</sup>

HBM.....±3000V

CDM.....±1000V

## NOTES:

1. For human body model (HBM), all pins comply with ANSI/ESDA/JEDEC JS-001 specifications.

2. For charged device model (CDM), all pins comply with ANSI/ESDA/JEDEC JS-002 specifications.

## RECOMMENDED OPERATING CONDITIONS

Voltage Range (with Respect to GND)

|                                                          |       |            |

|----------------------------------------------------------|-------|------------|

| ACN, ACP, VBUS                                           | ..... | 0V to 30V  |

| SRN, SRP, VSYS                                           | ..... | 0V to 27V  |

| SW1, SW2                                                 | ..... | -2V to 30V |

| BTST1, BTST2, HIDRV1, HIDRV2, nBATDRV                    | ..... | 0V to 36V  |

| SDA, SCL, CHRG_OK, COMP1, COMP2, CMPIN, CMPOUT, nPROCHOT | ..... | 0V to 5.3V |

| CELL_BATPRESZ, ILIM_HIZ, LODRV1, LODRV2, VDDA, REGN      | ..... | 0V to 6V   |

| IADPT, IBAT, PSYS                                        | ..... | 0V to 3.3V |

Differential Voltage Range

|                                              |       |               |

|----------------------------------------------|-------|---------------|

| BTST1-SW1, BTST2-SW2, HIDRV1-SW1, HIDRV2-SW2 | ..... | 0V to 6V      |

| SRP-SRN, ACP-ACN                             | ..... | -0.5V to 0.5V |

Operating Junction Temperature Range.....-40°C to +125°C

## OVERSTRESS CAUTION

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

## ESD SENSITIVITY CAUTION

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

## DISCLAIMER

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

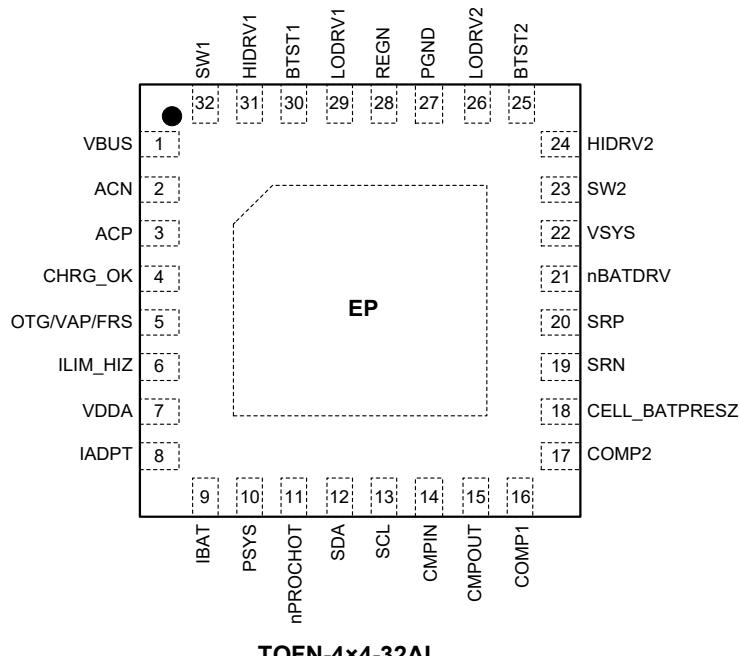

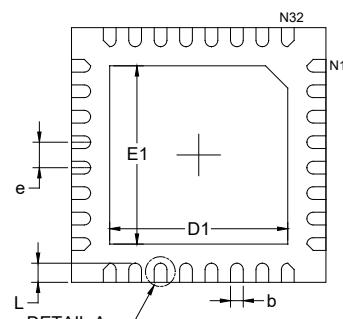

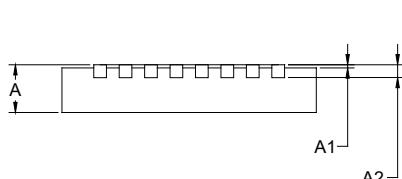

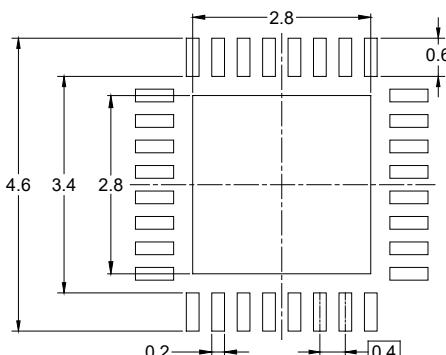

## PIN CONFIGURATION

(TOP VIEW)

TQFN-4x4-32AL

## PIN DESCRIPTION

| PIN | NAME        | TYPE <sup>(1)</sup> | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|-------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VBUS        | P                   | Charger Input. Place an RC low pass filter on this pin ( $R = 1\Omega$ and $C \geq 0.47\mu F$ ).                                                                                                                                                                                                                                                                                                                                                          |

| 2   | ACN         | P                   | Negative Terminal of the Input Current Sense Resistor. Place an RC low pass filter between this pin and the sense resistor.                                                                                                                                                                                                                                                                                                                               |

| 3   | ACP         | P                   | Positive Terminal of the Input Current Sense Resistor. Place an RC low pass filter between this pin and the sense resistor.                                                                                                                                                                                                                                                                                                                               |

| 4   | CHRG_OK     | O                   | Active High Open-Drain Good Power Source Status Output. Place a $10k\Omega$ resistor between this pin and pull-up rail. CHRG_OK goes high with no fault (SYS short latch off, SYSOVP, BATOC, BATOVP, ACOC, force latch off, and thermal shutdown) when VBUS voltage rises above $V_{VBUS\_CONVEN}$ or falls below $V_{ACOV}$ . CHRG_OK goes low when VBUS falls below $V_{VBUS\_CONVEN}$ or rises above $V_{ACOV}$ or when above fault occurs.            |

| 5   | OTG/VAP/FRS | I                   | OTG, VAP or FRS Modes Enable Input (Active High).<br>OTG mode enable: OTG_VAP_MODE bit = 1, EN_OTG bit = 1 and pull this pin to high.<br>VAP mode enable: OTG_VAP_MODE bit = 0, and pull this pin to high.<br>FRS mode enable: OTG_VAP_MODE bit = 1, EN_FRS bit = 1 and pull this pin to high in forward operation.                                                                                                                                       |

| 6   | ILIM_HIZ    | I                   | Input Current Limit Setting Input. Connect this pin to a resistor divider between supply and ground to set the target input current limit $I_{DPM}$ using the following equation:<br>$V_{ILIM\_HIZ} = 1V + 40 \times I_{DPM} \times R_{AC}$<br>The actual input current limit is the lower setting of ILIM_HIZ pin and IIN_HOST register. The device enters HIZ mode when $V_{ILIM\_HIZ} < 0.5V$ , and exits HIZ mode when $V_{ILIM\_HIZ} > 0.9V$ .       |

| 7   | VDDA        | P                   | Internal Reference Bias. Place a $10\Omega$ resistor from REGN to this pin, and place a $1\mu F$ ceramic capacitor from this pin to ground.                                                                                                                                                                                                                                                                                                               |

| 8   | IADPT       | O                   | Adapter Current Monitoring Output. $V_{IADPT} = 20$ or $40 \times (V_{ACP} - V_{ACN})$ and $20V/V$ or $40V/V$ can be selected in the IADPT_GAIN bit. Place a resistor from this pin to ground according to <b>Inductance Detection through IADPT Pin</b> section. The resistor is $137k\Omega$ when $L = 2.2\mu H$ . Connect a $100pF$ or less ceramic decoupling capacitor from this pin to ground. IADPT output voltage is clamped below 3.2V.          |

| 9   | IBAT        | O                   | Battery Current Monitoring Output. The charge current is monitored as $V_{IBAT} = 8$ or $16 \times (V_{SRP} - V_{SRN})$ , and the discharge current is monitored as $V_{IBAT} = 8$ or $16 \times (V_{SRN} - V_{SRP})$ . $8V/V$ or $16V/V$ can be selected in the IBAT_GAIN bit. Connect a $100pF$ or less ceramic decoupling capacitor from this pin to ground. IBAT pin can be left floating if not in use and its output voltage is clamped below 3.2V. |

## PIN DESCRIPTION (continued)

| PIN         | NAME          | TYPE <sup>(1)</sup> | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|---------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10          | PSYS          | O                   | System Power Monitoring Output (Current Mode). The output current of this pin is proportional to the total power from the adapter and the battery refers to <b>High-Accuracy Power Sense Amplifier (PSYS)</b> section. The gain can be selected by SMBus. Connect a resistor between this pin and ground to generate output voltage. PSYS pin can be left floating if not in use. And its output voltage is clamped below 3.2V.                                                                                      |

| 11          | nPROCHOT      | O                   | Active Low Open-Drain Processor Hot Indicator Output. The adapter input current, battery discharge current and system voltage are monitored, and a pulse is asserted if any event in the nPROCHOT profile is triggered. The minimum pulse width is adjustable in PROCHOT_WIDTH[1:0] bits.                                                                                                                                                                                                                            |

| 12          | SDA           | I/O                 | SMBus Data Signal. Use a 10kΩ pull-up to the logic high rail.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 13          | SCL           | I                   | SMBus Clock Signal. Use a 10kΩ pull-up to the logic high rail.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

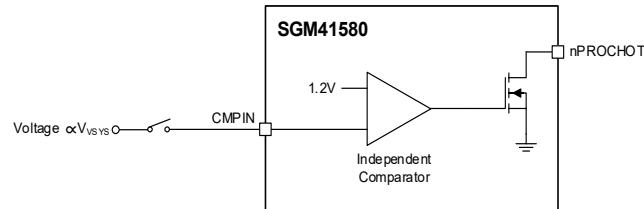

| 14          | CMPIN         | I                   | Independent Comparator Input. The voltage sensed on this pin is compared with internal reference by the independent comparator, and the output of comparator is on CMPOUT pin. The internal reference, output polarity and deglitch time are all selectable in the SMBus host. When CMP_POL bit = 1, the internal hysteresis is determined by the resistor between CMPIN and CMPOUT. When CMP_POL bit = 0, the internal hysteresis is 100mV. Connect this pin to ground if the independent comparator is not in use. |

| 15          | CMPOUT        | O                   | Open-Drain Independent Comparator Output. Place a resistor between this pin and pull-up supply rail.                                                                                                                                                                                                                                                                                                                                                                                                                 |

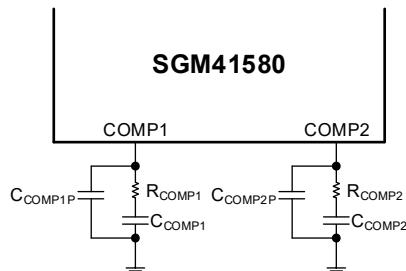

| 16          | COMP1         | I                   | Buck-Boost Compensation Pin 1. Refer to Table 4 for the compensation network.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 17          | COMP2         | I                   | Buck-Boost Compensation Pin 2. Refer to Table 4 for the compensation network.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 18          | CELL_BATPRESZ | I                   | Battery Cell Selection Input. This pin is biased from VDDA, and sets the SYSOVP thresholds (6V for 1-cell, 11.9V for 2-cell, 19.8V for 3-cell/4-cell, 24.6V for 5-cell and 28.5V for 6-cell). When the voltage on this pin is pulled below V <sub>CELL_BATPRESZ_FALL</sub> , it indicates battery removal. The device exits LEARN mode, the charge current goes back to 0. And the MaxChargeVoltage/MinSystemVoltage register goes to default.                                                                       |

| 19          | SRN           | P                   | Negative Input of the Charge Current Sense Resistor. This pin also senses the battery voltage. Place an optional 0.1μF ceramic capacitor from this pin to GND for common-mode noise filtering. Place a 0.1μF ceramic capacitor from SRP to SRN for differential mode noise filtering.                                                                                                                                                                                                                                |

| 20          | SRP           | P                   | Positive Input of the Charge Current Sense Resistor. Place an optional 0.1μF ceramic capacitor from this pin to GND for common-mode noise filtering. Place a 0.1μF ceramic capacitor from SRP to SRN for differential mode noise filtering.                                                                                                                                                                                                                                                                          |

| 21          | nBATDRV       | O                   | P-Channel BATFET Gate Driver Output. It is shorted to VSYS for turning off the BATFET and goes 11.7V below VSYS for fully on.                                                                                                                                                                                                                                                                                                                                                                                        |

| 22          | VSYS          | P                   | System Voltage Sensing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 23          | SW2           | P                   | Boost Mode Switching Node. Connect it to the source of the Boost mode high-side N-channel MOSFET (Q4).                                                                                                                                                                                                                                                                                                                                                                                                               |

| 24          | HIDRV2        | O                   | Boost Mode High-side N-Channel MOSFET (Q4) Driver. Connect it to the gate of Q4.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 25          | BTST2         | P                   | Boost Mode High-side N-Channel MOSFET (Q4) Driver Power Supply. Place a 47nF capacitor between SW2 and BTST2. It is internally connected to the boost-strap diode cathode.                                                                                                                                                                                                                                                                                                                                           |

| 26          | LODRV2        | O                   | Boost Mode Low-side N-Channel MOSFET (Q3) Driver. Connect it to the gate of Q3.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 27          | PGND          | GND                 | Power Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 28          | REGN          | P                   | 6V LDO Output. It is supplied from VBUS or VSYS and the LDO is active when VBUS voltage is above V <sub>VBUS_CONVEN</sub> . A 2.2μF or 3.3μF ceramic capacitor is recommended between this pin and PGND.                                                                                                                                                                                                                                                                                                             |

| 29          | LODRV1        | O                   | Buck Mode Low-side N-Channel MOSFET (Q2) Driver. Connect it to the gate of Q2.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 30          | BTST1         | P                   | Buck Mode High-side N-Channel MOSFET (Q1) Driver Power Supply. Place a 47nF capacitor between SW1 and BTST1. It is internally connected to the boost-strap diode cathode.                                                                                                                                                                                                                                                                                                                                            |

| 31          | HIDRV1        | O                   | Buck Mode High-side N-Channel MOSFET (Q1) Driver. Connect it to the gate of Q1.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 32          | SW1           | P                   | Buck Mode Switching Node. Connect it to the source of the Buck mode high-side N-channel MOSFET (Q1).                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Exposed Pad | EP            | -                   | Thermal Pad. It is the thermal pad to conduct heat from the device. Tie it externally to the PCB power ground plane. Thermal vias under the pad are needed to conduct the heat to the PCB power ground planes.                                                                                                                                                                                                                                                                                                       |

NOTE: 1. I = Input, O = Output, I/O = Input or Output, P = Power.

## ELECTRICAL CHARACTERISTICS

(T<sub>J</sub> = -40°C to +125°C, typical values are measured at T<sub>J</sub> = +25°C, unless otherwise noted.)

| PARAMETER                                  | SYMBOL                      | CONDITIONS                                     | MIN                                          | TYP | MAX                      | UNITS |  |  |

|--------------------------------------------|-----------------------------|------------------------------------------------|----------------------------------------------|-----|--------------------------|-------|--|--|

| Input Voltage Operating Range              | V <sub>INPUT_OP</sub>       | V <sub>VSYS</sub> ≥ 5V                         | 3.5                                          |     | 30                       | V     |  |  |

|                                            |                             | V <sub>VSYS</sub> < 5V, T <sub>J</sub> = +25°C | 4.6                                          |     | 30                       |       |  |  |

| <b>Regulation Accuracy</b>                 |                             |                                                |                                              |     |                          |       |  |  |

| <b>Max System Voltage Regulation</b>       |                             |                                                |                                              |     |                          |       |  |  |

| System Voltage Regulation                  | V <sub>SYSMAX RNG</sub>     | Charge disabled, measured on V <sub>VSYS</sub> | 1.024                                        |     | 27.6                     | V     |  |  |

| System Voltage Regulation Accuracy         | V <sub>SYSMAX ACC</sub>     | Charge disabled                                | MaxChargeVoltage register = 0x6270 (25.20V)  |     | V <sub>SRN</sub> + 200mV | V     |  |  |

|                                            |                             |                                                | -1                                           |     | 1                        | %     |  |  |

|                                            |                             |                                                | MaxChargeVoltage register = 0x5208 (21.00V)  |     | V <sub>SRN</sub> + 200mV | V     |  |  |

|                                            |                             |                                                | -1                                           |     | 1                        | %     |  |  |

|                                            |                             |                                                | MaxChargeVoltage register = 0x41A0 (16.800V) |     | V <sub>SRN</sub> + 200mV | V     |  |  |

|                                            |                             |                                                | -1.5                                         |     | 1.5                      | %     |  |  |

|                                            |                             |                                                | MaxChargeVoltage register = 0x3138 (12.600V) |     | V <sub>SRN</sub> + 200mV | V     |  |  |

| Minimum System Voltage Regulation          | V <sub>SYSMIN RNG</sub>     | Measured on V <sub>VSYS</sub>                  | MaxChargeVoltage register = 0x20D0 (8.400V)  |     | V <sub>SRN</sub> + 200mV | V     |  |  |

|                                            |                             |                                                | -2                                           |     | 2                        | %     |  |  |

|                                            |                             |                                                | MaxChargeVoltage register = 0x1068 (4.200V)  |     | V <sub>SRN</sub> + 200mV | V     |  |  |

|                                            |                             |                                                | -3                                           |     | 3                        | %     |  |  |

|                                            |                             |                                                | MinSystemVoltage register = 0xB900           |     | 18.5                     | V     |  |  |

|                                            |                             |                                                | -2                                           |     | 2                        | %     |  |  |

|                                            |                             |                                                | MinSystemVoltage register = 0x9A00           |     | 15.4                     | V     |  |  |

| Minimum System Voltage Regulation Accuracy | V <sub>SYSMIN REG ACC</sub> | VBAT below MinSystemVoltage register setting   | MinSystemVoltage register = 0x7B00           |     | 2                        | %     |  |  |

|                                            |                             |                                                | -2                                           |     | 12.3                     | V     |  |  |

|                                            |                             |                                                | MinSystemVoltage register = 0x5C00           |     | 9.2                      | V     |  |  |

|                                            |                             |                                                | -2                                           |     | 2                        | %     |  |  |

|                                            |                             |                                                | MinSystemVoltage register = 0x4200           |     | 6.6                      | V     |  |  |

|                                            |                             |                                                | -2                                           |     | 2                        | %     |  |  |

|                                            |                             |                                                | MinSystemVoltage register = 0x2400           |     | 3.6                      | V     |  |  |

|                                            |                             |                                                | -1                                           |     | 3                        | %     |  |  |

## ELECTRICAL CHARACTERISTICS (continued)

(T<sub>J</sub> = -40°C to +125°C, typical values are measured at T<sub>J</sub> = +25°C, unless otherwise noted.)

| PARAMETER                                                                        | SYMBOL                       | CONDITIONS                                                  | MIN                                | TYP  | MAX  | UNITS |

|----------------------------------------------------------------------------------|------------------------------|-------------------------------------------------------------|------------------------------------|------|------|-------|

| <b>Charge Voltage Regulation</b>                                                 |                              |                                                             |                                    |      |      |       |

| Battery Voltage Regulation                                                       | V <sub>BAT_RNG</sub>         |                                                             | 1.024                              |      | 27.6 | V     |

| Battery Voltage Regulation<br>Initial Accuracy                                   | V <sub>BAT_REG_ACC</sub>     | Charge enabled<br>(0°C to +85°C)                            | MaxChargeVoltage register = 0x6270 | 25.2 |      | V     |

|                                                                                  |                              |                                                             | -0.5                               | 0.5  |      | %     |

|                                                                                  |                              |                                                             | MaxChargeVoltage register = 0x5208 | 21   |      | V     |

|                                                                                  |                              |                                                             | -0.3                               | 0.6  |      | %     |

|                                                                                  |                              |                                                             | MaxChargeVoltage register = 0x41A0 | 16.8 |      | V     |

|                                                                                  |                              |                                                             | -0.4                               | 0.4  |      | %     |

|                                                                                  |                              |                                                             | MaxChargeVoltage register = 0x3138 | 12.6 |      | V     |

| Charge Current Regulation in Fast Charge                                         | V <sub>IREG_CHG_RNG</sub>    | V <sub>IREG_CHG</sub> = V <sub>SRP</sub> - V <sub>SRN</sub> | -0.5                               | 0.4  |      | %     |

|                                                                                  |                              |                                                             | MaxChargeVoltage register = 0x20D0 | 8.4  |      | V     |

|                                                                                  |                              |                                                             | -0.5                               | 0.5  |      | %     |

|                                                                                  |                              |                                                             | MaxChargeVoltage register = 0x1068 | 4.2  |      | V     |

|                                                                                  |                              |                                                             | -1                                 | 1    |      | %     |

|                                                                                  |                              |                                                             |                                    |      |      |       |

|                                                                                  |                              |                                                             |                                    |      |      |       |

| <b>Charge Current Regulation in LDO Mode</b>                                     |                              |                                                             |                                    |      |      |       |

| Pre-Charge Current Clamp                                                         | I <sub>CLAMP</sub>           | 2-cell to 6-cell                                            |                                    | 384  |      | mA    |

|                                                                                  |                              | 1-cell, V <sub>SRN</sub> < 3V                               |                                    | 384  |      | mA    |

|                                                                                  |                              | 1-cell, 3V < V <sub>SRN</sub> < V <sub>SYSMIN</sub>         |                                    | 2    |      | A     |

| Pre-Charge Current<br>Regulation Accuracy with<br>5mΩ SRP/SRN Series<br>Resistor | I <sub>PRECHRG_REG_ACC</sub> | VBAT below<br>MinSystemVoltage<br>register setting          | ChargeCurrent register = 0x00C0    | 384  |      | mA    |

|                                                                                  |                              |                                                             | 2-cell to 6-cell                   | -15  | 15   | %     |

|                                                                                  |                              |                                                             | ChargeCurrent register = 0x0080    | 256  |      | mA    |

|                                                                                  |                              |                                                             | 2-cell to 6-cell                   | -15  | 15   | %     |

| SRP, SRN Leakage Current<br>Mismatch                                             | I <sub>LEAK_SR_P_SR_N</sub>  |                                                             |                                    | -5   | 5    | µA    |

| <b>Input Current Regulation</b>                                                  |                              |                                                             |                                    |      |      |       |

| Input Current Regulation<br>Differential Voltage Range                           | V <sub>IREG_DPM_RNG</sub>    | V <sub>IREG_DPM</sub> = V <sub>ACP</sub> - V <sub>ACN</sub> | 0.5                                |      | 64   | mV    |

| Input Current Regulation Initial<br>Accuracy with 5mΩ ACP/ACN<br>Series Resistor | I <sub>DPM_REG_ACC</sub>     | IIN_HOST register = 0x4E00                                  | 7600                               | 7800 | 8000 | mA    |

|                                                                                  |                              | IIN_HOST register = 0x3A00                                  | 5600                               | 5800 | 6000 |       |

|                                                                                  |                              | IIN_HOST register = 0x1C00                                  | 2600                               | 2800 | 3000 |       |

|                                                                                  |                              | IIN_HOST register = 0x0800                                  | 600                                | 800  | 1000 |       |

SGM41580

# SMBus NVDC Buck-Boost Charge Controller for 1- to 6-Cell Battery

## ELECTRICAL CHARACTERISTICS (continued)

( $T_J = -40^\circ\text{C}$  to  $+125^\circ\text{C}$ , typical values are measured at  $T_J = +25^\circ\text{C}$ , unless otherwise noted.)

| PARAMETER                                                                                     | SYMBOL                            | CONDITIONS                                                                              | MIN                                  | TYP   | MAX    | UNITS         |  |  |

|-----------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------|-------|--------|---------------|--|--|

| ACP/ACN Leakage Current Mismatch                                                              | $I_{\text{LEAK\_ACP\_ACN}}$       |                                                                                         | -10                                  |       | 5      | $\mu\text{A}$ |  |  |

| Voltage Range for Input Current Regulation (ILIM_HIZ Pin)                                     | $V_{\text{IREG\_DPM\_RNG\_ILIM}}$ |                                                                                         | 1.15                                 |       | 4      | V             |  |  |

| Input Current Regulation Accuracy on ILIM_HIZ Pin with 5m $\Omega$ ACP/ACN Series Resistor    | $I_{\text{DPM\_REG\_ACC\_ILIM}}$  | $V_{\text{ILIM\_HIZ}} = 1\text{V}$<br>$+ 40 \times I_{\text{DPM}} \times R_{\text{AC}}$ | $V_{\text{ILIM\_HIZ}} = 2.6\text{V}$ | 7600  | 8000   | 8400          |  |  |

|                                                                                               |                                   |                                                                                         | $V_{\text{ILIM\_HIZ}} = 2.2\text{V}$ | 5600  | 6000   | 6400          |  |  |

|                                                                                               |                                   |                                                                                         | $V_{\text{ILIM\_HIZ}} = 1.6\text{V}$ | 2600  | 3000   | 3400          |  |  |

|                                                                                               |                                   |                                                                                         | $V_{\text{ILIM\_HIZ}} = 1.2\text{V}$ | 600   | 1000   | 1400          |  |  |

| ILIM_HIZ Pin Leakage Current                                                                  | $I_{\text{LEAK\_ILIM}}$           |                                                                                         | -1                                   |       | 1      | $\mu\text{A}$ |  |  |

| <b>Input Voltage Regulation</b>                                                               |                                   |                                                                                         |                                      |       |        |               |  |  |

| Input Voltage Regulation Range                                                                | $V_{\text{IREG\_DPM\_RNG}}$       | Voltage on VBUS                                                                         | 3.2                                  |       | 27.776 | V             |  |  |

| Input Voltage Regulation Accuracy                                                             | $V_{\text{DPM\_REG\_ACC}}$        | InputVoltage register = 0x3C80                                                          |                                      | 18688 |        | mV            |  |  |

|                                                                                               |                                   |                                                                                         | -3                                   |       | 1      | %             |  |  |

|                                                                                               |                                   | InputVoltage register = 0x1E00                                                          |                                      | 10880 |        | mV            |  |  |

|                                                                                               |                                   |                                                                                         | -3                                   |       | 1      | %             |  |  |

|                                                                                               |                                   |                                                                                         |                                      | 4480  |        | mV            |  |  |

|                                                                                               |                                   |                                                                                         | -3                                   |       | 2      | %             |  |  |

| <b>OTG Current Regulation</b>                                                                 |                                   |                                                                                         |                                      |       |        |               |  |  |

| OTG Output Current Regulation Differential Voltage Range                                      | $V_{\text{IOTG\_REG\_RNG}}$       | $V_{\text{IOTG\_REG}} = V_{\text{ACP}} - V_{\text{ACN}}$                                | 0                                    |       | 81.28  | mV            |  |  |

| OTG Output Current Regulation Accuracy with 100mA LSB and 5m $\Omega$ ACP/ACN Series Resistor | $I_{\text{OTG\_ACC}}$             | OTGCurrent register = 0x3C00                                                            | 5600                                 | 6000  | 6400   | mA            |  |  |

|                                                                                               |                                   | OTGCurrent register = 0x1E00                                                            | 2600                                 | 3000  | 3400   |               |  |  |

|                                                                                               |                                   | OTGCurrent register = 0x0A00                                                            | 600                                  | 1000  | 1400   |               |  |  |

| <b>OTG Voltage Regulation</b>                                                                 |                                   |                                                                                         |                                      |       |        |               |  |  |

| OTG Voltage Regulation Range                                                                  | $V_{\text{OTG\_REG\_RNG}}$        | Voltage on VBUS                                                                         | 3                                    |       | 28.16  | V             |  |  |

| OTG Voltage Regulation Accuracy                                                               | $V_{\text{OTG\_REG\_ACC}}$        | OTGVoltage register = 0x36B0                                                            |                                      | 28    |        | V             |  |  |

|                                                                                               |                                   |                                                                                         | -2.5                                 |       | 0.5    | %             |  |  |

|                                                                                               |                                   | OTGVoltage register = 0x1770                                                            |                                      | 12    |        | V             |  |  |

|                                                                                               |                                   |                                                                                         | -2                                   |       | 1      | %             |  |  |

|                                                                                               |                                   |                                                                                         |                                      | 5     |        | V             |  |  |

|                                                                                               |                                   |                                                                                         | -2                                   |       | 2      | %             |  |  |

| <b>Reference and Buffer</b>                                                                   |                                   |                                                                                         |                                      |       |        |               |  |  |

| <b>REGN Regulator</b>                                                                         |                                   |                                                                                         |                                      |       |        |               |  |  |

| REGN Regulator Voltage (0mA to 60mA)                                                          | $V_{\text{REGN\_REG}}$            | $V_{\text{VBUS}} = 10\text{V}$                                                          | 5.7                                  | 6.0   | 6.3    | V             |  |  |

| REGN Voltage in Drop Out Mode                                                                 | $V_{\text{DROPOUT}}$              | $V_{\text{VBUS}} = 5\text{V}$ , $I_{\text{LOAD}} = 20\text{mA}$                         | 4.5                                  | 4.75  | 5      | V             |  |  |

| REGN Current Limit when Converter is Enabled                                                  | $I_{\text{REGN\_LIM\_Charging}}$  | $V_{\text{VBUS}} = 10\text{V}$ , force $V_{\text{REGN}} = 4\text{V}$                    | 40                                   | 70    |        | mA            |  |  |

| REGN Output Capacitor Required for Stability                                                  | $C_{\text{REGN}}$                 | $I_{\text{LOAD}} = 100\mu\text{A}$ to $50\text{mA}$                                     | 2.2                                  |       |        | $\mu\text{F}$ |  |  |

| VDDA Input Capacitor Required for Stability                                                   | $C_{\text{VDDA}}$                 | $I_{\text{LOAD}} = 100\mu\text{A}$ to $50\text{mA}$                                     | 1                                    |       |        | $\mu\text{F}$ |  |  |

## ELECTRICAL CHARACTERISTICS (continued)

(T<sub>J</sub> = -40°C to +125°C, typical values are measured at T<sub>J</sub> = +25°C, unless otherwise noted.)

| PARAMETER                                                                                                                                                                                                                                               | SYMBOL                             | CONDITIONS                                                                                                                           | MIN                               | TYP  | MAX  | UNITS |   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------|------|-------|---|

| <b>Quiescent Current</b>                                                                                                                                                                                                                                |                                    |                                                                                                                                      |                                   |      |      |       |   |

| System Powered by Battery, BATFET on, I <sub>SRN</sub> + I <sub>SRP</sub> + I <sub>SW2</sub> + I <sub>BTST2</sub> + I <sub>SW1</sub> + I <sub>BTST1</sub> + I <sub>ACP</sub> + I <sub>ACN</sub> + I <sub>VBUS</sub> + I <sub>VSYS</sub>                 | I <sub>BAT_BATFET_ON</sub>         | V <sub>BAT</sub> = 18V, EN_LWPWR = 1, EN_PROCHOT_LPWR = 0, in low power mode, PSYS disabled                                          |                                   | 13   | 18   | μA    |   |

|                                                                                                                                                                                                                                                         |                                    | V <sub>BAT</sub> = 18V, EN_LWPWR = 1, EN_PROCHOT_LPWR = 1, PSYS_CONFIG[1:0] = 11, REGN off, PSYS disabled, enable low power nPROCHOT |                                   | 25   | 35   |       |   |

|                                                                                                                                                                                                                                                         |                                    | V <sub>BAT</sub> = 18V, EN_LWPWR = 0, PSYS_CONFIG[1:0] = 11, REGN on, PSYS disabled, in performance mode                             |                                   | 1300 | 1800 |       |   |

|                                                                                                                                                                                                                                                         |                                    | V <sub>BAT</sub> = 18V, EN_LWPWR = 0, PSYS_CONFIG[1:0] = 00, REGN on, PSYS enabled                                                   |                                   | 1400 | 1900 |       |   |

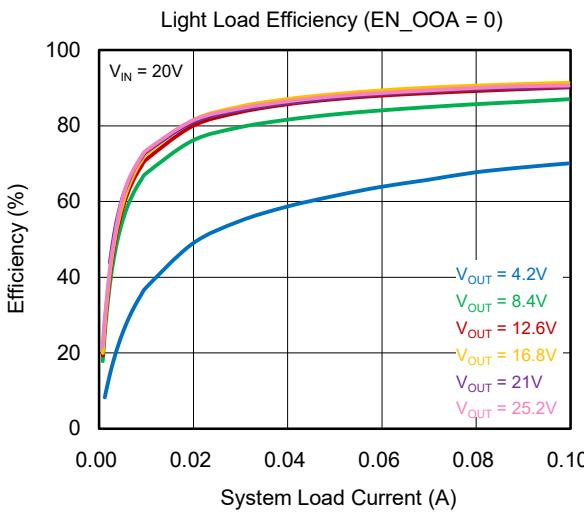

| Input Current during PSM in Buck Mode, No Load, I <sub>VBUS</sub> + I <sub>ACP</sub> + I <sub>ACN</sub> + I <sub>VSYS</sub> + I <sub>SRP</sub> + I <sub>SRN</sub> + I <sub>SW1</sub> + I <sub>BTST1</sub> + I <sub>SW2</sub> + I <sub>BTST2</sub>       | I <sub>AC_SW_LIGHT_Buck</sub>      | V <sub>IN</sub> = 20V, V <sub>BAT</sub> = 12.6V, 3-cell, EN_OOA = 0, MOSFET Q <sub>G</sub> = 8nC                                     |                                   | 2.2  |      | mA    |   |

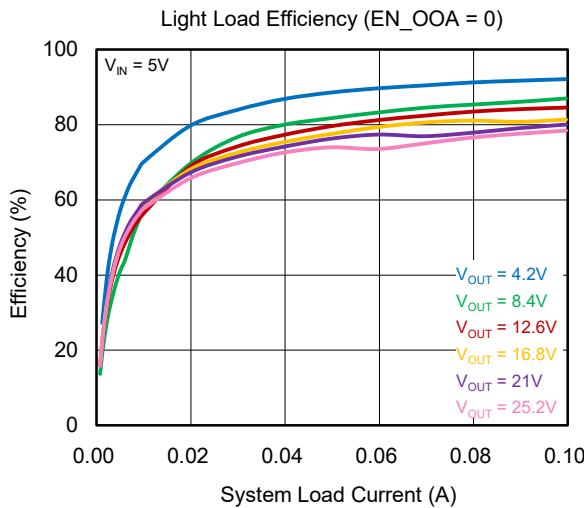

| Input Current during PSM in Boost Mode, No Load, I <sub>VBUS</sub> + I <sub>ACP</sub> + I <sub>ACN</sub> + I <sub>VSYS</sub> + I <sub>SRP</sub> + I <sub>SRN</sub> + I <sub>SW1</sub> + I <sub>BTST1</sub> + I <sub>SW2</sub> + I <sub>BTST2</sub>      | I <sub>AC_SW_LIGHT_Boost</sub>     | V <sub>IN</sub> = 5V, V <sub>BAT</sub> = 8.4V, 2-cell, EN_OOA = 0, MOSFET Q <sub>G</sub> = 8nC                                       |                                   | 6.5  |      | mA    |   |

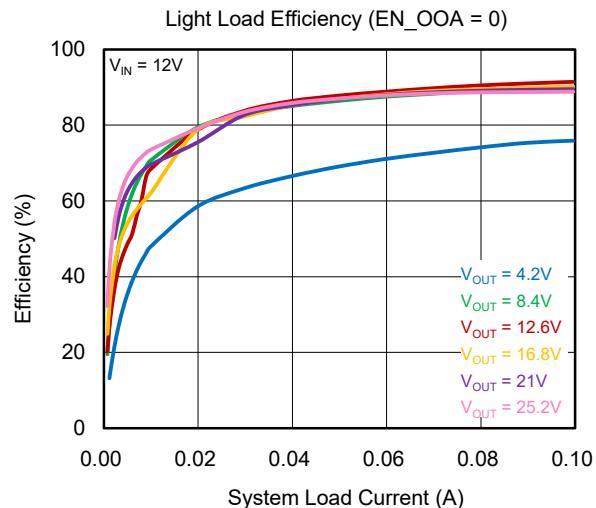

| Input Current during PSM in Buck-Boost Mode, No Load, I <sub>VBUS</sub> + I <sub>ACP</sub> + I <sub>ACN</sub> + I <sub>VSYS</sub> + I <sub>SRP</sub> + I <sub>SRN</sub> + I <sub>SW1</sub> + I <sub>BTST1</sub> + I <sub>SW2</sub> + I <sub>BTST2</sub> | I <sub>AC_SW_LIGHT_BuckBoost</sub> | V <sub>IN</sub> = 12V, V <sub>BAT</sub> = 12V, EN_OOA = 0, MOSFET Q <sub>G</sub> = 8nC                                               |                                   | 3.2  |      | mA    |   |

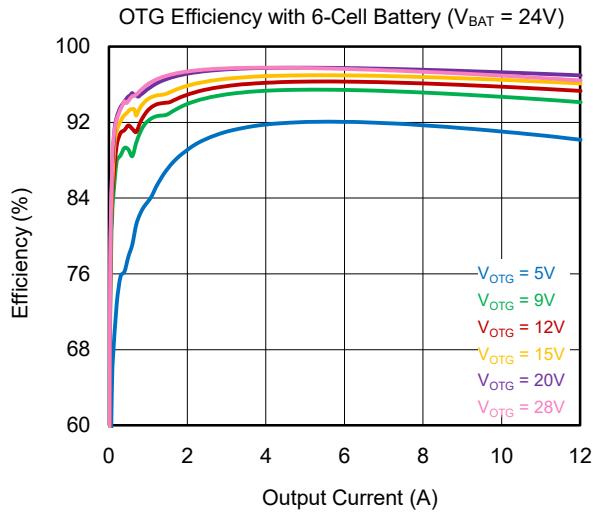

| Quiescent Current during PSM in OTG Mode, I <sub>VBUS</sub> + I <sub>ACP</sub> + I <sub>ACN</sub> + I <sub>VSYS</sub> + I <sub>SRP</sub> + I <sub>SRN</sub> + I <sub>SW1</sub> + I <sub>BTST1</sub> + I <sub>SW2</sub> + I <sub>BTST2</sub>             | I <sub>OTG_STANDBY</sub>           | V <sub>BAT</sub> = 8.4V, EN_OOA = 0, 800kHz switching frequency, MOSFET Q <sub>G</sub> = 8nC                                         | V <sub>VBUS</sub> = 5V            | 3.5  |      | mA    |   |

|                                                                                                                                                                                                                                                         |                                    |                                                                                                                                      | V <sub>VBUS</sub> = 12V           | 4    |      |       |   |

|                                                                                                                                                                                                                                                         |                                    |                                                                                                                                      | V <sub>VBUS</sub> = 20V           | 4.5  |      |       |   |

| Input Common Mode Range                                                                                                                                                                                                                                 | V <sub>ACP/N_OP</sub>              | Voltage on ACP/ACN                                                                                                                   |                                   | 3.8  | 30   | V     |   |

| IADPT Output Clamp Voltage                                                                                                                                                                                                                              | V <sub>IADPT_CLAMP</sub>           |                                                                                                                                      |                                   | 3.05 | 3.2  | 3.3   | V |

| IADPT Output Current                                                                                                                                                                                                                                    | I <sub>IADPT</sub>                 |                                                                                                                                      |                                   |      | 1    | mA    |   |

| Input Current Sensing Gain                                                                                                                                                                                                                              | A <sub>IADPT</sub>                 | V <sub>IADPT</sub> /V <sub>(ACP-ACN)</sub>                                                                                           | IADPT_GAIN = 0                    | 20   |      | V/V   |   |

|                                                                                                                                                                                                                                                         |                                    |                                                                                                                                      | IADPT_GAIN = 1                    | 40   |      |       |   |

| Input Current Monitor Initial Accuracy                                                                                                                                                                                                                  | V <sub>IADPT_ACC</sub>             | IADPT_GAIN = 1 (0°C to +85°C)                                                                                                        | V <sub>(ACP-ACN)</sub> = 40.96mV, | -2   | 2.5  | %     |   |

|                                                                                                                                                                                                                                                         |                                    |                                                                                                                                      | V <sub>(ACP-ACN)</sub> = 20.48mV, | -2.5 | 4    |       |   |

|                                                                                                                                                                                                                                                         |                                    |                                                                                                                                      | V <sub>(ACP-ACN)</sub> = 10.24mV, | -4.5 | 6.5  |       |   |

|                                                                                                                                                                                                                                                         |                                    |                                                                                                                                      | V <sub>(ACP-ACN)</sub> = 5.12mV   | -8   | 12   |       |   |

| Maximum Capacitance on IADPT Pin                                                                                                                                                                                                                        | C <sub>IADPT_MAX</sub>             |                                                                                                                                      |                                   |      | 100  | pF    |   |

| Battery Common Mode Range                                                                                                                                                                                                                               | V <sub>SRP/N_OP</sub>              | Voltage on SRP/SRN                                                                                                                   |                                   | 2.5  | 27.6 | V     |   |

| IBAT Output Clamp Voltage                                                                                                                                                                                                                               | V <sub>IBAT_CLAMP</sub>            |                                                                                                                                      |                                   | 3.05 | 3.2  | 3.3   | V |

| IBAT Output Current                                                                                                                                                                                                                                     | I <sub>IBAT</sub>                  |                                                                                                                                      |                                   |      | 1    | mA    |   |

| Charge and Discharge Current Sensing Gain on IBAT Pin                                                                                                                                                                                                   | A <sub>IBAT</sub>                  | V <sub>IBAT</sub> /V <sub>(SRN-SRN)</sub>                                                                                            | IBAT_GAIN = 0                     | 8    |      | V/V   |   |

|                                                                                                                                                                                                                                                         |                                    |                                                                                                                                      | IBAT_GAIN = 1                     | 16   |      |       |   |

| Charge Current Monitor Initial Accuracy on IBAT Pin                                                                                                                                                                                                     | V <sub>IBAT_CHG_ACC</sub>          | IBAT_GAIN = 1 (0°C to +85°C)                                                                                                         | V <sub>(SRP-SRN)</sub> = 40.96mV  | -2   | 2.5  | %     |   |

|                                                                                                                                                                                                                                                         |                                    |                                                                                                                                      | V <sub>(SRP-SRN)</sub> = 20.48mV  | -2.5 | 4    |       |   |

|                                                                                                                                                                                                                                                         |                                    |                                                                                                                                      | V <sub>(SRP-SRN)</sub> = 10.24mV  | -4.5 | 6.5  |       |   |

|                                                                                                                                                                                                                                                         |                                    |                                                                                                                                      | V <sub>(SRP-SRN)</sub> = 5.12mV   | -8   | 12   |       |   |

| Maximum Capacitance on IBAT Pin                                                                                                                                                                                                                         | C <sub>IBAT_MAX</sub>              |                                                                                                                                      |                                   |      | 100  | pF    |   |

## ELECTRICAL CHARACTERISTICS (continued)

(T<sub>J</sub> = -40°C to +125°C, typical values are measured at T<sub>J</sub> = +25°C, unless otherwise noted.)

| PARAMETER                                         | SYMBOL                        | CONDITIONS                                                                                  | MIN                      | TYP  | MAX  | UNITS |   |

|---------------------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------|--------------------------|------|------|-------|---|

| <b>System Power Sense Amplifier</b>               |                               |                                                                                             |                          |      |      |       |   |

| PSYS Output Voltage Range                         | V <sub>PSYS</sub>             |                                                                                             | 0                        |      | 3.3  | V     |   |

| PSYS Output Current                               | I <sub>PSYS</sub>             |                                                                                             | 0                        |      | 160  | µA    |   |

| PSYS System Gain                                  | A <sub>PSYS</sub>             | V <sub>PSYS</sub> /(P <sub>IN</sub> + P <sub>BAT</sub> ), PSYS_RATIO = 1                    |                          | 1    |      | µA/W  |   |

| PSYS Gain Accuracy                                | V <sub>PSYS_ACC</sub>         | Adapter only with system power = 19.5V/45W, PSYS_RATIO = 1, T <sub>J</sub> = -40°C to +85°C | -3                       |      | 3    | %     |   |

|                                                   |                               | Battery-only with system power = 11V/44W, PSYS_RATIO = 1, T <sub>J</sub> = -40°C to +85°C   | -3                       |      | 3    |       |   |

| PSYS Clamp Voltage                                | V <sub>PSYS_CLAMP</sub>       |                                                                                             | 2.5                      | 3.2  | 3.9  | V     |   |

| <b>Comparator</b>                                 |                               |                                                                                             |                          |      |      |       |   |

| <b>VSYS Under-Voltage Lockout Comparator</b>      |                               |                                                                                             |                          |      |      |       |   |

| VSYS Under-Voltage Rising Threshold               | V <sub>VSYS_UVLOZ</sub>       | VSYS rising                                                                                 | 2.3                      | 2.5  | 2.65 | V     |   |

| VBUS Under-Voltage Falling Threshold              | V <sub>VSYS_UVLO</sub>        | VSYS falling, VSYS_UVP[2:0] = 000                                                           | 2.2                      | 2.4  | 2.55 | V     |   |

| VBUS Under-Voltage Hysteresis                     | V <sub>VSYS_UVLO_HYST</sub>   |                                                                                             |                          | 100  |      | mV    |   |

| <b>VBUS Under-Voltage Lockout Comparator</b>      |                               |                                                                                             |                          |      |      |       |   |

| VBUS Under-Voltage Rising Threshold               | V <sub>VBUS_UVLOZ</sub>       | VBUS rising                                                                                 | 2.15                     | 2.4  | 2.65 | V     |   |

| VBUS Under-Voltage Falling Threshold              | V <sub>VBUS_UVLO</sub>        | VBUS falling                                                                                | 2                        | 2.25 | 2.5  | V     |   |

| VBUS Under-Voltage Hysteresis                     | V <sub>VBUS_UVLO_HYST</sub>   |                                                                                             |                          | 150  |      | mV    |   |

| VBUS Converter Enable Rising Threshold            | V <sub>VBUS_CONVEN</sub>      | VBUS rising                                                                                 | 3.1                      | 3.5  | 3.8  | V     |   |

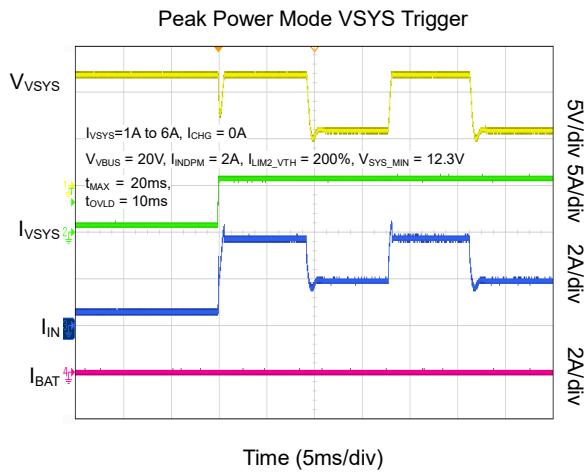

| VBUS Converter Enable Falling Threshold           | V <sub>VBUS_CONVENZ</sub>     | VBUS falling                                                                                | 2.8                      | 3.2  | 3.5  | V     |   |