## SGM41664 Efficient I<sup>2</sup>C Power Backup Manager with High Current Bidirectional DC/DC Converter and Capacitor Measurement Capability

## **GENERAL DESCRIPTION**

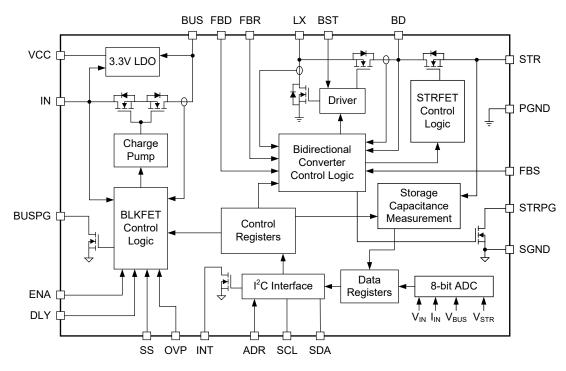

The SGM41664 is a programmable power management IC with I<sup>2</sup>C interface and integrated analog-to-digital converter (ADC) for applications that need backup power or energy storage capability such as solid-state drivers (SSD). For example, in an SSD the power is needed for a few milliseconds after an unexpected supply loss to complete any remaining write action. The integrated efficient bidirectional synchronous Buck converter/Boost charger is capable of charging storage capacitors to as high as 36V from a 2.8V to 16V input source. A quasi-fixed frequency and constant off-time controller provides fast transient response and excellent converter stability.

An integrated reverse blocking MOSFET (BLKFET) in the input allows blocking of energy leaking back to the removed source. The BLKFET has a programmable current limit in the range of 1.2A to 6.2A. BUS over-voltage protection threshold is selected based on the input source nominal voltage (3.3V, 5V or 12V) by strapping the OVP pin. The I<sup>2</sup>C interface is used to set the input current limit, switching frequency, Boost peak current limit and for measuring the storage capacitance and ESR. It is also used to monitor system variables and statuses, such as input voltage, input current, BUS voltage and storage voltage.

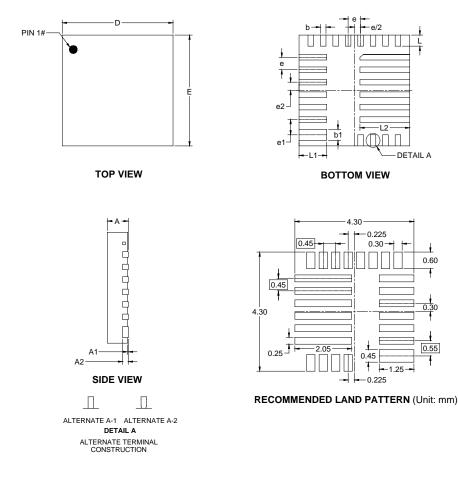

The SGM41664 is available in a Green TQFN-4×4-25L package to allow compact layout design and better space saving for higher SSD memory capacity.

# **APPLICATIONS**

Solid-state Drivers Power Backup Systems

# **FEATURES**

- Wide 2.8V to 16V Input Voltage Range

- Up to 36V Programmable Storage Voltage

- Up to 6.2A Programmable Input Current Limit

- Efficient Bidirectional DC/DC Converter

- Low R<sub>DSON</sub> for Internal MOSFETs

- Input Reverse Blocking MOSFET (BLKFET): 14mΩ

- + High-side/Low-side MOSFETs: 45mΩ/47mΩ

- STR Disconnect MOSFET (STRFET): 35mΩ

- Adjustable BLKFET Turn-On Delay and Soft-Start

- Adjustable Quasi-Fixed Frequency: 0.25MHz to 1.5MHz

- Constant Off-Time Control in Steady State

- Programmable Boost Charging Peak Current

- Autonomous or I<sup>2</sup>C Modes for Optimal Operation

- Complete Voltage and Current ADC Conversion

- Selectable Input Over-Voltage Protection

- Input Reverse Blocking to Block Leakage Current

- Short-Circuit Protection at Energy Storage Side

- Storage Capacitance Measurement

- Abnormal ESR Detection

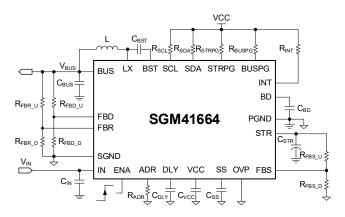

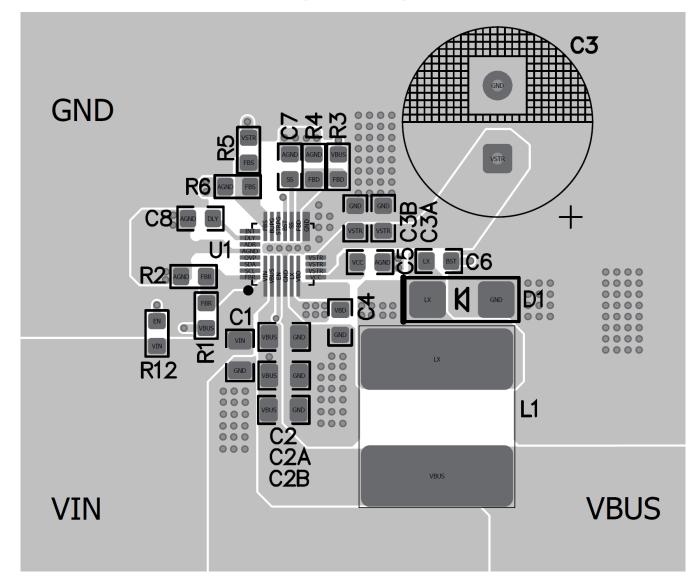

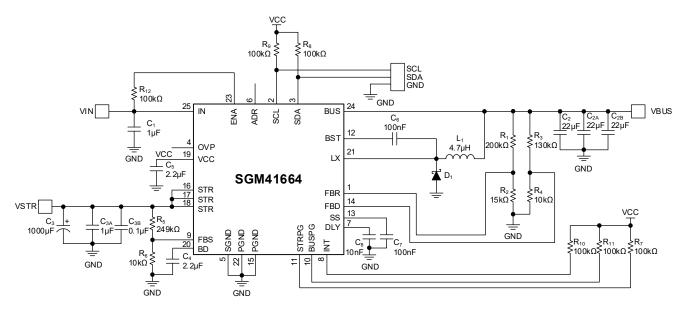

# TYPICAL APPLICATION

Figure 1. SGM41664 Typical Application

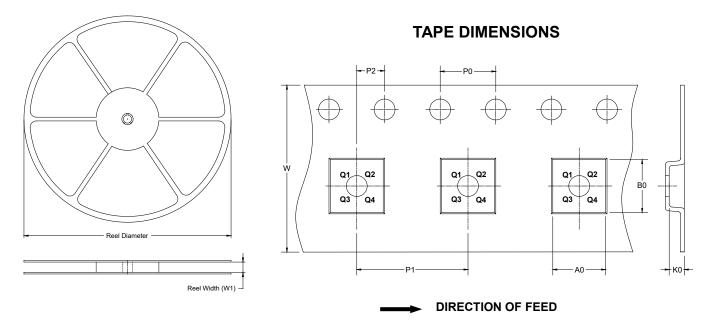

## **PACKAGE/ORDERING INFORMATION**

| MODEL    | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING          | PACKING<br>OPTION   |

|----------|------------------------|-----------------------------------|--------------------|-----------------------------|---------------------|

| SGM41664 | TQFN-4×4-25L           | -40°C to +125°C                   | SGM41664XTRQ25G/TR | SGM41664<br>XTRQ25<br>XXXXX | Tape and Reel, 3000 |

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

XXXXX

- Vendor Code

- Trace Code

- Date Code Year

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### **ABSOLUTE MAXIMUM RATINGS**

Voltage Range

| 5 5                               |                     |

|-----------------------------------|---------------------|

| STR, BD, LX, BST, FBS             | 0.3V to 38V         |

| LX (10ns transient)               | 5V to 38V           |

| IN, BUS, BUSPG, OVP, STRPG,       | ADR, FBD, FBR, ENA, |

| BD - STR, INT                     | 0.3V to 18V         |

| IN, BUS, BUSPG, OVP, STRPG, A     | DR, ENA, INT        |

| (100ns transient)                 | 0.3V to 22V         |

| SCL, SDA, DLY, SS                 | 0.3V to 6V          |

| VCC, BST - LX                     | 0.3V to 4V          |

| Package Thermal Resistance        |                     |

| TQFN-4×4-25L, θ <sub>JA</sub>     | 59°C/W              |

| Junction Temperature              | +150°C              |

| Storage Temperature Range         | 65°C to +150°C      |

| Lead Temperature (Soldering, 10s) | +260°C              |

| ESD Susceptibility                |                     |

| HBM                               | 2000V               |

| CDM                               | 1000V               |

|                                   |                     |

#### **RECOMMENDED OPERATING CONDITIONS**

| STR, BD, LX, BST, FBS Voltages       | 0.3V to 36V    |

|--------------------------------------|----------------|

| IN, BUS, BUSPG, OVP, STRPG, ADR,     | FBD, FBR, ENA, |

| BD - STR, INT Voltages               | 0.3V to 16V    |

| SCL, SDA, DLY, SS Voltages           | 0.3V to 5V     |

| VCC, BST - LX Voltages               | 0.3V to 3.3V   |

| Operating Junction Temperature Range | 40°C to +125°C |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### DISCLAIMER

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

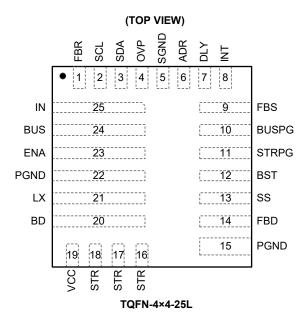

# **PIN CONFIGURATION**

# **PIN DESCRIPTION**

| NUMBER     | NAME  |                                                                                                                                                                         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                  |                         |                                      |                                        |  |  |  |

|------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------------------------|----------------------------------------|--|--|--|

| 1          | FBR   | Voltage Feedback Pin                                                                                                                                                    | /oltage Feedback Pin for Buck Mode Regulation. Use a resistor divider to set the Buck mode voltage ( $V_{REF}$ = 0.61V).                                                                                                                                                                                                                                                                                                     |                         |                                      |                                        |  |  |  |

| 2          | SCL   | I <sup>2</sup> C Interface Clock Pir                                                                                                                                    | l.                                                                                                                                                                                                                                                                                                                                                                                                                           |                         |                                      |                                        |  |  |  |

| 3          | SDA   | I <sup>2</sup> C Interface Data Pin.                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                              |                         |                                      |                                        |  |  |  |

|            |       | select the input OVP t recommended to deco                                                                                                                              | nput Over-Voltage Threshold Selection Pin (selected based on the input source voltage). Use the following table to<br>elect the input OVP threshold and the OVP logic will be latched after the power-on reset (POR) is completed. It is<br>ecommended to decoupling this pin with a 0.1μF capacitor when OVP logic is High. This pin also determines the<br>ninimum input voltage that turns on the device (POR threshold). |                         |                                      |                                        |  |  |  |

| 4          | OVP   |                                                                                                                                                                         | OVP Pin State                                                                                                                                                                                                                                                                                                                                                                                                                | Input Source<br>Voltage | V <sub>IN</sub> OVP Threshold<br>TYP |                                        |  |  |  |

|            |       |                                                                                                                                                                         | Low (OVP = GND)                                                                                                                                                                                                                                                                                                                                                                                                              | 3.3V                    | 3.8V                                 |                                        |  |  |  |

|            |       |                                                                                                                                                                         | High (OVP = IN)                                                                                                                                                                                                                                                                                                                                                                                                              | 5V                      | 6.1V                                 | -                                      |  |  |  |

|            |       |                                                                                                                                                                         | OVP Floating                                                                                                                                                                                                                                                                                                                                                                                                                 | 12V                     | 14.1V                                |                                        |  |  |  |

| 5          | SGND  | Signal Ground Pin.                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                              |                         |                                      |                                        |  |  |  |

| 6          | ADR   |                                                                                                                                                                         | ADR up by a resistor to I select address 0x5B. The                                                                                                                                                                                                                                                                                                                                                                           |                         |                                      |                                        |  |  |  |

| 7          | DLY   | Turn-On Delay Time P                                                                                                                                                    | rogram Pin for the Reverse gram this delay time: $t_{\text{DLY}}$ (r                                                                                                                                                                                                                                                                                                                                                         | Blocking MOSFET (E      | LKFET). Connect DLY                  | with a capacitor (C <sub>DLY</sub> >   |  |  |  |

| 8          | INT   |                                                                                                                                                                         | dicator Pin. INT goes high                                                                                                                                                                                                                                                                                                                                                                                                   | •                       |                                      |                                        |  |  |  |

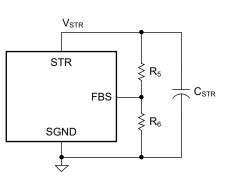

| 9          | FBS   |                                                                                                                                                                         | for Energy Storage Capacities and $R_6$ between FBS and                                                                                                                                                                                                                                                                                                                                                                      |                         |                                      | voltage. If R <sub>5</sub> resistor is |  |  |  |

| 10         | BUSPG | Open-Drain Power Go                                                                                                                                                     | od Output Pin for BUS Vo<br>high when the FBR pin vol                                                                                                                                                                                                                                                                                                                                                                        | ltage. BUSPG is pulle   | d low if FBD pin voltage             | e drops below 0.605V,                  |  |  |  |

| 11         | STRPG |                                                                                                                                                                         | od Output Pin for STR Vo<br>when the FBS voltage exc                                                                                                                                                                                                                                                                                                                                                                         |                         | d low if FBS pin voltage             | e drops below 1V, and                  |  |  |  |

| 12         | BST   | Bootstrap pin. It suppl capacitor between this                                                                                                                          | es the high-side gate driv pin and LX.                                                                                                                                                                                                                                                                                                                                                                                       | er of the bidirectional | converter. Connect a 0               | .1μF or larger ceramic                 |  |  |  |

| 13         | SS    | Soft-Start Program Pir                                                                                                                                                  | for the Reverse Blocking                                                                                                                                                                                                                                                                                                                                                                                                     | MOSFET. Use an ex       | ernal capacitor to set th            | nis soft-start time.                   |  |  |  |

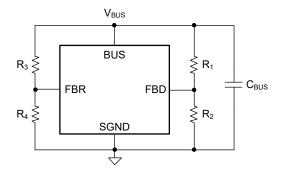

| 14         | FBD   |                                                                                                                                                                         | k Mode Detection. The co<br>or divider on BUS voltage                                                                                                                                                                                                                                                                                                                                                                        |                         |                                      |                                        |  |  |  |

| 15, 22     | PGND  | Power Ground Pins.                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                              |                         |                                      |                                        |  |  |  |

| 16, 17, 18 | STR   | Energy Storage Capac                                                                                                                                                    | citor Connection Pins. Cor                                                                                                                                                                                                                                                                                                                                                                                                   | nect the storage capa   | citors between STR an                | d PGND.                                |  |  |  |

| 19         | VCC   | 3.3V Internal LDO Out                                                                                                                                                   | 3.3V Internal LDO Output Pin. Decouple VCC to GND with at least 2.2µF ceramic capacitor (X5R or better).                                                                                                                                                                                                                                                                                                                     |                         |                                      |                                        |  |  |  |

| 20         | BD    | Drain Pin of the STR Disconnect FET (STRFET) and the Input of the Buck Converter. BD must be decoupled to PGND with at least a 2.2µF ceramic capacitor (X5R or better). |                                                                                                                                                                                                                                                                                                                                                                                                                              |                         |                                      |                                        |  |  |  |

| 21         | LX    | Converter Switching N                                                                                                                                                   | Converter Switching Node Pin. Connect it to the inductor and bootstrap capacitor.                                                                                                                                                                                                                                                                                                                                            |                         |                                      |                                        |  |  |  |

| 23         | ENA   | Enable Control Pin for                                                                                                                                                  | Enable Control Pin for the BLKFET with an internal 1M $\Omega$ pull-down resistor. Logic high enables the BLKFET.                                                                                                                                                                                                                                                                                                            |                         |                                      |                                        |  |  |  |

| 24         | BUS   | BUS Output Pin. It mu                                                                                                                                                   | st be decoupled to PGND                                                                                                                                                                                                                                                                                                                                                                                                      | with at least 22µF ce   | amic capacitor (X5R or               | better).                               |  |  |  |

| 25         | IN    | Power Supply Input Pi                                                                                                                                                   | n. Decouple it to PGND w                                                                                                                                                                                                                                                                                                                                                                                                     | ith at least 0.1µF cera | mic capacitor.                       |                                        |  |  |  |

# Efficient Power Backup Manager with High Current Bidirectional DC/DC Converter and Capacitor Measurement Capability

# ELECTRICAL CHARACTERISTICS

$(V_{IN} = 5V, V_{BUS} = 5V, L = 4.7\mu H, V_{BD} = V_{STR} = 12V, T_J = -40^{\circ}C$  to +125°C, typical values are at  $T_J = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                                          | SYMBOL              | CONDITIONS                                                          | MIN   | TYP             | MAX   | UNITS |

|----------------------------------------------------|---------------------|---------------------------------------------------------------------|-------|-----------------|-------|-------|

| Device Power Supply (IN)                           |                     | 1                                                                   |       |                 |       |       |

| Input Voltage Range                                | V <sub>IN</sub>     |                                                                     | 2.8   |                 | 16    | V     |

| Input Rising for Activating I <sup>2</sup> C       | V <sub>IN4C</sub>   | V <sub>IN</sub> rising                                              |       | 2.5             | 2.8   | V     |

|                                                    |                     | OVP = low                                                           |       | 2.5             | 2.8   |       |

| Power-On Reset (POR) Rising Threshold ( $V_{IN}$ ) | VPORR               | OVP = high                                                          |       | 3.5             | 3.7   | V     |

|                                                    |                     | OVP = floating                                                      |       | 8.4             | 9     |       |

|                                                    |                     | OVP = low                                                           | 2.0   | 2.4             |       |       |

| POR Falling Threshold (V <sub>IN</sub> )           | VPORF               | OVP = high                                                          | 3.1   | 3.3             |       | V     |

|                                                    |                     | OVP = floating                                                      | 7.6   | 8               |       |       |

| On-Resistance of BLKFET                            | R <sub>DSON_R</sub> |                                                                     |       | 14              | 25    | mΩ    |

|                                                    |                     | V <sub>IN</sub> = 0V, V <sub>BUS</sub> = 16V, V <sub>ENA</sub> = 0V |       | 0.1             | 2     |       |

| Reverse Blocking Leakage Current                   | I <sub>RBLK</sub>   | V <sub>IN</sub> = 16V, V <sub>BUS</sub> = 0V, V <sub>ENA</sub> = 0V |       | 0.1             | 2     | μA    |

| Input Supply Current Before POR                    | I <sub>IN_POR</sub> | V <sub>IN</sub> rises to 8V, OVP = floating,<br>ENA = high          |       |                 | 267   | μA    |

| Bias Current (IN)                                  | I <sub>BIAS</sub>   | V <sub>IN</sub> = 5V, OVP = high,<br>DC/DC converter is disabled    |       | 1400            |       | μA    |

| Reverse Blocking Range                             | V <sub>RB</sub>     |                                                                     |       |                 | 16    | V     |

|                                                    |                     | OVP = low, internal accuracy                                        | 3.67  | 3.8             | 3.90  | V     |

| Input Over-Voltage Threshold (1)                   | V <sub>OVP</sub>    | OVP = high, internal accuracy                                       | 5.91  | 6.1             | 6.23  |       |

|                                                    |                     | OVP = floating, internal accuracy                                   | 13.77 | 14.1            | 14.45 |       |

|                                                    |                     | OVP = low                                                           |       | 150             |       | mV    |

| Input Over-Voltage Threshold Hysteresis            | V <sub>OVPHYS</sub> | OVP = high                                                          |       | 200             |       |       |

|                                                    |                     | OVP = floating                                                      |       | 400             |       |       |

| BLKFET Turn-On Delay Time                          | t <sub>DLY</sub>    | $C_{DLY} = 10 n F^{(1)}$                                            |       | 2.5             |       | ms    |

| Soft-Start Time                                    | t <sub>ss</sub>     | C <sub>SS</sub> = 100nF <sup>(2)</sup>                              |       | 16.5            |       | ms    |

| Current Limit Program Range                        | I <sub>LIM</sub>    |                                                                     | 1.2   |                 | 6.2   | Α     |

| Current Limit Accuracy                             |                     | LSP[5:3] = 011                                                      | -9    |                 | 9     | %     |

| BUSPG Threshold <sup>(1)</sup>                     | VBUSPGH             | V <sub>FBR</sub> rising, internal accuracy                          | 0.611 | 0.635           | 0.655 | V     |

| BOSEG Threshold                                    | VBUSPGL             | V <sub>FBD</sub> falling, internal accuracy                         | 0.590 | 0.605           | 0.619 | V     |

| Internal LDO Output Voltage                        | V <sub>VCC</sub>    | V <sub>IN</sub> > 3.3V                                              |       | 3.3             |       | v     |

| internal LDO Output voltage                        | V VCC               | $V_{IN} \le 3.3V$                                                   |       | V <sub>IN</sub> |       |       |

| ENA Logic Voltage                                  | VENAH               |                                                                     | 1.1   |                 |       | V     |

|                                                    | VENAL               |                                                                     |       |                 | 0.5   | V     |

| OVP Pin Logic Voltage                              | V <sub>OVPH</sub>   |                                                                     | 1.1   |                 |       | V     |

|                                                    | V <sub>OVPL</sub>   |                                                                     |       |                 | 0.5   | V     |

| Bidirectional DC/DC Converter                      |                     |                                                                     |       |                 |       |       |

| BUS Side Operation Voltage Range                   | V <sub>BUSOP</sub>  |                                                                     | 2.8   |                 | 16    | V     |

| STR Side Buck Operation Voltage Range              | V <sub>STROP</sub>  |                                                                     | 2.8   |                 | 36    | V     |

| Boost Minimum Peak Current                         | I <sub>PMIN</sub>   |                                                                     |       | 250             |       | mA    |

| Switching Frequency                                | f <sub>SWBST</sub>  | SF[1:0] = 01                                                        |       | 500             |       | kHz   |

| Minimum LSFET On-Time                              | $t_{OFF}_{MINL}$    | During Boost/Buck mode                                              |       | 110             |       | ns    |

| Minimum HSFET On-Time                              | t <sub>on_MIN</sub> | During Boost/Buck mode                                              |       | 110             |       | ns    |

| Boost CV Mode Voltage Reference                    | $V_{REF\_BST}$      | T <sub>J</sub> = +25°C, internal accuracy                           | 1.188 | 1.205           | 1.222 | V     |

# Efficient Power Backup Manager with High Current Bidirectional DC/DC Converter and Capacitor Measurement Capability

## **ELECTRICAL CHARACTERISTICS (continued)**

(V<sub>IN</sub> = 5V, V<sub>BUS</sub> = 5V, L = 4.7µH, V<sub>BD</sub> = V<sub>STR</sub> = 12V, T<sub>J</sub> = -40°C to +125°C, typical values are at T<sub>J</sub> = +25°C, unless otherwise noted.)

| PARAMETER                                                                | SYMBOL                        | CONDITIONS                                                              | MIN   | TYP   | MAX   | UNITS |

|--------------------------------------------------------------------------|-------------------------------|-------------------------------------------------------------------------|-------|-------|-------|-------|

| $V_{\mbox{\scriptsize FBS}}$ Boost Burst Mode Stop Switching Threshold   | V <sub>BRT_R</sub>            | V <sub>FBS</sub> rising                                                 |       | 1.2   |       | V     |

| $V_{\mbox{\scriptsize FBS}}$ Boost Burst Mode Switching Resume Threshold | $V_{BRT_F}$                   | V <sub>FBS</sub> falling                                                |       | 1.17  |       | V     |

| V <sub>FBS</sub> Boost Burst Mode Threshold Accuracy                     |                               |                                                                         | -3.0  |       | 5.0   | %     |

| V <sub>FBD</sub> Buck Detection Voltage Reference <sup>(1)</sup>         | V <sub>BUCK_DET</sub>         | V <sub>FBD</sub> falling, internal accuracy                             | 0.590 | 0.605 | 0.619 | V     |

| V <sub>FBR</sub> Buck Regulation Voltage Reference <sup>(1)</sup>        | $V_{\text{BUCK}\_\text{REG}}$ | Internal accuracy                                                       | 0.592 | 0.610 | 0.624 | V     |

| Maximum Cycle-by-Cycle Buck Peak Current                                 | I <sub>PK_BK</sub>            | V <sub>STR</sub> = 28V, V <sub>BUS</sub> = 8.6V, T <sub>J</sub> = +25°C | 7.5   | 8.4   |       | А     |

|                                                                          | V <sub>STRPGH</sub>           | V <sub>FBS</sub> rising                                                 |       | 1.05  |       | V     |

| V <sub>FBS</sub> STRPG Threshold                                         | V <sub>STRPGL</sub>           | V <sub>FBS</sub> falling                                                |       | 1.00  |       | V     |

| STR Short-Circuit Detection Threshold in Pre-charge                      | V <sub>STRSC</sub>            | V <sub>FBS</sub> value                                                  |       | 0.7   |       | V     |

| Pre-charge Current                                                       | I <sub>PRECHG</sub>           | V <sub>STR</sub> = 7.5V, V <sub>BD</sub> = 15V                          |       | 150   |       | mA    |

| R <sub>DSON</sub> of High-side FET                                       | R <sub>DSON_H1</sub>          |                                                                         |       | 45    | 74    | mΩ    |

| R <sub>DSON</sub> of Low-side FET                                        | R <sub>DSON_L1</sub>          |                                                                         |       | 47    | 76    | mΩ    |

| R <sub>DSON</sub> of STR Disconnect FET                                  | R <sub>DSON_D</sub>           |                                                                         |       | 35    | 59    | mΩ    |

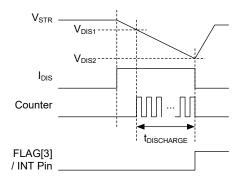

| STR Capacitor Measurement                                                |                               |                                                                         |       |       |       |       |

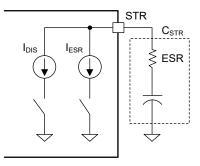

| Capacitance Measurement Discharge Current                                | I <sub>DIS</sub>              | DCP[7:6] = 01                                                           |       | 5     |       | mA    |

| Internal Counter Clock                                                   | f <sub>CLK</sub>              |                                                                         |       | 500   |       | Hz    |

| Abnormal ESR Detection Discharge Current                                 | I <sub>ESR</sub>              |                                                                         |       | 1     |       | А     |

| I <sup>2</sup> C and Logic Interfaces (SDA, SCL, ADR, INT)               |                               | ·                                                                       |       |       |       |       |

| High State Input Voltage                                                 | VIH                           | SDA and SCL pins                                                        | 1.5   |       |       | V     |

| Low State Input Voltage                                                  | V <sub>IL</sub>               | SDA and SCL pins                                                        |       |       | 0.4   | V     |

| Low State Output Voltage                                                 | V <sub>OL</sub>               | Sink 4mA, INT pin                                                       |       |       | 0.5   | V     |

|                                                                          | V <sub>ADRH</sub>             |                                                                         | 1.1   |       |       | V     |

| ADR Pin Logic Voltage                                                    | V <sub>ADRL</sub>             |                                                                         |       |       | 0.5   | V     |

| ADC                                                                      |                               | ·                                                                       |       |       |       |       |

| ADC Reference Voltage                                                    | $V_{\text{REF}\_\text{ADC}}$  |                                                                         |       | 1     |       | V     |

| ADC Resolution                                                           |                               |                                                                         |       | 8     |       | Bits  |

| ADC Conversion Time                                                      |                               | For one variable                                                        |       | 40    |       | μs    |

| Thermal Protection                                                       |                               |                                                                         |       | •     | •     |       |

| Thermal Shutdown Temperature                                             | T <sub>SD</sub>               |                                                                         |       | 150   |       | °C    |

| Thermal Recovery Hysteresis                                              | T <sub>HYS</sub>              |                                                                         |       | 25    |       | °C    |

| Thermal Warning Threshold                                                | T <sub>WRN</sub>              |                                                                         |       | 125   |       | °C    |

#### NOTES:

1. These values are guaranteed by FT.

2. Recommended Delay Time Program Table

| C <sub>DLY</sub> (nF) | None | 10  | 47   | 100  |

|-----------------------|------|-----|------|------|

| Delay Time (ms)       | 1.0  | 2.5 | 11.8 | 25.0 |

3. Recommended Soft-Start Time Program Table

| C <sub>ss</sub> (nF) | None | 10  | 47  | 100  |

|----------------------|------|-----|-----|------|

| Rise Time (ms)       | 1.0  | 1.7 | 7.7 | 16.5 |

# Efficient Power Backup Manager with High Current Bidirectional DC/DC Converter and Capacitor Measurement Capability

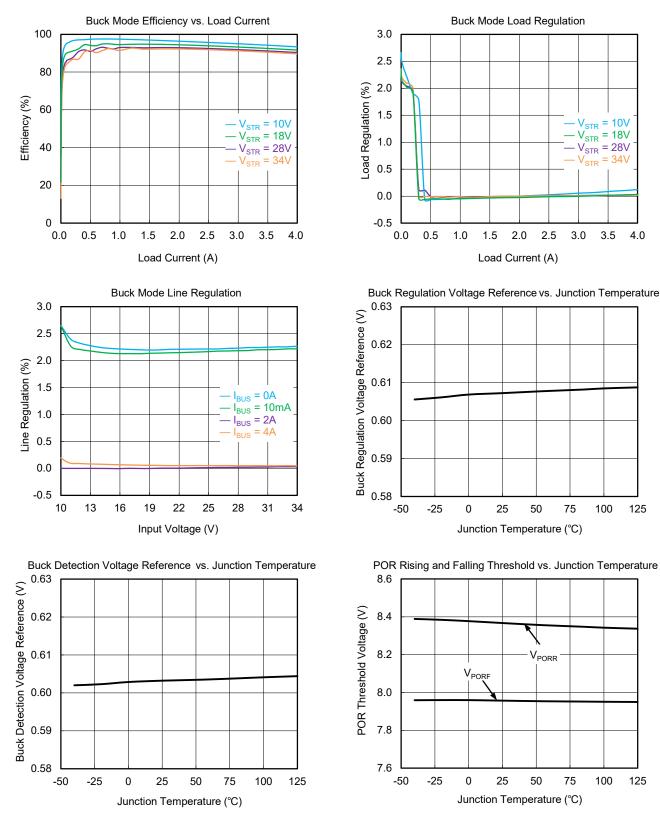

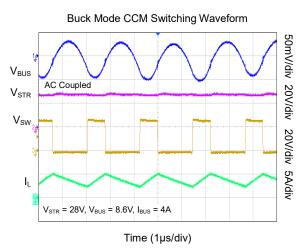

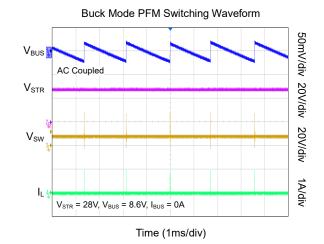

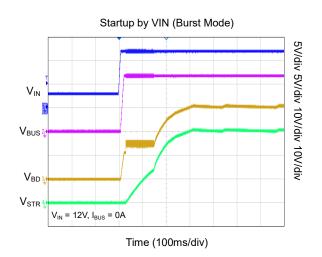

## **TYPICAL PERFORMANCE CHARACTERISTICS**

$V_{IN}$  = 12V,  $V_{BUS_{REG}}$  = 8.7V,  $V_{BUS_{DET}}$  = 8.5V, OVP floating, L = 4.7µH,  $V_{BD}$  =  $V_{STR}$  = 31V, unless otherwise noted.

SG Micro Corp

# Efficient Power Backup Manager with High Current Bidirectional DC/DC Converter and Capacitor Measurement Capability

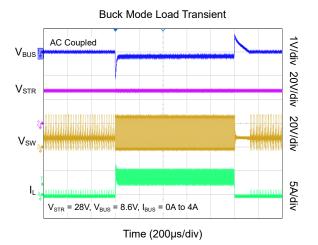

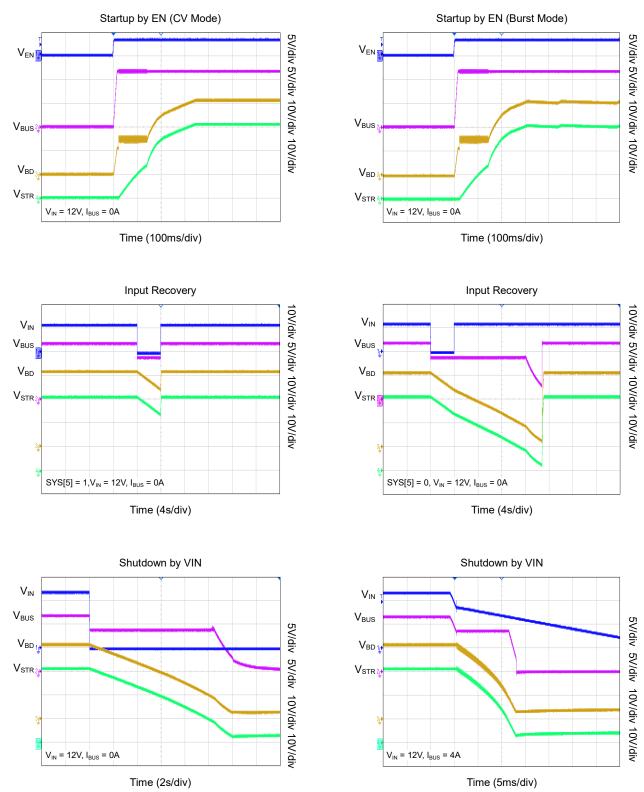

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$V_{IN}$  = 12V,  $V_{BUS_{REG}}$  = 8.7V,  $V_{BUS_{DET}}$  = 8.5V, OVP floating, L = 4.7µH,  $V_{BD}$  =  $V_{STR}$  = 31V, unless otherwise noted.

SG Micro Corp

# Efficient Power Backup Manager with High Current Bidirectional DC/DC Converter and Capacitor Measurement Capability

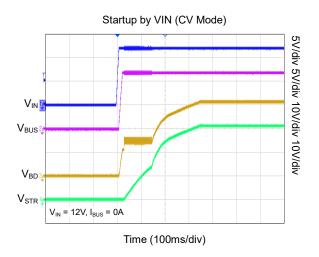

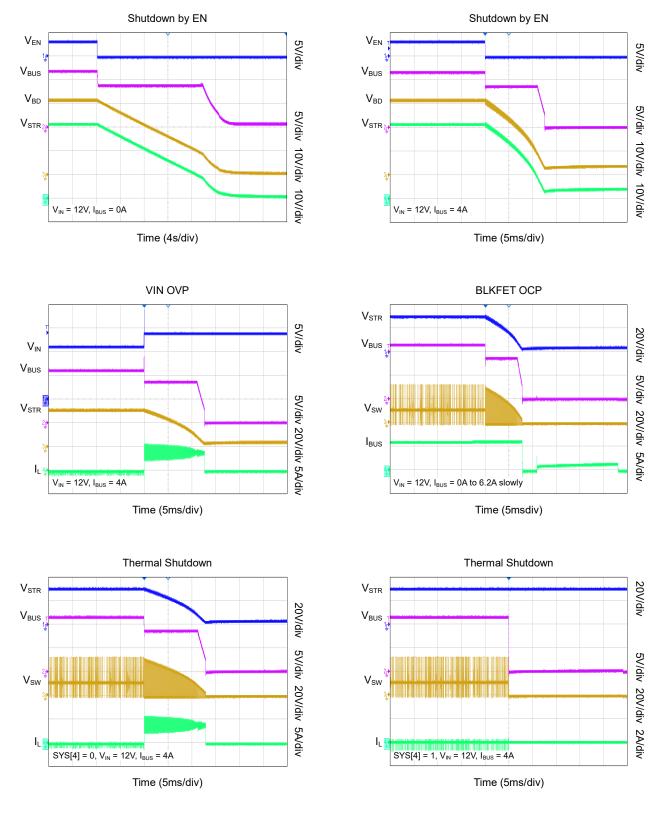

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$V_{IN}$  = 12V,  $V_{BUS_{REG}}$  = 8.7V,  $V_{BUS_{DET}}$  = 8.5V, OVP floating, L = 4.7µH,  $V_{BD}$  =  $V_{STR}$  = 31V, unless otherwise noted.

# Efficient Power Backup Manager with High Current Bidirectional DC/DC Converter and Capacitor Measurement Capability

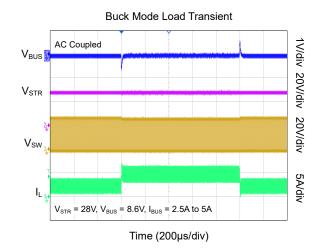

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$V_{IN} = 12V$ ,  $V_{BUS_{REG}} = 8.7V$ ,  $V_{BUS_{DET}} = 8.5V$ , OVP floating,  $L = 4.7\mu$ H,  $V_{BD} = V_{STR} = 31V$ , unless otherwise noted.

SG Micro Corp

# **REGISTER ADDRESS MAPING (17, 8-Bit Registers)**

All registers are 8-bit and individual bits are named from D[0] (LSB) to D[7] (MSB). Slave Device Address is selectable: 0x59, 0x5A or 0x5B.

| FUNCTION     | STAT                  | FLAG              | MASK              | THRESHOLD SETTING     | ENABLE  |

|--------------|-----------------------|-------------------|-------------------|-----------------------|---------|

| DEVICE_REV   | —                     | —                 | —                 | 0x00[5:3]             | —       |

| VIN_OVP      | —                     | 0x0F[7]           | 0x0E[7]           | —                     | 0x01[7] |

| ILIM_IN      | —                     | 0x0F[6]           | 0x0E[6]           | 0x01[5:3]             | —       |

| BLKFET       | 0x10[0]               | —                 | —                 | —                     | 0x01[0] |

| IDIS_CSTR    | —                     | —                 | —                 | 0x02[7:6]             | —       |

| CSTR_MEAS    | 0x07[7:0] & 0x08[7:0] | 0x0F[3]           | 0x0E[3]           | 0x04[7:0] & 0x05[7:0] | 0x06[5] |

| ESR_DET      | 0x09[0]               | 0x0F[3]           | 0x0E[3]           | 0x06[3:2]             | 0x06[5] |

| STR_SCP      | —                     | 0x0F[5]           | 0x0E[5]           | —                     | —       |

| STR_OVP      | —                     | 0x10[3]           | —                 | 0x0B[4:0]             | —       |

| FSW_SET      | —                     | —                 | —                 | 0x06[1:0]             | —       |

| BOOST        | —                     | —                 | —                 | 0x02[3:1] & 0x06[4]   | 0x02[0] |

| BUCK         | —                     | —                 | —                 | —                     | 0x02[0] |

| BUCK_OFF     | —                     | _                 | —                 | 0x03[7:0]             | —       |

| RECOVER_MODE | —                     | —                 | —                 | 0x10[5]               |         |

| RB_PROT      | —                     | 0x0F[4]           | 0x0E[4]           | —                     | 0x06[6] |

| THERMAL      | —                     | 0x0F[1] & 0x0F[0] | 0x0E[1] & 0x0E[0] | 0x10[4]               |         |

| VBUS_PG      | —                     | 0x10[2]           | —                 | —                     |         |

| VIN_PG       | —                     | 0x10[1]           | —                 | —                     | —       |

| ADC          |                       | 0x0F[2]           | 0x0E[2]           | —                     | 0x10[7] |

| IIN_ADC      | 0x09[7:2]             | _                 | —                 | —                     |         |

| VBUS_ADC     | 0x0A[7:0]             | _                 |                   | —                     | _       |

| VIN_ADC      | 0x0C[7:0]             | —                 | —                 | —                     | —       |

| VSTR_ADC     | 0x0D[7:0]             |                   |                   | —                     |         |

# **REGISTER DESCRIPTION**

Bit Types: **R**: Read only bit **R/W**: Read or write bit **R/WC**: Read or write bit. Writing a '1' clears the bit. Writing a '0' has no effect.

## REG0x00: Vendor ID Register Address (reset = 0x00)

| BITS | BIT NAME | DEFAULT | TYPE | DESCRIPTION                            | COMMENT |

|------|----------|---------|------|----------------------------------------|---------|

| D[7] | CTRL[7]  | 0       | R    | Reserved                               |         |

| D[6] | CTRL[6]  | 0       | R    | Reserved                               |         |

| D[5] | CTRL[5]  | 0       | R    |                                        |         |

| D[4] | CTRL[4]  | 0       | R    | Device Revision Bits<br>000 = SGM41664 |         |

| D[3] | CTRL[3]  | 0       | R    |                                        |         |

| D[2] | CTRL[2]  | 0       | R    | Reserved                               |         |

| D[1] | CTRL[1]  | 0       | R    | Reserved                               |         |

| D[0] | CTRL[0]  | 0       | R    | Reserved                               |         |

## **REG0x01: BLKFET Control Parameter Programming Register Address (reset = 0x39)**

| BITS | BIT NAME | DEFAULT | TYPE | DESCRIPTION                                                                                             | COMMENT |

|------|----------|---------|------|---------------------------------------------------------------------------------------------------------|---------|

| D[7] | LSP[7]   | 0       | R/W  | V <sub>IN</sub> OVP Enable Bit<br>0 = OVP function is enabled (default)<br>1 = OVP function is disabled |         |

| D[6] | LSP[6]   | 0       | R    | Reserved                                                                                                |         |

| D[5] | LSP[5]   | 1       | R/W  | Input Current Limit Threshold<br>000 = 1.2A<br>001 = 2A                                                 |         |

| D[4] | LSP[4]   | 1       | R/W  | 010 = 2.5A<br>011 = 3A<br>100 = 3.5A                                                                    |         |

| D[3] | LSP[3]   | 1       | R/W  | 101 = 4A<br>110 = 4.5A<br>111 = 6.2A (default)                                                          |         |

| D[2] | LSP[2]   | 0       | R    | Reserved                                                                                                |         |

| D[1] | LSP[1]   | 0       | R    | Reserved                                                                                                |         |

| D[0] | LSP[0]   | 1       | R/W  | ENA Bit<br>0 = BLKFET is disabled<br>1 = BLKFET is enabled (default)                                    |         |

## **REGISTER DESCRIPTION (continued)**

**REG0x02:** DC/DC Converter Control Parameter Programming Register Address (reset = 0xC9)

| BITS | BIT NAME | DEFAULT | TYPE | DESCRIPTION                                                                                                      | COMMENT |

|------|----------|---------|------|------------------------------------------------------------------------------------------------------------------|---------|

| D[7] | DCP[7]   | 1       | R/W  | C <sub>STR</sub> Measurement Discharge Current<br>00 = 2mA<br>01 = 5mA                                           |         |

| D[6] | DCP[6]   | 1       | R/W  | 10 = 10mA<br>11 = 20mA (default)                                                                                 |         |

| D[5] | DCP[5]   | 0       | R    | Reserved                                                                                                         |         |

| D[4] | DCP[4]   | 0       | R    | Reserved                                                                                                         |         |

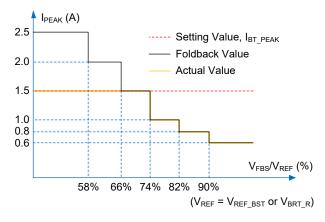

| D[3] | DCP[3]   | 1       | R/W  | Boost Peak Current<br>000 = 300mA<br>001 = 500mA                                                                 |         |

| D[2] | DCP[2]   | 0       | R/W  | 010 = 600mA<br>011 = 800mA<br>100 = 1A (default)                                                                 |         |

| D[1] | DCP[1]   | 0       | R/W  | 101 = 1.5A<br>110 = 2A<br>111 = 2.5A                                                                             |         |

| D[0] | DCP[0]   | 1       | R/W  | ENCON, DC/DC Converter Enable Bit<br>0 = DC/DC converter is disabled<br>1 = DC/DC converter is enabled (default) |         |

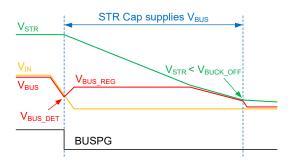

## REG0x03: Buck-Off Voltage Programming Register Address (reset = 0x37)

| BITS | BIT NAME | DEFAULT | TYPE | DESCRIPTION                  | COMMENT                                                                                                |

|------|----------|---------|------|------------------------------|--------------------------------------------------------------------------------------------------------|

| D[7] | OFF[7]   | 0       | R/W  |                              |                                                                                                        |

| D[6] | OFF[6]   | 0       | R/W  |                              | Default: 0x37. V <sub>BUCK_OFF</sub> = 2.64V                                                           |

| D[5] | OFF[5]   | 1       | R/W  |                              | V <sub>BUCK_OFF</sub> = OFF[7:0] × 0.048V                                                              |

| D[4] | OFF[4]   | 1       | R/W  | Puel Off Voltage Programming | The $V_{\text{BUCK}_{OFF}}$ program range is 2.64V to 12V.                                             |

| D[3] | OFF[3]   | 0       | R/W  | Buck-Off Voltage Programming | Example:                                                                                               |

| D[2] | OFF[2]   | 1       | R/W  |                              | If OFF[7:0] = 0x37, then<br>$V_{BUCK OFF} = (3 \times 16^{1} + 7 \times 16^{0}) \times 0.048 = 2.64V.$ |

| D[1] | OFF[1]   | 1       | R/W  |                              | VBUCK_OFF (0 4 10 1 4 10 ) 4 0.040 2.040.                                                              |

| D[0] | OFF[0]   | 1       | R/W  |                              |                                                                                                        |

#### REG0x04: VDIS1 Programming Register Address (reset = 0xA6)

| BITS | BIT NAME | DEFAULT | TYPE | DESCRIPTION                                            | COMMENT                                                                                      |

|------|----------|---------|------|--------------------------------------------------------|----------------------------------------------------------------------------------------------|

| D[7] | VDIS1[7] | 1       | R/W  |                                                        |                                                                                              |

| D[6] | VDIS1[6] | 0       | R/W  |                                                        | Default: 0xA6. V <sub>DIS1</sub> = 24.9V                                                     |

| D[5] | VDIS1[5] | 1       | R/W  |                                                        | 5.01                                                                                         |

| D[4] | VDIS1[4] | 0       | R/W  | $V_{DIS1}$ Threshold Programming (For C <sub>STR</sub> | $V_{DIS1} = VDIS1[7:0] \times 0.15V$<br>The $V_{DIS1}$ voltage program range is 1.5V to 36V. |

| D[3] | VDIS1[3] | 0       | R/W  | measurement)                                           | Example:                                                                                     |

| D[2] | VDIS1[2] | 1       | R/W  |                                                        | If $VDIS1[7:0] = 0xA6$ , then                                                                |

| D[1] | VDIS1[1] | 1       | R/W  |                                                        | $V_{\text{DIS1}} = (10 \times 16^{1} + 6 \times 16^{0}) \times 0.15 = 24.9 \text{V}.$        |

| D[0] | VDIS1[0] | 0       | R/W  |                                                        |                                                                                              |

## **REGISTER DESCRIPTION (continued)**

#### **REG0x05: VDIS2 Programming Register Address (reset = 0x8F)**

| BITS | BIT NAME | DEFAULT | TYPE | DESCRIPTION                                                   | COMMENT                                                                                       |

|------|----------|---------|------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| D[7] | VDIS2[7] | 1       | R/W  |                                                               |                                                                                               |

| D[6] | VDIS2[6] | 0       | R/W  |                                                               | Default: 0x8F. V <sub>DIS2</sub> = 21.45V                                                     |

| D[5] | VDIS2[5] | 0       | R/W  |                                                               |                                                                                               |

| D[4] | VDIS2[4] | 0       | R/W  | V <sub>DIS2</sub> Threshold Programming (For C <sub>STR</sub> | $V_{DIS2}$ = VDIS2[7:0] × 0.15V<br>The V <sub>DIS2</sub> voltage program range is 1.5V to 36V |

| D[3] | VDIS2[3] | 1       | R/W  | measurement)                                                  | Example:                                                                                      |

| D[2] | VDIS2[2] | 1       | R/W  |                                                               | If $VDIS2[7:0] = 0x8F$ , then                                                                 |

| D[1] | VDIS2[1] | 1       | R/W  |                                                               | $V_{DIS2} = (8 \times 16^{1} + 15 \times 16^{0}) \times 0.15 = 21.45V.$                       |

| D[0] | VDIS2[0] | 1       | R/W  |                                                               |                                                                                               |

# REG0x06: Switching Frequency, $C_{STR}$ Measuring, Reverse Block and CV Mode Program Register Address (reset = 0x01)

| BITS | BIT NAME | DEFAULT | TYPE | DESCRIPTION                                                                                                                                              | COMMENT                                                                                                                                           |

|------|----------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| D[7] | SF[7]    | 0       | R    | Reversed                                                                                                                                                 |                                                                                                                                                   |

| D[6] | SF[6]    | 0       | R/W  | Reverse Block Enable Bit<br>0 = BLKFET turns off once the reverse<br>current exceeds 0.5A<br>1 = BLKFET unchanged if the reverse<br>current exceeds 0.5A |                                                                                                                                                   |

| D[5] | SF[5]    | 0       | R/W  | C <sub>STR</sub> Measurement Enable<br>Default: 0                                                                                                        | Capacitance measurement starts when SF[5] changes from 0 to 1.                                                                                    |

| D[4] | SF[4]    | 0       | R/W  | Boost Operation Mode<br>0 = CV mode (Default)<br>1 = Burst mode                                                                                          | In Burst mode, it is recommended to use a BST capacitor with a relatively small capacitance value to accelerate the recharge speed, such as 47nF. |

| D[3] | SF[3]    | 0       | R/W  | C <sub>STR</sub> ESR Detection Threshold<br>00 = 50mV (default)<br>01 = 100mV                                                                            |                                                                                                                                                   |

| D[2] | SF[2]    | 0       | R/W  | 10 = 150mV<br>11 = 200mV                                                                                                                                 |                                                                                                                                                   |

| D[1] | SF[1]    | 0       | R/W  | Switching Frequency<br>00 = 250kHz<br>01 = 500kHz (default)                                                                                              |                                                                                                                                                   |

| D[0] | SF[0]    | 1       | R/W  | 10 = 1MHz<br>11 = 1.5MHz                                                                                                                                 |                                                                                                                                                   |

### **REG0x07:** C<sub>STR</sub> Discharge Timer High Byte Register Address (reset = 0x00)

| BITS | BIT NAME | DEFAULT | TYPE | DESCRIPTION | COMMENT                           |

|------|----------|---------|------|-------------|-----------------------------------|

| D[7] | TIMH[7]  | 0       | R    | 1 = 65536ms |                                   |

| D[6] | TIMH[6]  | 0       | R    | 1 = 32768ms |                                   |

| D[5] | TIMH[5]  | 0       | R    | 1 = 16384ms |                                   |

| D[4] | TIMH[4]  | 0       | R    | 1 = 8192ms  | Capacitor Discharge Timer Reading |

| D[3] | TIMH[3]  | 0       | R    | 1 = 4096ms  | Range: 0 - 131070ms               |

| D[2] | TIMH[2]  | 0       | R    | 1 = 2048ms  |                                   |

| D[1] | TIMH[1]  | 0       | R    | 1 = 1024ms  |                                   |

| D[0] | TIMH[0]  | 0       | R    | 1 = 512ms   |                                   |

## \_\_\_\_\_

SGM41664

## **REGISTER DESCRIPTION (continued)**

### **REG0x08:** C<sub>STR</sub> Discharge Timer Low Byte Register Address (reset = 0x00)

| BITS | BIT NAME | DEFAULT | TYPE | DESCRIPTION | COMMENT                           |

|------|----------|---------|------|-------------|-----------------------------------|

| D[7] | TIML[7]  | 0       | R    | 1 = 256ms   |                                   |

| D[6] | TIML[6]  | 0       | R    | 1 = 128ms   |                                   |

| D[5] | TIML[5]  | 0       | R    | 1 = 64ms    |                                   |

| D[4] | TIML[4]  | 0       | R    | 1 = 32ms    | Capacitor Discharge Timer Reading |

| D[3] | TIML[3]  | 0       | R    | 1 = 16ms    | Range: 0 - 131070ms               |

| D[2] | TIML[2]  | 0       | R    | 1 = 8ms     |                                   |

| D[1] | TIML[1]  | 0       | R    | 1 = 4ms     |                                   |

| D[0] | TIML[0]  | 0       | R    | 1 = 2ms     |                                   |

#### **REG0x09: ADC I<sub>IN</sub> Data and ESR Detection Status Register Address (reset = 0x00)**

| BITS | BIT NAME | DEFAULT | TYPE | DESCRIPTION                                                                   | COMMENT                                                                                                                 |

|------|----------|---------|------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| D[7] | LSC[7]   | 0       | R    | 1 = 4.8A                                                                      |                                                                                                                         |

| D[6] | LSC[6]   | 0       | R    | 1 = 2.4A                                                                      |                                                                                                                         |

| D[5] | LSC[5]   | 0       | R    | 1 = 1.2A                                                                      | Input Current ADC Results Reading<br>Range: 0 - 9.45A                                                                   |

| D[4] | LSC[4]   | 0       | R    | 1 = 0.6A                                                                      | 6 bits (0 - 63) × 0.15A resolution                                                                                      |

| D[3] | LSC[3]   | 0       | R    | 1 = 0.3A                                                                      |                                                                                                                         |

| D[2] | LSC[2]   | 0       | R    | 1 = 0.15A                                                                     |                                                                                                                         |

| D[1] | LSC[1]   | 0       | R    | Reserved                                                                      |                                                                                                                         |

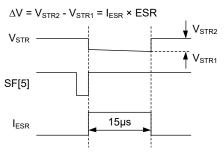

| D[0] | LSC[0]   | 0       | R    | Detected ESR Status (ESR <sub>CSTR</sub> )<br>0 = ESR normal<br>1 = ESR error | Error is detected if the $\Delta V_{STR}$ (= ESR × I <sub>ESR</sub> ) is higher than the threshold set in SF[3:2] bits. |

#### **REG0x0A: ADC V<sub>BUS</sub> Data Register Address (reset = 0x00)**

| BITS | BIT NAME | DEFAULT | TYPE | DESCRIPTION | COMMENT                                                 |

|------|----------|---------|------|-------------|---------------------------------------------------------|

| D[7] | BUS[7]   | 0       | R    | 1 = 8.192V  |                                                         |

| D[6] | BUS[6]   | 0       | R    | 1 = 4.096V  |                                                         |

| D[5] | BUS[5]   | 0       | R    | 1 = 2.048V  |                                                         |

| D[4] | BUS[4]   | 0       | R    | 1 = 1.024V  | V <sub>BUS</sub> ADC Results Reading                    |

| D[3] | BUS[3]   | 0       | R    | 1 = 0.512V  | Range: 0 - 16.32V<br>8 bits (0 - 255) × 64mV resolution |

| D[2] | BUS[2]   | 0       | R    | 1 = 0.256V  |                                                         |

| D[1] | BUS[1]   | 0       | R    | 1 = 0.128V  |                                                         |

| D[0] | BUS[0]   | 0       | R    | 1 = 0.064V  |                                                         |

#### **REG0x0B: STR Over-Voltage Protection Programming Register Address (reset = 0x1D)**

| BITS | BIT NAME | DEFAULT | TYPE | DESCRIPTION                                | COMMENT                                                                    |

|------|----------|---------|------|--------------------------------------------|----------------------------------------------------------------------------|

| D[7] | OVP[7]   | 0       | R    | Reserved                                   |                                                                            |

| D[6] | OVP[6]   | 0       | R    | Reserved                                   |                                                                            |

| D[5] | OVP[5]   | 0       | R    | Reserved                                   |                                                                            |

| D[4] | OVP[4]   | 1       | R/W  |                                            | Default: 0x1D, V <sub>STROVP</sub> = 36V                                   |

| D[3] | OVP[3]   | 1       | R/W  |                                            | The $V_{\text{STROVP}}$ voltage program range is 7V to 38V.                |

| D[2] | OVP[2]   | 1       | R/W  | V <sub>STR</sub> OVP Threshold Programming | $V_{\text{STROVP}} = \text{OVP}[4:0] \times 1\text{V} + 7\text{V}$         |

| D[1] | OVP[1]   | 0       | R/W  |                                            | Example:<br>if OVP[4:0] = 0x1D, then                                       |

| D[0] | OVP[0]   | 1       | R/W  |                                            | $V_{\text{STROVP}} = (1 \times 16^1 + 13 \times 16^0 + 7) \times 1 = 36V.$ |

## **REGISTER DESCRIPTION (continued)**

#### REG0x0C: ADC V<sub>IN</sub> Data Register Address (reset = 0x00)

| BITS | BIT NAME | DEFAULT | TYPE | DESCRIPTION | COMMENT                                                 |

|------|----------|---------|------|-------------|---------------------------------------------------------|

| D[7] | IN[7]    | 0       | R    | 1 = 8.192V  |                                                         |

| D[6] | IN[6]    | 0       | R    | 1 = 4.096V  |                                                         |

| D[5] | IN[5]    | 0       | R    | 1 = 2.048V  |                                                         |

| D[4] | IN[4]    | 0       | R    | 1 = 1.024V  | V <sub>IN</sub> ADC Results Reading                     |

| D[3] | IN[3]    | 0       | R    | 1 = 0.512V  | Range: 0 - 16.32V<br>8 bits (0 - 255) × 64mV resolution |

| D[2] | IN[2]    | 0       | R    | 1 = 0.256V  |                                                         |

| D[1] | IN[1]    | 0       | R    | 1 = 0.128V  |                                                         |

| D[0] | IN[0]    | 0       | R    | 1 = 0.064V  |                                                         |

### **REG0x0D: ADC V<sub>STR</sub> Data Register Address (reset = 0x00)**

| BITS | BIT NAME | DEFAULT | TYPE | DESCRIPTION | COMMENT                                                  |

|------|----------|---------|------|-------------|----------------------------------------------------------|

| D[7] | STR[7]   | 0       | R    | 1 = 19.2V   |                                                          |

| D[6] | STR[6]   | 0       | R    | 1 = 9.6V    |                                                          |

| D[5] | STR[5]   | 0       | R    | 1 = 4.8V    |                                                          |

| D[4] | STR[4]   | 0       | R    | 1 = 2.4V    | V <sub>STR</sub> ADC Results Reading                     |

| D[3] | STR[3]   | 0       | R    | 1 = 1.2V    | Range: 0 - 38.25V<br>8 bits (0 - 255) × 0.15V resolution |

| D[2] | STR[2]   | 0       | R    | 1 = 0.6V    |                                                          |

| D[1] | STR[1]   | 0       | R    | 1 = 0.3V    |                                                          |

| D[0] | STR[0]   | 0       | R    | 1 = 0.15V   |                                                          |

## REG0x0E: Interrupt (INT Pin Output Signal) Mask Control Register Address (reset = 0x00)

| BITS | BIT NAME | DEFAULT | TYPE | DESCRIPTION                                                                          | COMMENT                                        |

|------|----------|---------|------|--------------------------------------------------------------------------------------|------------------------------------------------|

| All  |          | 0       | R/W  | 0 = event can assert interrupt<br>1 = event cannot interrupt but its flag bit is set |                                                |

| D[7] | MASK[7]  | 0       | R/W  | Mask V <sub>IN</sub> OVP Interrupt                                                   | If $V_{IN}$ OVP function is enabled in LSP[7]. |

| D[6] | MASK[6]  | 0       | R/W  | Mask Input OCP Interrupt                                                             |                                                |

| D[5] | MASK[5]  | 0       | R/W  | Mask C <sub>STR</sub> SCP Interrupt                                                  |                                                |

| D[4] | MASK[4]  | 0       | R/W  | Mask Reverse Blocking Protection Interrupt                                           | If the RB protection is enabled in SF[6].      |

| D[3] | MASK[3]  | 0       | R/W  | Mask C <sub>STR</sub> Measurement Complete Interrupt                                 | Measuring starts if SF[5] rises from 0 to 1.   |

| D[2] | MASK[2]  | 0       | R/W  | Mask ADC Complete Interrupt                                                          | ADC starts when SYS[7] rises from 0 to 1.      |

| D[1] | MASK[1]  | 0       | R/W  | Mask High Junction Temperature Warning Interrupt                                     |                                                |

| D[0] | MASK[0]  | 0       | R/W  | Mask Thermal Shutdown Interrupt                                                      |                                                |

# **REGISTER DESCRIPTION (continued)**

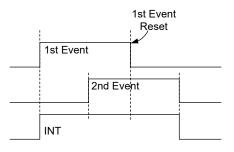

## **REG0x0F:** Interrupt Flag Register Address (reset = 0x00)

| BITS | BIT NAME | DEFAULT | TYPE | DESCRIPTION                                                                                                                            | COMMENT                                        |

|------|----------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| All  |          | 0       | R/WC | 0 = event has not occurred<br>1 = event has occurred<br>To reset flag and interrupt, write 1 to the bit after<br>the event is cleared. |                                                |

| D[7] | FLAG[7]  | 0       | R/WC | V <sub>IN</sub> OVP Event Flag Bit (V <sub>IN</sub> OVP exceeded)                                                                      | If $V_{IN}$ OVP function is enabled in LSP[7]. |

| D[6] | FLAG[6]  | 0       | R/WC | Input OCP Event Flag Bit (Input current limit exceeded)                                                                                |                                                |

| D[5] | FLAG[5]  | 0       | R/WC | $C_{\text{STR}}$ SCP Event Flag Bit (V_{\text{STR}} fell below the short-circuit threshold)                                            |                                                |

| D[4] | FLAG[4]  | 0       | R/WC | Reverse Blocking Protection Event Flag Bit (BUS to IN current passed the reverse current threshold).                                   | If the RB protection is enabled in SF[6].      |

| D[3] | FLAG[3]  | 0       | R/WC | C <sub>STR</sub> Measurement Complete Event Flag Bit                                                                                   | Measuring starts if SF[5] rises from 0 to 1.   |

| D[2] | FLAG[2]  | 0       | R/WC | ADC Conversion Complete Event Flag Bit                                                                                                 | ADC starts if SYS[7] rises from 0 to 1.        |

| D[1] | FLAG[1]  | 0       | R/WC | High Junction Temperature Warning Event Flag Bit $(T_J > +125^{\circ}C)$                                                               |                                                |

| D[0] | FLAG[0]  | 0       | R/WC | Thermal Shutdown Event Flag Bit (T $_{J}$ > +150°C)                                                                                    |                                                |

#### **REG0x10:** System Control Register Address (reset = 0x02)

| BITS | BIT NAME | DEFAULT | TYPE | DESCRIPTION                                                                                                                                                                                                                                                       | COMMENT                                 |

|------|----------|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| D[7] | SYS[7]   | 0       | R/W  | ADC Conversion Enable<br>Default: 0                                                                                                                                                                                                                               | ADC starts if SYS[7] rises from 0 to 1. |

| D[6] | SYS[6]   | 0       | R    | Reserved                                                                                                                                                                                                                                                          |                                         |

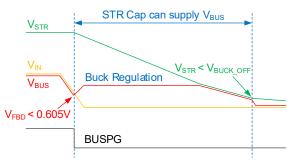

| D[5] | SYS[5]   | 0       | R/W  | Converter Mode After V <sub>IN</sub> Recovery<br>0 = Run and continue in Buck mode until V <sub>STR</sub> goes below V <sub>BUCK_OFF</sub> .<br>1 = Exit Buck mode and charge C <sub>BUS</sub> from V <sub>IN</sub> (if already in Buck mode)                     |                                         |

| D[4] | SYS[4]   | 0       | R/W  | After Detecting Thermal Shutdown<br>0 = Force to Buck mode<br>1 = Turn off all circuits immediately                                                                                                                                                               |                                         |