# SGM8433-2XTHQ12G Low-Distortion, Dual-Power Operational Amplifier with Integrated Protection for Resolver Drive

#### **GENERAL DESCRIPTION**

The SGM8433-2XTHQ12G is a dual-power, high performance operational amplifier with integrated protection, which is specifically designed for applications involving resolvers. The device features high gain-bandwidth product and high slew rate. It also offers a continuous high output current drive. These characteristics make the device highly suitable for providing the requisite low-distortion, high-level differential excitation essential for activating the primary coil of a resolver. The device integrates over-temperature and current-limit protection to improve the robustness of overall system, particularly in scenarios where analog signals are transmitted through wires that may be vulnerable to errors.

The SGM8433-2XTHQ12G fits in a small package and features low thermal resistance, which permit the transfer of high currents to loads while saving space on the circuit board. The SGM8433-2XTHQ12G's enhanced gain-bandwidth feature enables its use as a filter component, while driving high output current. This advantage allows for a more compact design in the resolver drive signal chain by minimizing the overall footprint required. The compact design of the device stands out as a significant benefit for its integration into industrial systems.

The SGM8433-2XTHQ12G is available in a Green TDFN-3×3-12BL package. It is specified over the extended industrial temperature range (-40  $^{\circ}$ C to +125 $^{\circ}$ C).

#### **FEATURES**

- Wide Supply Voltage Range: 4.5V to 24V

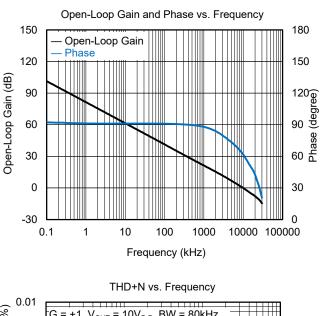

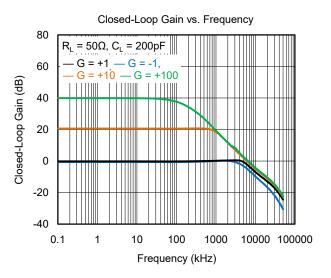

- Gain-Bandwidth Product: 12MHz

- Slew Rate: 35V/µs

- Functional-Safety Feature

- Over-Temperature Protection

- Current-Limit Protection

- Shutdown Mode for Applications with Low IQ

- -40°C to +125°C Operating Temperature Range

- Available in a Green TDFN-3×3-12BL Package

#### **APPLICATIONS**

Exciting Signal Driver of Resolver Primary Coil Motor Control System Servo Control System

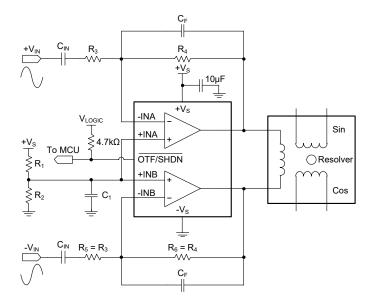

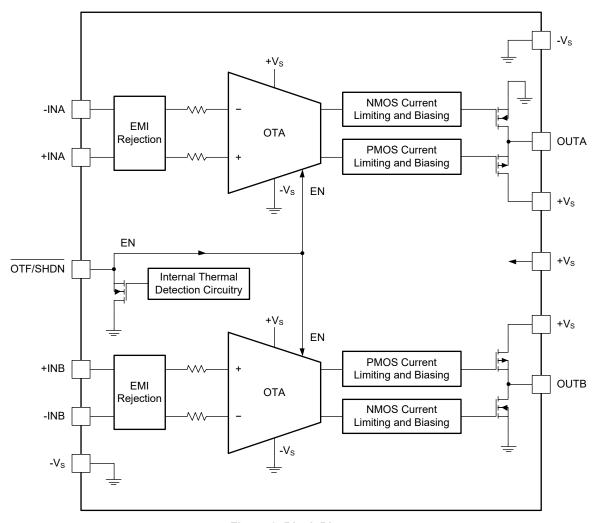

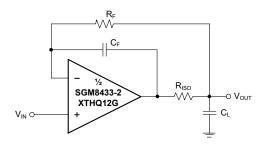

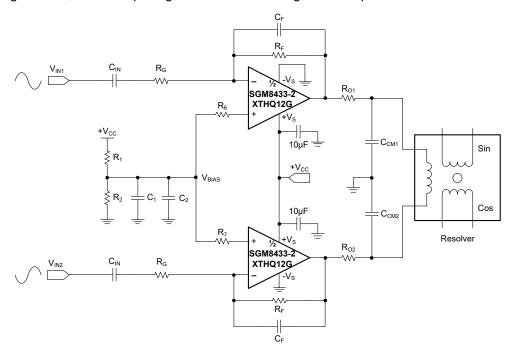

#### SIMPLIFIED SCHEMATIC

Figure 1. Simplified Schematic for Differential Input

#### PACKAGE/ORDERING INFORMATION

| MODEL            | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER  | PACKAGE<br>MARKING     | PACKING<br>OPTION   |

|------------------|------------------------|-----------------------------------|---------------------|------------------------|---------------------|

| SGM8433-2XTHQ12G | TDFN-3×3-12BL          | -40°C to +125°C                   | SGM8433-2XTHQ12G/TR | SGM<br>1C2THQ<br>XXXXX | Tape and Reel, 4000 |

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### **ABSOLUTE MAXIMUM RATINGS**

| ADOCEO I E INIAMINIONI I           | CAT III OO                                     |

|------------------------------------|------------------------------------------------|

| Supply Voltage, V <sub>S</sub>     |                                                |

| Single Supply                      | 26V                                            |

| Dual Supply                        | ±13V                                           |

| Signal Input Voltage Terminals     |                                                |

| Common Mode                        | $(-V_S)$ - 0.5V to $(+V_S)$ + 0.7V             |

| Differential                       | (+V <sub>S</sub> ) - (-V <sub>S</sub> ) + 0.2V |

| OTF/SHDN Pin Voltage Range, V      | VOTF/SHDN                                      |

| Common Mode                        |                                                |

| Output Short-Circuit Current (1)   | Continuous                                     |

| Package Thermal Resistance         |                                                |

| TDFN-3×3-12BL, θ <sub>JA</sub>     | 37.7°C/W                                       |

| TDFN-3×3-12BL, θ <sub>JB</sub>     | 17.4°C/W                                       |

| TDFN-3×3-12BL, $\theta_{JC (TOP)}$ | 40.3°C/W                                       |

| TDFN-3×3-12BL, $\theta_{JC (BOT)}$ | 5°C/W                                          |

| Junction Temperature               | +150°C                                         |

| Storage Temperature Range          | 65°C to +150°C                                 |

| Lead Temperature (Soldering, 10    | s)+260°C                                       |

| ESD Susceptibility (2)(3)          |                                                |

| HBM                                | ±8000V                                         |

| CDM                                | ±1000V                                         |

|                                    |                                                |

#### NOTES:

- 1. Each package contains one amplifier, which can be shorted to ground.

- 2. For human body model (HBM), all pins comply with ANSI/ESDA/JEDEC JS-001 specifications.

- 3. For charged device model (CDM), all pins comply with ANSI/ESDA/JEDEC JS-002 specifications.

#### RECOMMENDED OPERATING CONDITIONS

| Supply Voltage Range, V <sub>S</sub> |                |

|--------------------------------------|----------------|

| Single Supply                        | 4.5V to 24V    |

| Dual Supply                          | ±2.25V to ±12V |

| Operating Temperature Range          | 40°C to +125°C |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

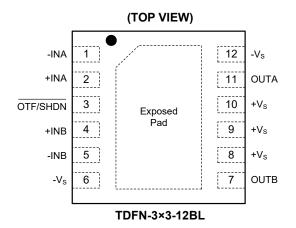

## **PIN CONFIGURATION**

## **PIN DESCRIPTION**

| PIN         | NAME                             | I/O | FUNCTION                                                                                                                                                                                                                                                                  |

|-------------|----------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | -INA                             | 1   | Inverting Input of Amplifier A.                                                                                                                                                                                                                                           |

| 2           | +INA                             | 1   | Non-Inverting Input of Amplifier A.                                                                                                                                                                                                                                       |

| 3           | 3                                |     | Over-Temperature Flag and Shutdown. When the $\overline{OTF/SHDN}$ pin is high (> $V_{IH\_OTF}$ ), the operational amplifier is operating. When the $\overline{OTF/SHDN}$ pin is low (< $V_{IL\_OTF}$ ), the operational amplifier is in shutdown mode (low $I_Q$ state). |

| 4           |                                  |     | Non-Inverting Input of Amplifier B.                                                                                                                                                                                                                                       |

| 5           | -INB                             | I   | Inverting Input of Amplifier B.                                                                                                                                                                                                                                           |

| 6, 12       | 6, 12 -V <sub>S</sub> — 7 OUTB O |     | Negative Supply. The dual negative supply points must be used and interconnected on the circuit board.                                                                                                                                                                    |

| 7           |                                  |     | Output of Amplifier B.                                                                                                                                                                                                                                                    |

| 8, 9, 10    | +V <sub>S</sub>                  |     | Positive Supply.                                                                                                                                                                                                                                                          |

| 11          | OUTA                             | 0   | Output of Amplifier A.                                                                                                                                                                                                                                                    |

| Exposed Pad | Exposed<br>Pad                   | _   | The exposed pad can be connected to $-V_S$ or left floating. Connect it to $-V_S$ plane to maximize thermal performance. Ensure that the exposed pad is exclusively connected to the $-V_S$ pin and not to any other pins.                                                |

## **ELECTRICAL CHARACTERISTICS**

$(V_S = 4.5 \text{V to } 24 \text{V}, V_{CM} = V_{OUT} = V_S/2, \text{ and } R_L = 10 \text{k}\Omega \text{ connected to } V_S/2, \text{ Full } = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C}, \text{ typical values are at } T_A = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.})$

| PARA                                     | AMETER             | SYMBOL               | CONDITIONS                                                                   | TEMP          | MIN                      | TYP      | MAX                      | UNITS    |  |

|------------------------------------------|--------------------|----------------------|------------------------------------------------------------------------------|---------------|--------------------------|----------|--------------------------|----------|--|

| Input Characte                           | eristics           |                      |                                                                              |               |                          |          |                          |          |  |

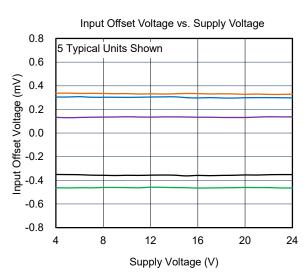

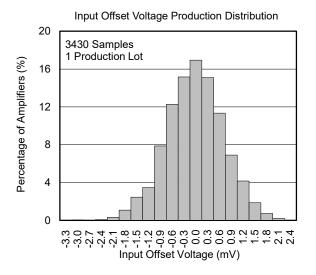

| Innert Offerst Val                       | 4                  |                      |                                                                              | +25°C         |                          | ±1       | ±7                       | m\/      |  |

| Input Offset Vol                         | tage               | V <sub>os</sub>      |                                                                              | Full          |                          |          | ±8                       | mV       |  |

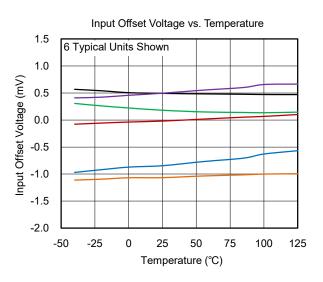

| Input Offset Vol                         | tage Drift         | ΔV <sub>OS</sub> /ΔΤ |                                                                              | Full          |                          | ±5       | ±20 <sup>(1)</sup>       | μV/°C    |  |

| Input Rice Curre                         | ant                | I <sub>B</sub>       |                                                                              | +25°C         |                          | ±20      | ±300                     | pА       |  |

| Input bias Curre                         | Input Bias Current |                      |                                                                              | Full          |                          |          | ±15                      | nA       |  |

| Input Offset Cui                         | rrent              | los                  |                                                                              | +25°C         |                          | ±20      | ±300                     | pА       |  |

| input Onset Out                          |                    | 105                  |                                                                              | Full          |                          |          | ±5                       | nA       |  |

| Input Common N                           | Mode Voltage Range | V <sub>CM</sub>      |                                                                              | +25°C         | (-V <sub>S</sub> ) - 0.2 |          | (+V <sub>S</sub> ) + 0.2 | V        |  |

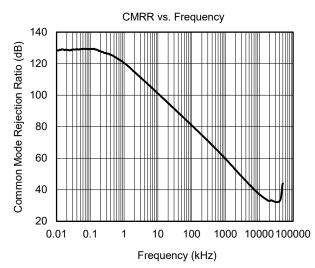

|                                          |                    |                      | $V_S = 4.5V$ , $V_{CM} = (-V_S) - 0.2V$ to $(+V_S) + 0.2V$                   | +25°C         | 71                       | 90       |                          |          |  |

|                                          |                    |                      | 13 (13) 0 (13) 0                                                             | Full          | 68                       |          |                          |          |  |

|                                          |                    |                      | $V_S = 4.5V$ , $V_{CM} = (-V_S) + 2.5V$ to $(+V_S) + 0.2V$                   | +25°C         | 89                       | 112      |                          |          |  |

| Common Mode                              | Rejection Ratio    | CMRR                 | 3 2 7 3 11 ( 3 7 2 ( 3 7 2                                                   | Full          | 86                       |          |                          | dB       |  |

|                                          | ,                  |                      | $V_S = 24V$ , $V_{CM} = (-V_S) - 0.2V$ to $(+V_S) + 0.2V$                    | +25°C         | 84                       | 102      |                          | -        |  |

|                                          |                    |                      |                                                                              | Full          | 81                       |          |                          |          |  |

| Differential                             |                    | _                    | $V_S = 24V$ , $V_{CM} = (-V_S) + 2.5V$ to $(+V_S) + 0.2V$                    | +25°C         | 109                      | 126      |                          | -        |  |

|                                          |                    |                      |                                                                              | Full          | 104                      |          |                          |          |  |

| Input Differential Impedance Common Mode | Z <sub>ID</sub>    |                      | +25°C                                                                        |               | 20    0.8                |          | MΩ    pF                 |          |  |

| impedance                                | Common Mode        | Z <sub>IC</sub>      |                                                                              | +25°C         |                          | 0.5    8 |                          | GΩ    pF |  |

|                                          |                    |                      | $V_S = 4.5V, (-V_S) + 0.5V < V_{OUT} < (+V_S) - 0.5V$                        | +25°C         | 94                       | 120      |                          | dB       |  |

|                                          |                    |                      | $V_S = 4.5V$ , $(-V_S) + 1.5V < V_{OUT} < (+V_S) - 1.5V$ , $R_L = 225\Omega$ | Full          | 90                       |          |                          |          |  |

|                                          |                    |                      |                                                                              | +25°C         | 86                       | 110      |                          |          |  |

| Open-Loop Volt                           | tage Gain          | A <sub>OL</sub>      |                                                                              | Full          | 83                       |          |                          |          |  |

|                                          |                    |                      | $V_S = 24V$ , $(-V_S) + 0.5V < V_{OUT} < (+V_S) - 0.5V$                      | +25°C         | 109                      | 134      |                          |          |  |

|                                          |                    |                      |                                                                              | Full          | 106                      |          |                          |          |  |

|                                          |                    |                      | $V_S = 24V$ , $(-V_S) + 1.5V < V_{OUT} < (+V_S) - 1.5V$ ,                    | +25°C<br>Full | 107                      | 128      |                          |          |  |

|                                          |                    |                      | $R_L = 225\Omega$                                                            |               | 103                      |          |                          |          |  |

| Output Charac                            | teristics          | Π                    | I                                                                            |               | I                        |          | 1 00                     |          |  |

| Output Voltage                           | Swing from Rail    |                      | I <sub>OUT</sub> = ±5mA                                                      | +25°C         |                          | 20       | 30                       | mV       |  |

|                                          |                    |                      | 0.1.                                                                         | Full          | 000                      | 400      | 35                       |          |  |

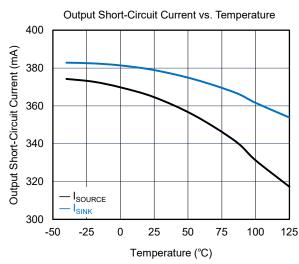

| Output Short-Ci                          | ircuit Current     | I <sub>sc</sub>      | Sinking                                                                      | +25°C         | 280                      | 400      | 510                      | mA       |  |

|                                          |                    |                      | Sourcing                                                                     | +25°C         | 230                      | 360      | 500                      |          |  |

| Power Supply                             | as Donas           |                      |                                                                              | F             | 4.5                      |          | 04                       | \/       |  |

| Operating Volta                          | ge Kange           | Vs                   |                                                                              | Full<br>+25°C | 4.5                      | 100      | 24                       | V        |  |

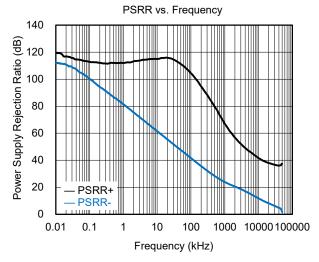

| Power Supply F                           | Rejection Ratio    | PSRR                 | V <sub>S</sub> = ±2.25V to ±12V                                              |               | 104                      | 126      |                          | dB       |  |

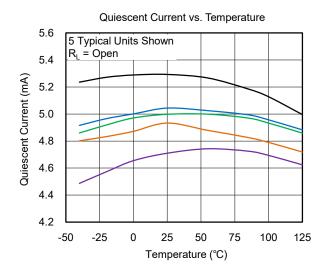

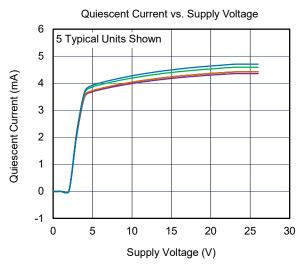

| Total Ouisseent                          | Current            | 1                    | I <sub>OUT</sub> = 0A                                                        | Full<br>Full  | 100                      | 5        | 7.5                      | mA       |  |

| Total Quiescent Current                  |                    | ΙQ                   | 1001 - 07                                                                    | i uli         |                          | J        | 1.5                      | 11174    |  |

NOTE: 1. This is guaranteed by design and tested by limited samples, and is not covered by manufacture testing.

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_S = 4.5 \text{V to } 24 \text{V}, V_{CM} = V_{OUT} = V_S/2, \text{ and } R_L = 10 \text{k}\Omega \text{ connected to } V_S/2, \text{ Full } = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C}, \text{ typical values are at } T_A = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.})$

| PARAMETER                         | SYMBOL                | CONDITIONS                                                                          | TEMP  | MIN | TYP | MAX | UNITS             |  |

|-----------------------------------|-----------------------|-------------------------------------------------------------------------------------|-------|-----|-----|-----|-------------------|--|

| Dynamic Performance               | •                     |                                                                                     | •     |     |     | •   | •                 |  |

| Gain-Bandwidth Product            | GBP                   |                                                                                     | +25°C |     | 12  |     | MHz               |  |

| Olani Bata                        | 0.0                   | V <sub>S</sub> = 4.5V, 4V step, G = +1                                              | +25°C |     | 20  |     | ) //:             |  |

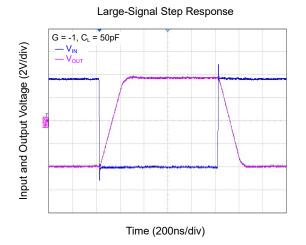

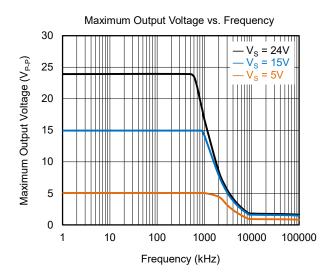

| Slew Rate                         | SR                    | V <sub>S</sub> = 24V, 10V step, G = +1                                              | +25°C |     | 35  |     | V/µs              |  |

| Cattling Times to 0.40/           | 4                     | V <sub>S</sub> = 24V, 10V step, G = +1, C <sub>L</sub> = 10pF                       | +25°C |     | 0.6 |     | μs                |  |

| Settling Time to 0.1%             | t <sub>S</sub>        | V <sub>S</sub> = 24V, 10V step, G = -1, C <sub>L</sub> = 10pF                       | +25°C |     | 0.6 |     |                   |  |

| Overload Recovery Time            | ORT                   | V <sub>IN</sub> × G > V <sub>S</sub>                                                | +25°C |     | 0.1 |     | μs                |  |

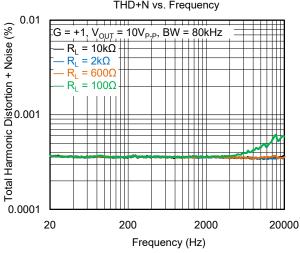

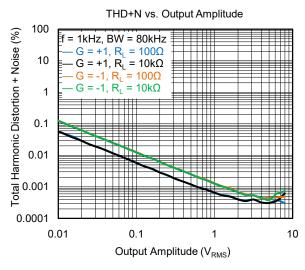

| Total Harmonic Distortion + Noise | THD+N                 | $V_S = 15V$ , $V_{OUT} = 10V_{P-P}$ ,<br>$G = -1$ , $f = 10kHz$ , $R_L = 100\Omega$ | +25°C |     | 100 |     | dB                |  |

| Channel Separation                |                       | f = 10kHz                                                                           | +25°C |     | 110 |     | dB                |  |

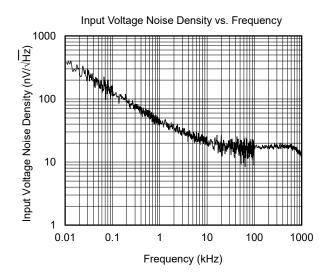

| Noise                             |                       |                                                                                     |       |     |     |     |                   |  |

| Input Voltage Noise               |                       | f = 0.1Hz to 10Hz                                                                   | +25°C |     | 5   |     | μV <sub>RMS</sub> |  |

| Input Voltage Noise Density       | e <sub>n</sub>        | f = 1kHz                                                                            | +25°C |     | 60  |     | nV/√Hz            |  |

|                                   |                       | f = 100kHz                                                                          | +25°C |     | 20  |     | ⊓V/√HZ            |  |

| Input Current Noise Density       | in                    | f = 1kHz                                                                            | +25°C |     | 4   |     | fA/√Hz            |  |

| Enable                            |                       |                                                                                     |       |     |     |     |                   |  |

| Enable High Input Voltage         | $V_{IH\_OTF}$         |                                                                                     | +25°C | 1.2 |     |     | V                 |  |

| Enable Low Input Voltage          | $V_{IL\_OTF}$         |                                                                                     | +25°C |     |     | 0.5 | V                 |  |

| Frankla I biotamasia              |                       | V <sub>S</sub> = 4.5V                                                               | +25°C |     | 120 |     | >/                |  |

| Enable Hysteresis                 |                       | V <sub>S</sub> = 24V                                                                | +25°C |     | 180 |     | mV                |  |

| Enable Start-Up Time              | t <sub>OTF/SHDN</sub> |                                                                                     | +25°C |     | 3   |     | μs                |  |

| Shutdown Current                  | I <sub>SD</sub>       | V <sub>OTF/SHDN</sub> = 0V                                                          | +25°C |     | 50  | 80  | μA                |  |

| Thermal Protection                |                       |                                                                                     |       |     | •   |     | •                 |  |

| Thermal Shutdown                  |                       |                                                                                     |       |     | 170 |     | °C                |  |

| Thermal Shutdown Recovery         |                       |                                                                                     |       |     | 150 |     | °C                |  |

#### TYPICAL PERFORMANCE CHARACTERISTICS

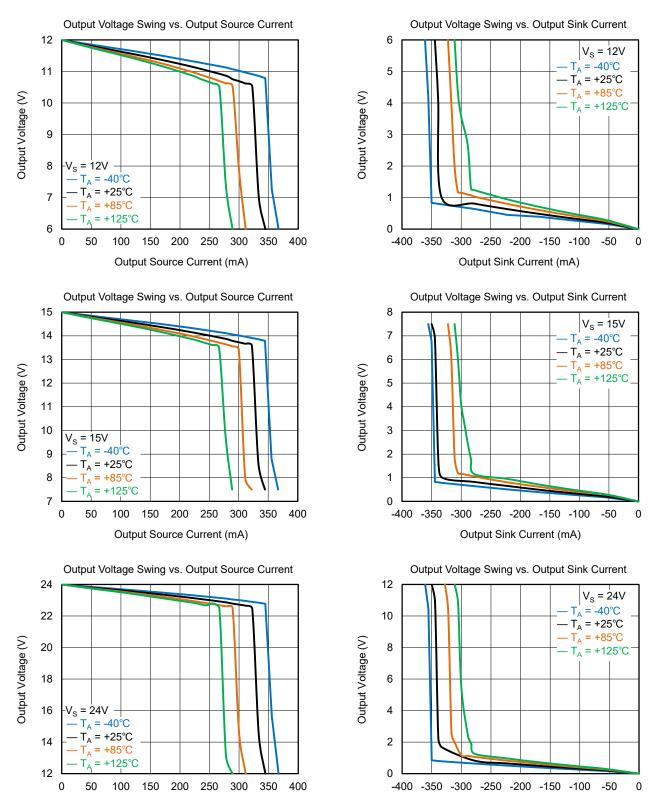

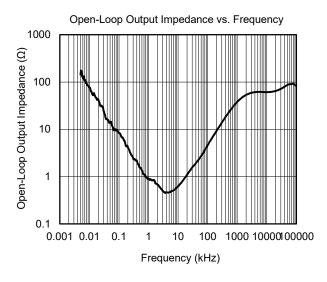

At  $T_A$  = +25°C,  $V_S$  = 24V,  $V_{CM}$  =  $V_S/2$  and  $R_L$  = 10k $\Omega$ , unless otherwise noted.

Output Source Current (mA)

Output Sink Current (mA)

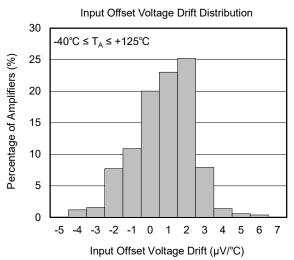

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. Block Diagram

#### **DETAILED DESCRIPTION**

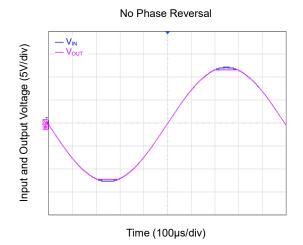

The SGM8433-2XTHQ12G is a high performance operational amplifier that supports dual-power supply, rail-to-rail input and output, and has high output current drive capability. The device also comes with shutdown control, over-temperature and current-limit protection functions, which is specifically designed for applications involving resolvers.

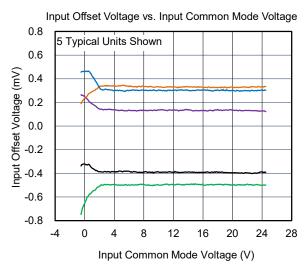

#### **Input and Output Range**

The SGM8433-2XTHQ12G supports rail-to-rail input and output. The input common mode range is from  $(\text{-V}_S)$  - 0.2V to  $(\text{+V}_S)$  + 0.2V. To achieve normal output performance in application, it is necessary to ensure that the input signal does not exceed this specification. If the input signal exceeds the limit, it can cause distortion and nonlinearities; in severe cases, it can lead to the device damage.

The SGM8433-2XTHQ12G has high current output capability and low output voltage swing from rail. The typical output voltage swing from rail is 20mV under the condition of ±5mA output current. This makes the SGM8433-2XTHQ12G suitable for applications that require low output voltage swing from rail.

#### **Over-Temperature and Shutdown Function**

The SGM8433-2XTHQ12G is designed with overtemperature protection and a shutdown control  $(\overline{\text{OTF/SHDN}})$  pin. This pin is a dual function pin. When the  $\overline{\text{OTF/SHDN}}$  pin is pulled low, the device enters shutdown mode, and the device's quiescent current is as low as  $50\mu\text{A}$  (typical value at +25°C). In shutdown mode, all output pins of the operational amplifier maintain a high-impedance state. When the  $\overline{\text{OTF/SHDN}}$  pin is pulled high, the device is enabled, and the operational amplifier can operate normally.

The SGM8433-2XTHQ12G defaults to shutdown mode when the  $\overline{OTF/SHDN}$  pin is floating, if users want to enable the device, the  $\overline{OTF/SHDN}$  pin must be pulled high through an external pull-up resistor. Table 1 summarizes the control logic of the  $\overline{OTF/SHDN}$  pin. In addition, it should be noted that the absolute maximum rating for the  $\overline{OTF/SHDN}$  pin is 5.5V relative to -V<sub>S</sub> pin, so users should exercise caution when operating it.

Table 1. OTF/SHDN Shutdown Control

| OTF/SHDN Pin                   | SGM8433-2XTHQ12G State |

|--------------------------------|------------------------|

| High ( > V <sub>IH_OTF</sub> ) | Enabled and Operating  |

| Low ( < V <sub>IL_OTF</sub> )  | Shutdown Mode          |

The OTF/SHDN pin's another function is used to indicate over-temperature protection events. This pin defaults to being pulled high. When the over-temperature event occurs and the junction temperature of SGM8433-2XTHQ12G exceeds the limit value, the OTF/SHDN pin will actively become low and all outputs of the operational amplifier will enter a high-impedance state.

#### **Thermal Shutdown**

The SGM8433-2XTHQ12G design has a thermal shutdown (TSD) function. The device enters a shutdown state when the internal junction temperature exceeds the shutdown threshold of +170°C. In thermal shutdown mode, the output current is cut off, and the output pin remains in a high-impedance state. The device has a thermal shutdown hysteresis temperature of 20°C. It will automatically recover from TSD mode once the junction temperature drops to +150°C. In application, the SGM8433-2XTHQ12G should be operated at a junction temperature below +150°C, and the exposed pad should be connected to a larger ground plane to maximize thermal performance.

#### **Current-Limit**

The SGM8433-2XTHQ12G design has an output current-limit function that activates when overload events happen. The output source and sink current limits are 360mA (TYP) and 400mA (TYP), respectively. In application, the die temperature rises rapidly if the SGM8433-2XTHQ12G remains in current limitation for an extended period. This situation may cause the chip to enter thermal shutdown. Therefore, it is necessary for users to evaluate whether the device's output current can meet the normal operating requirements when designing circuits. It should be noted not to operate the equipment continuously under thermal hysteresis for a long time, as this behavior may cause irreversible damage to the device.

## **DETAILED DESCRIPTION (continued)**

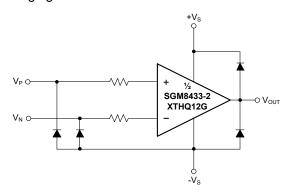

#### **Input and Output Protection**

The SGM8433-2XTHQ12G incorporates internal ESD protection circuits on both input and output pins, and equivalent input and output circuit is illustrated in the following figure.

Figure 3. Equivalent Input and Output Circuit

For input and output pins, this protection primarily consists of current-steering diodes connected between the input and power supply pins. Therefore, it is crucial to keep the input voltage below the maximum rating and limit the input current to less than 10mA.

In addition, the SGM8433-2XTHQ12G supports large differential voltage inputs within the power supply range, making it suitable for use as a comparator in some applications.

#### **Capacitive Load and Stability**

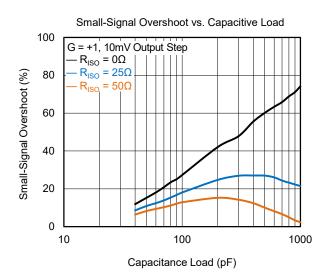

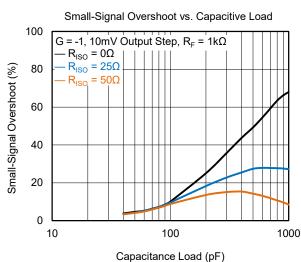

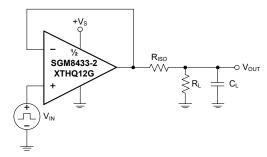

The SGM8433-2XTHQ12G is designed for driving the 100pF capacitive load with unity-gain stable. If greater capacitive load must be driven in application, the circuit in Figure 4 can be used. In this circuit, the IR drop voltage generated by  $R_{\rm ISO}$  is compensated by feedback loop.

Figure 4. Circuit to Drive Heavy Capacitive Load

For the buffer circuit, another simpler compensation is shown in Figure 5. This method, called out-of-the-loop compensation, primarily uses a resistor to isolate the output pin and feedback network from the capacitive load. Functionally, it introduces a zero in the transfer function of the feedback network, which reduces the loop phase shift at higher frequencies. This method is effective, but the  $R_{\rm ISO}$  will bring an IR drop voltage, so choosing an appropriate resistance value is crucial in actual applications. The selection of  $R_{\rm ISO}$  can refer to the Small-Signal Overshoot vs. Capacitive Load.

Figure 5. Circuit to Drive Capacitive Load

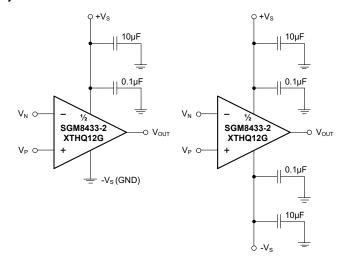

#### **Power Supply Bypassing and Layout**

Power supply pins are actually inputs to the amplifiers. Care must be taken to provide the amplifiers with a clean, low noise DC voltage source. Power supply bypassing is employed to provide a low-impedance path to ground for noise and undesired signals at all frequencies. This cannot be achieved with a single capacitor type; however, with a variety of capacitors in parallel, the bandwidth of power supply bypassing can be greatly extended. The bypass capacitors have two functions:

- Provide a low-impedance path for noise and undesired signals from the supply pins to ground.

- Provide local stored charge for fast switching conditions and minimize the voltage drop at the supply pins during transients. This is typically achieved with large electrolytic capacitors.

# **DETAILED DESCRIPTION (continued)**

Good quality ceramic chip capacitors should be used and always kept as close as possible to the amplifier package. A parallel combination of a  $0.1\mu F$  ceramic and a  $10\mu F$  electrolytic capacitor covers a wide range of rejection for unwanted noise. The  $10\mu F$  capacitor is less critical for high-frequency bypassing, and in most cases, one per supply line is sufficient. The values of capacitors are circuit-dependent and should be determined by the system's requirements.

Figure 6. Amplifier with Bypass Capacitors

#### APPLICATION INFORMATION

The SGM8433-2XTHQ12G is a dual CMOS operational amplifier featuring rail-to-rail output, high voltage and high output drive. It operates within a wide voltage range of 4.5V to 24V, offers a high continuous output current of 230mA (MIN), and is available in a TDFN-3×3-12BL package that provides efficient heat dissipation. These characteristics make the device highly suitable for applications requiring both high operating voltage and high output current.

The SGM8433-2XTHQ12G has output current limit and thermal shutdown (TSD) functions. It can be flexibly applied to a resolver excitation circuit. The following chapter provides more detailed descriptions.

#### **Resolver Excitation Circuit**

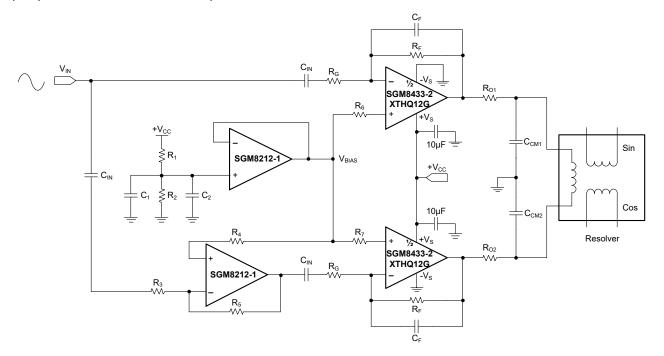

The SGM8433-2XTHQ12G's high continuous output current function makes it very suitable for resolver excitation circuit. Figure 7 shows the typical resolver excitation circuit using the SGM8433-2XTHQ12G and the SGM8212-1. This circuit includes two SGM8212-1s: one is used to provide a bias voltage buffer and the other is used as an inverting amplifier to obtain a signal with phase reversal.

Figure 7. Resolver Excitation Circuit with SGM8212-1

## **APPLICATION INFORMATION (continued)**

Figure 8 shows a simplified resolver excitation circuit without SGM8212-1. Its bias voltage is provided by a resistance voltage divider, and the input signal is a differential signal with a phase difference of 180 degrees.

Figure 8. Simplified Resolver Excitation Circuit without SGM8212-1

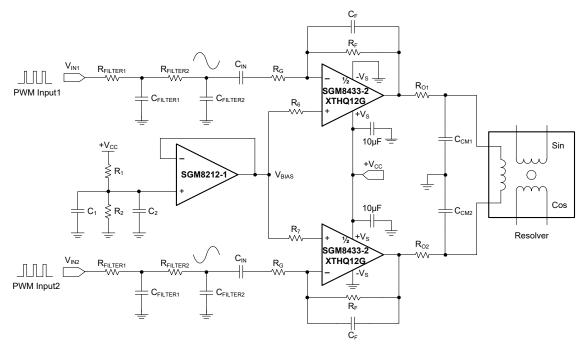

Figure 9 shows a resolver excitation circuit with a pulse-width modulation (PWM) signal as the input. In this circuit, the SGM8212-1 is used as a buffer and provides the bias voltage. Two input PWM signals from the I/O pins of the microcontroller are filtered by a two-stage RC filter circuit and converted to a sine wave signal for use as an excitation input.

Figure 9. Resolver Excitation Circuit from PWM Input Signal

## **APPLICATION INFORMATION (continued)**

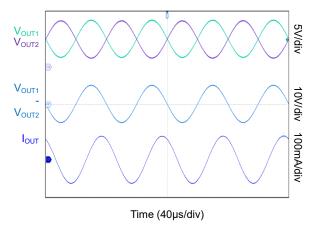

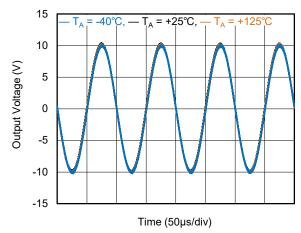

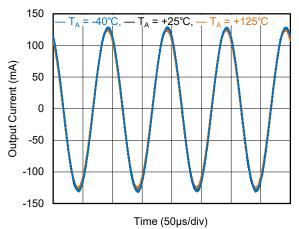

Figure 10 shows the actual output waveform from a resolver excitation circuit, and the key circuit parameter design is shown in Table 2.

Figure 10. Actual Output Waveform from Resolver Excitation Circuit (+ $V_S$  = 15 $V_T$ , - $V_S$  = 0 $V_T$ , f = 10 $V_T$ )

**Table 2. Design Parameters**

| Design Parameter                                | Example Value           |

|-------------------------------------------------|-------------------------|

| Ambient Temperature Range                       | -40°C to +125°C         |

| Supply Voltage                                  | +15V                    |

| V <sub>BIAS</sub>                               | +7.5V from<br>SGM8212-1 |

| Ro                                              | Ω0                      |

| C <sub>CM</sub>                                 | No Connect              |

| Gain                                            | 2.5V/V                  |

| Input Signal Frequency                          | 10kHz                   |

| Resolver Excitation Input Voltage               | 8V <sub>P-P</sub>       |

| Resolver Excitation Output Voltage              | 20V <sub>P-P</sub>      |

| Output Current with Resolver Equivalent Circuit | ±130mA <sub>P-P</sub>   |

Figure 11 and Figure 12 respectively show the output voltage and the output current of the resolver excitation circuit.

Figure 11. Output Voltage of Resolver Excitation Circuit

Figure 12. Output Current of Resolver Excitation Circuit

## **SGM8433-2XTHQ12G**

# Low-Distortion, Dual-Power Amplifier with Integrated Protection for Resolver Drive

## **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

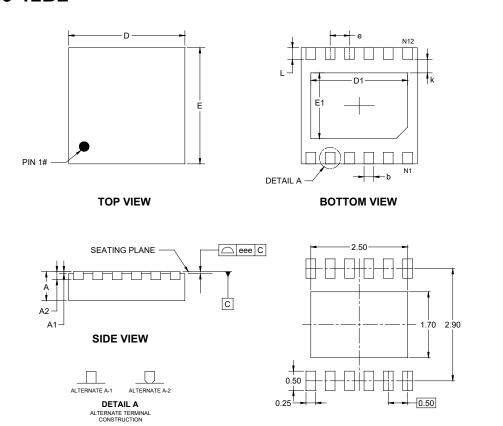

# PACKAGE OUTLINE DIMENSIONS TDFN-3×3-12BL

| Symbol | Dimensions In Millimeters |           |       |  |  |  |  |

|--------|---------------------------|-----------|-------|--|--|--|--|

| Symbol | MIN                       | NOM       | MAX   |  |  |  |  |

| Α      | 0.700                     | -         | 0.800 |  |  |  |  |

| A1     | 0.000                     | -         | 0.050 |  |  |  |  |

| A2     |                           | 0.203 REF |       |  |  |  |  |

| D      | 2.900                     | 3.100     |       |  |  |  |  |

| Е      | 2.900 -                   |           | 3.100 |  |  |  |  |

| D1     | 2.400                     | 2.600     |       |  |  |  |  |

| E1     | 1.600                     | 1.600 -   |       |  |  |  |  |

| b      | 0.200                     | 0.200 -   |       |  |  |  |  |

| L      | 0.200                     | 0.200 -   |       |  |  |  |  |

| k      | 0.350 REF                 |           |       |  |  |  |  |

0.500 BSC 0.080

RECOMMENDED LAND PATTERN (Unit: mm)

NOTE: This drawing is subject to change without notice.

eee

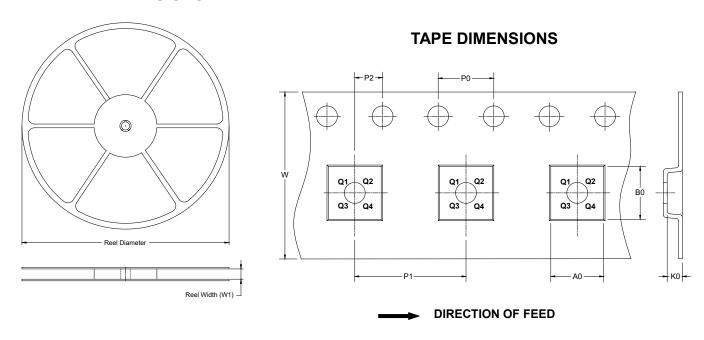

## TAPE AND REEL INFORMATION

#### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type  | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| TDFN-3×3-12BL | 13"              | 12.4                     | 3.35       | 3.35       | 1.13       | 4.0        | 8.0        | 2.0        | 12.0      | Q2               |

### **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

## **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |        |

|-----------|----------------|---------------|----------------|--------------|--------|

| 13″       | 386            | 280           | 370            | 5            | DD0002 |