### **GENERAL DESCRIPTION**

The SGM6030 is an efficient and miniature synchronous Buck converter with I<sup>2</sup>C/VSEL interface. The device implements auto PFM mode operation to maximize the efficiency at light load condition. At moderate to heavy load, the device automatically switches to continuous conduction mode (CCM) operation. Forced PWM operation is also available for better output ripple performance and stable switching frequency. COT-control architecture is implemented to incorporate the benefits of fast load and line transient responses and low output voltage ripple, which is beneficial for RF and noise sensitive applications.

The SGM6030 family offers VSEL option for dynamic voltage scaling (DVS) via the  $I^2C$  interface, which can adjust the output voltage rapidly to adapt for any changes on the load side.

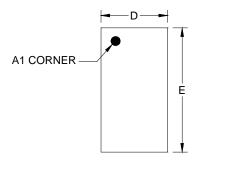

The SGM6030 is available in a Green WLCSP-0.76×1.42-8B package.

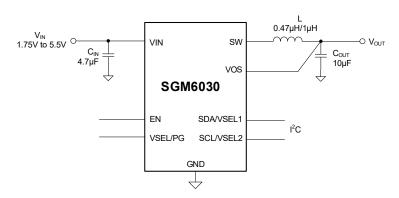

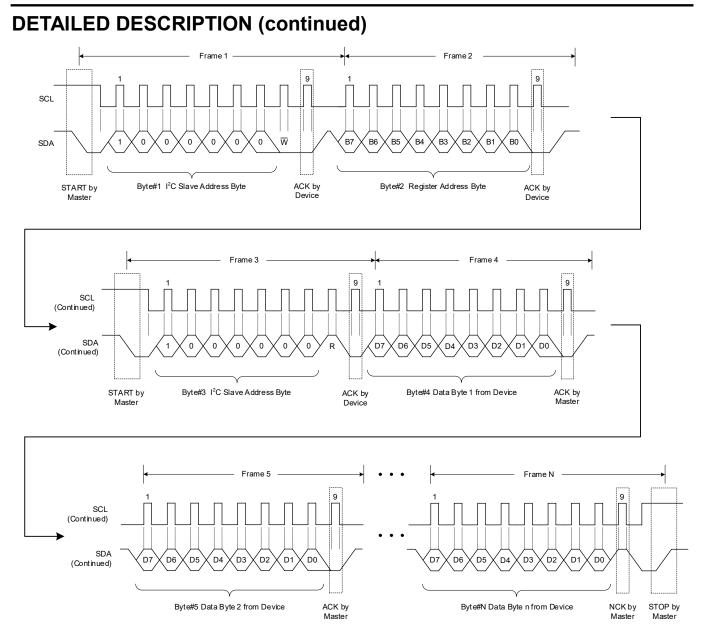

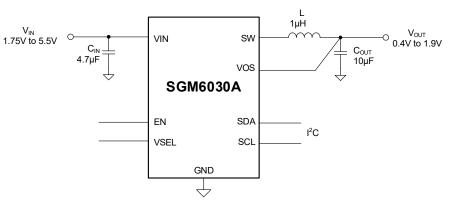

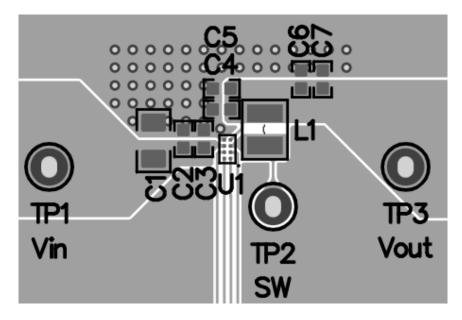

**TYPICAL APPLICATION**

# **FEATURES**

- 1.75V to 5.5V Input Voltage Range

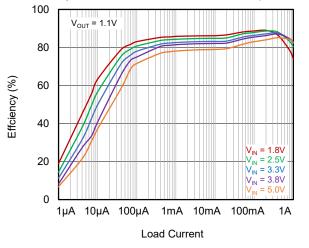

- 2.5µA (TYP) Operating Quiescent Current

- Up to 3.3MHz (TYP) Switching Frequency

- VSEL Pin Option for Changing Output Voltage

- Output Current

- SGM6030A/B/C/D: 0.6A

- SGM6030E: 1A

- Up to 1Mbps I<sup>2</sup>C Compatible Interface to Set:

- Output Voltage from 0.4V to 1.9875V with 12.5mV Steps

- Output Voltage Ramp Speed

- Available in a Green WLCSP-0.76×1.42-8B Package

### **APPLICATIONS**

**Mobile Phones**

Wearable and Portable Electronics Medical Sensor Patches and Patient Monitors

Figure 1. Typical Application Circuit

### **PACKAGE/ORDERING INFORMATION**

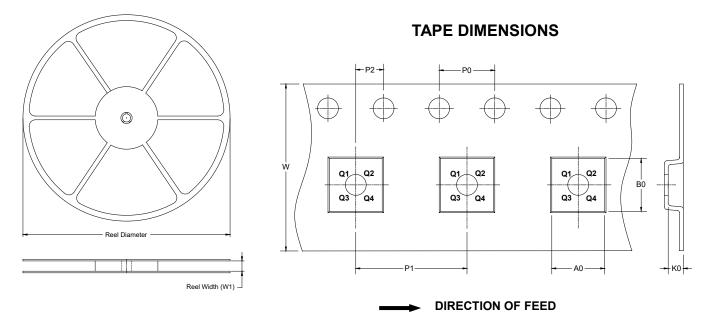

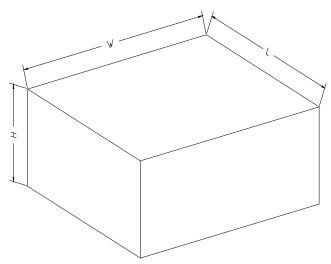

| MODEL    | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING | PACKING<br>OPTION   |

|----------|------------------------|-----------------------------------|--------------------|--------------------|---------------------|

| SGM6030A | WLCSP-0.76×1.42-8B     | -40°C to +125°C                   | SGM6030AXG/TR      | XXXX<br>1GR        | Tape and Reel, 5000 |

| SGM6030B | WLCSP-0.76×1.42-8B     | -40°C to +125°C                   | SGM6030BXG/TR      | XXXX<br>1TO        | Tape and Reel, 5000 |

| SGM6030C | WLCSP-0.76×1.42-8B     | -40°C to +125°C                   | SGM6030CXG/TR      | XXXX<br>246        | Tape and Reel, 5000 |

| SGM6030D | WLCSP-0.76×1.42-8B     | -40°C to +125°C                   | SGM6030DXG/TR      | XXXX<br>247        | Tape and Reel, 5000 |

| SGM6030E | WLCSP-0.76×1.42-8B     | -40°C to +125°C                   | SGM6030EXG/TR      | XXXX<br>1TP        | Tape and Reel, 5000 |

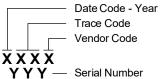

#### MARKING INFORMATION

NOTE: XXXX = Date Code, Trace Code and Vendor Code.

Serial Number

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

### **DEVICE OPTIONS**

| Device   | Output Current | Default Output Voltage Setting | fsw_fccm | User Interfaces            |

|----------|----------------|--------------------------------|----------|----------------------------|

| SGM6030A | 0.6A           | 0.6V, 1.1V                     | 1.4MHz   | EN, I <sup>2</sup> C, VSEL |

| SGM6030B | 0.6A           | 0.6V, 0.7V, 0.8V, 1.0V         | 1.4MHz   | 2 × VSEL, EN, PG           |

| SGM6030C | 0.6A           | 1.05V, 0.65V                   | 1.4MHz   | EN, I <sup>2</sup> C, VSEL |

| SGM6030D | 0.6A           | 0.85V, 1.1V                    | 1.4MHz   | EN, I <sup>2</sup> C, VSEL |

| SGM6030E | 1.0A           | 0.6V, 1.1V                     | 3.3MHz   | EN, I <sup>2</sup> C, VSEL |

#### **ABSOLUTE MAXIMUM RATINGS**

| VIN                                   | -0.3V to 6V            |

|---------------------------------------|------------------------|

| SW0.3V to                             | V <sub>IN</sub> + 0.3V |

| SW Transient < 10ns, While Switching  | -2.5V to 9V            |

| EN, VSEL/PG, SDA/VSEL1, SCL/VSEL2     | -0.3V to 6V            |

| VOS                                   | -0.3V to 5V            |

| Package Thermal Resistance            |                        |

| WLCSP-0.76×1.42-8Β, θ <sub>JA</sub>   | 170.2°C/W              |

| WLCSP-0.76×1.42-8Β, θ <sub>JB</sub>   | 53.9°C/W               |

| WLCSP-0.76×1.42-8Β, θJc               | 54.3°C/W               |

| Junction Temperature                  | +150°C                 |

| Storage Temperature Range65°C         | to +150°C              |

| Lead Temperature (Soldering, 10s)     | +260°C                 |

| ESD Susceptibility <sup>(1) (2)</sup> |                        |

| НВМ                                   | ±4000V                 |

| CDM                                   | ±1000V                 |

|                                       |                        |

#### NOTES:

1. For human body model (HBM), all pins comply with ANSI/ESDA/JEDEC JS-001 specifications.

2. For charged device model (CDM), all pins comply with ANSI/ESDA/JEDEC JS-002 specifications.

#### **RECOMMENDED OPERATING CONDITIONS**

| Input Supply Voltage, V <sub>IN</sub>          | .1.75V to 5.5V |

|------------------------------------------------|----------------|

| Output Voltage, V <sub>OUT</sub> 0.            | 4V to 1.9875V  |

| SW Voltage                                     | 0V to 5.5V     |

| EN, VSEL/PG, SDA/VSEL1, SCL/VSEL2              | 0V to 5.5V     |

| Output Current Range, IOUT                     |                |

| SGM6030E, V <sub>IN</sub> > 2.3V               | 1A (MAX)       |

| SGM6030E, V <sub>IN</sub> ≤ 2.3V               | 0.7A (MAX)     |

| SGM6030A/B/C/D                                 | 0.6A (MAX)     |

| Power Good Input Current Capability, IPG       | 1mA (MAX)      |

| Effective Input Capacitance, CIN2µF (MIN       | ), 4.7µF (TYP) |

| SGM6030E                                       |                |

| Effective Inductance, L 0.33µH to 0.82µH,      | 0.47µH (TYP)   |

| Effective Output Capacitance, C <sub>OUT</sub> | 2µF to 26µF    |

| SGM6030A/B/C/D                                 |                |

| Effective Inductance, L0.7µH to 1.2µF          | l, 1.0µH (TYP) |

| Effective Output Capacitance, COUT             | 3µF to 26µF    |

| Operating Junction Temperature Range4          | 0°C to +125°C  |

### 0.6A/1A Synchronous Buck Converter with I<sup>2</sup>C/VSEL Interface

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### DISCLAIMER

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

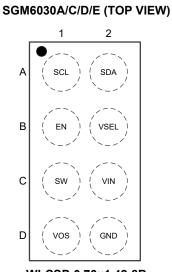

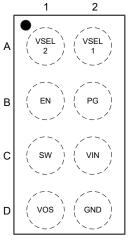

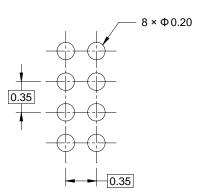

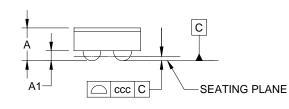

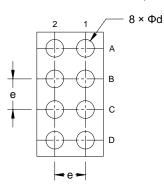

### **PIN CONFIGURATIONS**

WLCSP-0.76×1.42-8B

### **PIN DESCRIPTION**

#### SGM6030B (TOP VIEW)

WLCSP-0.76×1.42-8B

| PIN | NAME       | TYPE | FUNCTION                                                                                                                                                                                                                                               |

|-----|------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1  | SCL        | Ι    | I <sup>2</sup> C Bus Clock Signal. Do not leave it floating. Connect it to AGND if not used.                                                                                                                                                           |

| AI  | VSEL2      | I    | Voltage Selection Pin. Can be toggled during operation.                                                                                                                                                                                                |

|     | SDA        | I    | I <sup>2</sup> C Bus Data Signal. Do not leave it floating. Connect it to AGND if not used.                                                                                                                                                            |

| AZ  | A2 VSEL1 I |      | Voltage Selection Pin. Can be toggled during operation.                                                                                                                                                                                                |

| B1  | EN         | Ι    | Device Enable Pin. Logic high on this pin enables the device, and logic low on this pin disables the device. Do not leave it floating. The pin is connected with an internal pull-down resistor, which becomes inactive once the device is powered on. |

| B2  | VSEL       | I    | Voltage Selection Pin. Can be toggled during operation.<br>Low = 0.6V (SGM6030A/E), 1.05V (SGM6030C), 0.85V (SGM6030D).<br>High = 1.1V (SGM6030A/D/E), 0.65V (SGM6030C).                                                                               |

|     | PG         | 0    | Power Good Output. This is an open-drain signal. A pull-up resistor (connected to a DC voltage) is required to indicate high if the output voltage is within the regulation.                                                                           |

| C1  | SW         | Р    | Switching Node Output. Connect it to the filter inductor.                                                                                                                                                                                              |

| C2  | VIN        | Р    | Power Supply Input. Connect a ceramic capacitor ( $C_{IN}$ ) close to this pin and GND.                                                                                                                                                                |

| D1  | VOS        | Ι    | Output Voltage Sense Input. This pin is internally connected to the feedback loop and a MOSFET to discharge the output voltage ( $V_{OUT}$ ) when the device is disabled. Connect it to the output capacitor with a short trace.                       |

| D2  | GND        | G    | Ground Pin. Connect the $C_{IN}$ and $C_{OUT}$ ground terminals close to this pin.                                                                                                                                                                     |

NOTE: I = input, O = output, P = power, G = ground.

### **ELECTRICAL CHARACTERISTICS**

(V<sub>IN</sub> = 3.6V,  $T_J$  = -40°C to +125°C, all typical values are measured at  $T_J$  = +25°C, unless otherwise noted.)

| PARAMETER                                 | SYMBOL               | CONDITIONS                                         |                                                            |                                  | MIN          | TYP  | MAX  | UNITS    |

|-------------------------------------------|----------------------|----------------------------------------------------|------------------------------------------------------------|----------------------------------|--------------|------|------|----------|

| Supply                                    |                      |                                                    |                                                            |                                  |              |      |      |          |

|                                           |                      |                                                    |                                                            | 2V, device not switching,        |              | 2.5  | 5    |          |

| VIN Quiescent Current                     | Ι <sub>Q</sub>       |                                                    | C to +85°C                                                 |                                  |              | 2.0  | 5    | μA       |

|                                           |                      | EN = VI                                            | EN = VIN, $I_{OUT}$ = 0µA, $V_{OUT}$ = 1.2V, device switch |                                  |              | 2.5  |      |          |

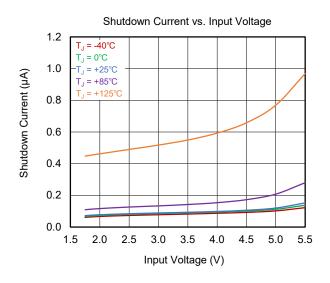

| VIN Shutdown Supply Current               | I <sub>SD</sub>      | EN = GND, shutdown current<br>into VIN, VSEL = GND |                                                            | T <sub>J</sub> = +25°C           |              | 100  | 150  | nA       |

|                                           | -50                  |                                                    |                                                            | $T_J$ = -40°C to +85°C           |              |      | 800  | 1        |

| UVLO                                      |                      |                                                    |                                                            |                                  |              |      |      |          |

| VIN UVLO Rising Threshold                 | $V_{UVLO_R}$         | $V_{\text{IN}}$ rising                             | l                                                          |                                  |              | 1.69 | 1.75 | V        |

| VIN UVLO Falling Threshold                | $V_{\text{UVLO}\_F}$ | V <sub>IN</sub> falling                            | g                                                          |                                  |              | 1.58 | 1.65 | V        |

| VIN UVLO Hysteresis                       | V <sub>UVLO_H</sub>  |                                                    |                                                            |                                  |              | 110  |      | mV       |

| Logic Pins                                |                      |                                                    |                                                            |                                  |              |      |      |          |

| High-Level Input Voltage Threshold        | V <sub>IH</sub>      |                                                    |                                                            |                                  | 0.8          |      |      | V        |

| Low-Level Input Voltage Threshold         | VIL                  |                                                    |                                                            |                                  |              |      | 0.4  | V        |

| Input Leakage Current into SDA, SCL, VSEL | I <sub>LKG</sub>     | Pin conn                                           | ected to VIN, T <sub>J</sub> = -40°C                       | C to +85℃                        |              | 10   |      | nA       |

| EN Internal Pull-Down Resistance          |                      | EN Pin te                                          | o GND                                                      |                                  |              | 0.5  |      | MΩ       |

| Input Leakage into EN                     | I <sub>LKG</sub>     | Pin conn                                           | Pin connected to VIN, $T_J = -40^{\circ}C$ to +85°C        |                                  |              |      |      | nA       |

| VOUT Voltage                              |                      |                                                    |                                                            |                                  |              | •    |      |          |

|                                           | V <sub>OUT</sub>     | PWM<br>mode,<br>no load                            | 1V < V <sub>OUT</sub> ≤ 1.9875V                            | T <sub>J</sub> = +25℃            | -1.5         |      | +1.5 | - %      |

|                                           |                      |                                                    |                                                            | T <sub>J</sub> = +25°C to +125°C | -2           |      | +2   |          |

|                                           |                      |                                                    | 0.5V < V <sub>OUT</sub> ≤ 1V                               | T <sub>J</sub> = +25℃            | -2           |      | +2   |          |

| Output Voltage Accuracy                   |                      |                                                    |                                                            | T <sub>J</sub> = +25℃ to +125℃   | -2.5         |      | +2.5 |          |

|                                           |                      |                                                    |                                                            | T <sub>J</sub> = +25℃            | -2           |      | +2   |          |

|                                           |                      |                                                    | $0.4V < V_{OUT} \le 0.5V$                                  | T <sub>J</sub> = -40°C to +125°C | -3           |      | +3   |          |

| VOS Input Leakage Current                 | I <sub>VOS_LKG</sub> |                                                    | N, V <sub>OUT</sub> = 1.2V (internal<br>C to +85℃          | 3.2M $\Omega$ resistor divider), |              | 400  | 1000 | nA       |

| Switching Frequency                       |                      | 13 40                                              |                                                            |                                  |              |      |      | <u>i</u> |

|                                           | Ι                    | V - 2 C                                            | V V - 4 0V                                                 | SGM6030E                         |              | 3.3  |      |          |

| Switching Frequency, FCCM Operation       | f <sub>sw_FCCM</sub> | $V_{IN} = 3.6$<br>PWM op                           | V, V <sub>OUT</sub> = 1.2V,<br>eration                     | SGM6030A/B/C/D                   |              | 1.4  |      | MHz      |

| Start-up                                  |                      | I                                                  |                                                            |                                  |              | 1.7  |      | <u> </u> |

| Internal Fixed Soft-Start Time            | t <sub>ss</sub>      | from Vol                                           | т = 0V to 95% of V <sub>OUT</sub> n                        | ominal                           |              | 0.12 | 0.25 | ms       |

| EN High to Start of Switching Delay       | •>>                  |                                                    |                                                            |                                  |              | 500  | 1100 | μs       |

| Power Stage                               | I                    | 1                                                  |                                                            |                                  | l            | 000  |      | P0       |

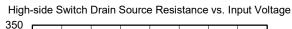

| High-side MOSFET On-Resistance            | R <sub>DSON_H</sub>  | Jour = 50                                          | 0mA                                                        |                                  |              | 115  | 180  | mΩ       |

| Low-side MOSFET On-Resistance             | RDSON_H              |                                                    | I <sub>OUT</sub> = 500mA<br>I <sub>OUT</sub> = 500mA       |                                  |              | 90   | 165  | mΩ       |

| Over-Current Protection                   | . 1000N_L            | 1.001 00                                           | <b>·</b>                                                   |                                  | 1            |      |      |          |

| High-side Peak Current Limit              | I <sub>HS_OC</sub>   | SGM603                                             | SGM6030E                                                   |                                  |              | 1.70 | 2.10 | А        |

| Low-side Valley Current Limit             | I <sub>LS_OC</sub>   | SGM603                                             |                                                            |                                  | 1.20<br>0.75 | 1.05 | 1.30 | A        |

| High-side Peak Current Limit              |                      |                                                    | 0A/B/C/D                                                   |                                  | 0.95         | 1.20 | 1.45 | A        |

| Low-side Valley Current Limit             |                      |                                                    | 0A/B/C/D                                                   |                                  | 0.95         | 0.85 | 1.45 | A        |

| Low-side Negative Current Limit           | I <sub>LS_OC</sub>   |                                                    | current limit on low-side                                  | FET                              | 0.00         | 0.65 | 1.05 | A        |

| Low-side negative Cullent Linit           | I <sub>LS_NOC</sub>  | Sinking                                            | Surrent minit off low-side                                 |                                  |              | 0.00 |      | А        |

# **ELECTRICAL CHARACTERISTICS (continued)** (V<sub>IN</sub> = 3.6V, T<sub>J</sub> = -40°C to +125°C, all typical values are measured at T<sub>J</sub> = +25°C, unless otherwise noted.)

| PARAMETER                            | SYMBOL              | CONDITIONS                                                       | MIN              | TYP | MAX | UNITS |

|--------------------------------------|---------------------|------------------------------------------------------------------|------------------|-----|-----|-------|

| Power Good                           |                     |                                                                  |                  |     |     |       |

| Deven Or d Three hold                | V <sub>PGTH</sub>   | PGOOD low, V <sub>os</sub> falling                               |                  | 93  |     | %     |

| Power Good Threshold                 | VPGTH               | PGOOD high, V <sub>os</sub> rising                               |                  | 96  |     | 70    |

| Power Good Deglitch Delay            | t <sub>PG_DLY</sub> | PG rising edge                                                   | PG rising edge 5 |     |     | μs    |

| Input Leakage Current into PG Pin    | I <sub>PG_LKG</sub> | V <sub>PG</sub> = 5.0V                                           |                  | 10  |     | nA    |

| PG Pin Output Low-Level Voltage      |                     | I <sub>PG</sub> = 1mA                                            |                  |     | 400 | mV    |

| Output Discharge                     |                     |                                                                  |                  |     |     |       |

| Output Discharge Resistor on VOS Pin |                     | EN = GND, $I_{VOS}$ = -10mA into VOS pin, $T_J$ = -40°C to +85°C |                  | 7   | 11  | Ω     |

| Thermal Shutdown                     |                     |                                                                  |                  |     |     |       |

| Thermal Shutdown Threshold           | $T_{SD}$            | Temperature rising, PWM mode                                     |                  | 160 |     | °C    |

| Thermal Shutdown Hysteresis          | T <sub>HYS</sub>    |                                                                  |                  | 20  |     | °C    |

# I<sup>2</sup>C INTERFACE TIMING CHARACTERISTICS

| PARAMETER (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SYMBOL                            | CONDITIONS     | MIN                    | TYP | MAX  | UNITS |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------|------------------------|-----|------|-------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   | Standard Mode  |                        |     | 100  | kHz   |  |

| SCL Clock Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | f <sub>SCL</sub>                  | Fast Mode      |                        |     | 400  | kHz   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   | Fast Mode Plus |                        |     | 1    | MHz   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   | Standard Mode  | 4.7                    |     |      |       |  |

| Bus Free Time Between a Stop and Start Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | t <sub>BUF</sub>                  | Fast Mode      | 1.3                    |     |      | μs    |  |

| Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                   | Fast Mode Plus | 0.5                    |     |      |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   | Standard Mode  | 4                      |     |      |       |  |

| Hold Time (Repeated) Start Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $t_{HD,} t_{STA}$                 | Fast Mode      | 0.6                    |     |      | μs    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   | Fast Mode Plus | 0.26                   |     |      |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   | Standard Mode  | 4.7                    |     |      |       |  |

| Low Period of the SCL Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | t <sub>LOW</sub>                  | Fast Mode      | 1.3                    |     |      | μs    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   | Fast Mode Plus | 0.5                    |     |      |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   | Standard Mode  | 4                      |     |      |       |  |

| High Period of the SCL Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | t <sub>HIGH</sub>                 | Fast Mode      | 0.6                    |     |      | μs    |  |

| °                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                   | Fast Mode Plus | 0.26                   |     |      |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   | Standard Mode  | 4.7                    |     |      |       |  |

| Setup Time for a Repeated Start Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $t_{SU,} t_{STA}$                 | Fast Mode      | 0.6                    |     |      | μs    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 00, 0111                          | Fast Mode Plus | 0.26                   |     |      |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   | Standard Mode  | 250                    |     |      |       |  |

| Data Setup Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $t_{SU,} t_{DAT}$                 | Fast Mode      | 100                    |     |      | ns    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | - /                               | Fast Mode Plus | 50                     |     |      | -     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   | Standard Mode  | 0                      |     | 3.45 |       |  |

| Data Hold Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $t_{HD,} t_{DAT}$                 | Fast Mode      | 0                      |     | 0.9  | μs    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   | Fast Mode Plus | 0                      |     |      | 1 .   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   | Standard Mode  |                        |     | 1000 |       |  |

| Rise Time of SCL Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | t <sub>RCL</sub>                  | Fast Mode      | 20 + 0.1C <sub>B</sub> |     | 300  | ns    |  |

| ç                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                   | Fast Mode Plus |                        |     | 120  |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   | Standard Mode  | 20 + 0.1C <sub>B</sub> |     | 1000 |       |  |

| Rise Time of SCL Signal after a Repeated Start                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | t <sub>RCL1</sub>                 | Fast Mode      | 20 + 0.1C <sub>B</sub> |     | 300  | ns    |  |

| Condition and after an Acknowledge Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                   | Fast Mode Plus |                        |     | 120  |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   | Standard Mode  | 20 + 0.1C <sub>B</sub> |     | 300  |       |  |

| Fall Time of SCL Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | t <sub>FCL</sub>                  | Fast Mode      |                        |     | 300  | ns    |  |

| , and the second s |                                   | Fast Mode Plus |                        |     | 120  | -     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   | Standard Mode  |                        |     | 1000 |       |  |

| Rise Time of SDA Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | t <sub>RDA</sub>                  | Fast Mode      | 20 + 0.1C <sub>B</sub> |     | 300  | ns    |  |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                   | Fast Mode Plus |                        |     | 120  | -     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   | Standard Mode  |                        |     | 300  |       |  |

| Fall Time of SDA Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | t <sub>FDA</sub>                  | Fast Mode      | 20 + 0.1C <sub>B</sub> |     | 300  | ns    |  |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                   | Fast Mode Plus |                        |     | 120  | -     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   | Standard Mode  | 4                      |     |      |       |  |

| Setup Time of Stop Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | t <sub>su,</sub> t <sub>sтo</sub> | Fast Mode      | 0.6                    |     |      | μs    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   | Fast Mode Plus | 0.26                   |     |      |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   | Standard Mode  |                        |     | 400  |       |  |

| Capacitive Load for SDA and SCL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | C <sub>B</sub>                    | Fast Mode      |                        |     | 400  | pF    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   | Fast Mode Plus |                        |     | 550  | 1 .   |  |

#### NOTE:

1. All values refer to  $V_{\text{IL}}$  (MAX) and  $V_{\text{IH}}$  (MIN) levels.

### **TYPICAL PERFORMANCE CHARACTERISTICS**

$T_A$  = +25°C,  $V_{IN}$  = 3.8V, unless otherwise noted.

Time (20µs/div)

DVS with 5mV/µs, 10mV/µs Slew Rate

SG Micro Corp

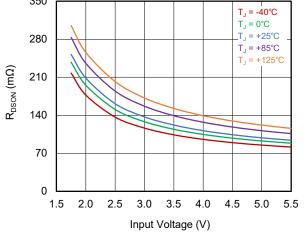

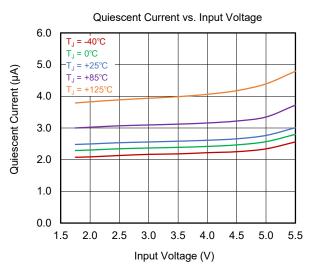

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_A = +25^{\circ}C$ ,  $V_{IN} = 3.8V$ , unless otherwise noted.

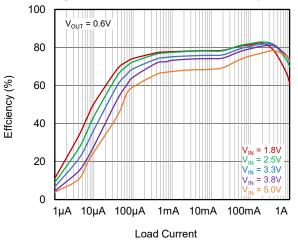

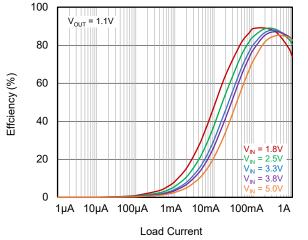

Efficiency vs. Load Current in Power Save Mode (SGM6030E)

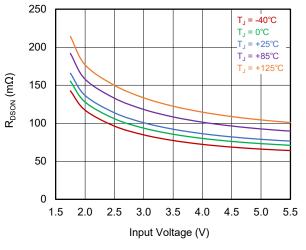

Low-side Switch Drain Source Resistance vs. Input Voltage

Efficiency vs. Load Current in Power Save Mode (SGM6030E)

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_A = +25^{\circ}C$ ,  $V_{IN} = 3.8V$ , unless otherwise noted.

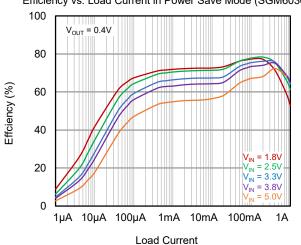

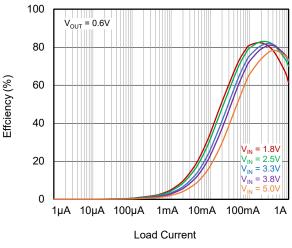

Efficiency vs. Load Current in Power Save Mode (SGM6030E)

Efficiency vs. Load Current in Power Save Mode (SGM6030A)

Efficiency vs. Load Current in Power Save Mode (SGM6030E) 100 = 1.9875V 80 Effciency (%) 60 40 20 2.5 = 3.3\ = 3.8V 5.0\ 0 1µA 10µA 100µA 1mA 10mA 100mA 1A Load Current

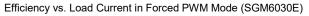

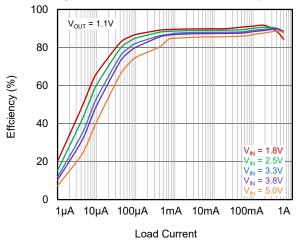

Efficiency vs. Load Current in Forced PWM Mode(SGM6030E)

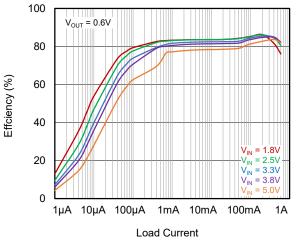

Efficiency vs. Load Current in Power Save Mode (SGM6030A)

# 0.6A/1A Synchronous Buck Converter with I<sup>2</sup>C/VSEL Interface

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_A$  = +25°C,  $V_{IN}$  = 3.8V, unless otherwise noted.

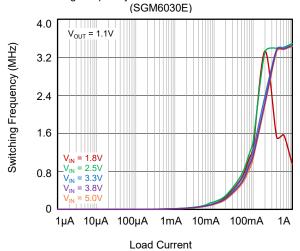

Switching Frequency vs. Load Current in Power Save Mode (SGM6030E)

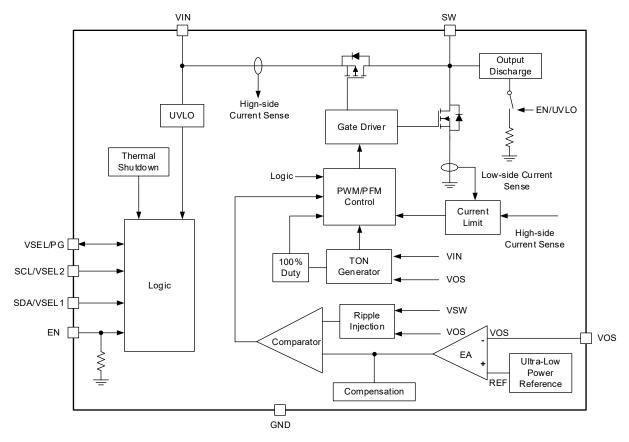

# FUNCTIONAL BLOCK DIAGRAM

Figure 2. Block Diagram

# **DETAILED DESCRIPTION**

### Overview

The SGM6030 is a 2.5µA (TYP) quiescent current synchronous Buck converter that adopts the constant on-time (COT) control architecture to achieve excellent load/line transient performance. The family of SGM6030 devices offers easy programmable output voltages via I<sup>2</sup>C settings with 12.5mV adjustment steps, or the SGM6030B offers 4 different fixed output voltages via programming the VSEL1 and VSEL2 pins. The COT architecture is not limited by traditional fixed frequency architecture where switching pulses are confined by the edge switching frequency clock, a main voltage comparator is implemented to signal the changes occurring at the output. In addition, by sensing the actual output voltage, the COT architecture can quickly adapt to any load transient event and quickly adjust the switching frequency to replenish the energy delivered to the load. An internally compensated voltage error amplifier is also implemented in the SGM6030 to provide accurate DC load regulation. The SGM6030 just needs 4 external components to realize the design, which significantly reduces the solution size.

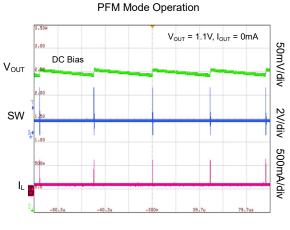

#### Feature Description Power-Save Mode

As the load current decreases, the inductor current reaches around 0A in a switching cycle, the operation mode becomes discontinuous. The SGM6030 automatically enters power-save mode (PSM) in discontinuous mode. Adding more output capacitors will minimize the output voltage rise in PSM.

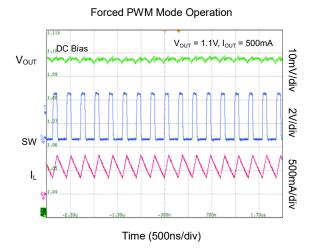

#### **Forced PWM Operation**

The SGM6030 is able to operate in forced PWM mode to achieve fixed switching frequency and output ripple across the entire operating load range. Forced PWM is configurable in **REG0x03** control register via  $l^2C$ .

#### Enable and Shutdown (EN)

$I^2C$  interface is live when the EN pin is toggled logic high after the enable delay time. When the EN pin is toggled to logic low, power FETs are off as well as the internal control circuits, register settings are reset except the EN\_DIS bit. Device enters shutdown mode when EN pin is logic low,  $I^2C$  communication is terminated in this mode.

The device also supports a software enable/disable via EN\_DEVICE bit in **REG0x03** register while EN pin is toggled to logic high. When the device is enabled by

this bit, the device starts up with soft-start time. No EN high to start the switching delay is required. When the device is disabled by this bit, the device stops switching, but  $I^2C$  communication remains active.

#### Soft-Start

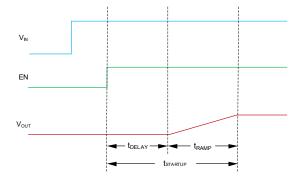

When the input voltage is above the UVLO rising threshold of 1.69V (TYP), toggling the enable pin to logic high to start up the device. Before the output voltage starts ramping up, the device has an enable delay of 500 $\mu$ s (TYP). During the enable delay, the device establishes the internal reference determined by the VSEL pin or VSEL1/2 pin. The internal registers can be programmed via I<sup>2</sup>C after the enable delay.

Figure 3. Start-up Sequence

The device initiates an internal soft-start when the enable delay finishes. The internal soft-start time is fixed to 0.12ms (TYP) to ramp up the output voltage from 0V to the programmed output voltage (95%). The soft-start mechanism effectively reduces the inrush current drawn from the input source, as well as providing a controlled output voltage rising ramp. For pre-biased output voltage start-up, the device starts up from the pre-biased voltage to the programmed output voltage.

#### Output Voltage Selection (VSEL) for SGM6030B

SGM6030B uses 2 VSEL interfaces to set the output voltage. The programmable output voltages are shown in Table 1.

Table 1. Target Output Voltages Setting by VSEL Interface

| VSEL1 | VSEL2 | SGM6030B | <b>Operation Mode</b> |

|-------|-------|----------|-----------------------|

| 0     | 0     | 0.6V     | PFM                   |

| 1     | 0     | 0.7V     | PFM                   |

| 0     | 1     | 0.8V     | PFM                   |

| 1     | 1     | 1.0V     | PFM                   |

### **DETAILED DESCRIPTION (continued)**

#### Output Voltage Selection (VSEL and I<sup>2</sup>C)

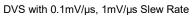

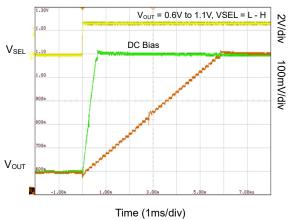

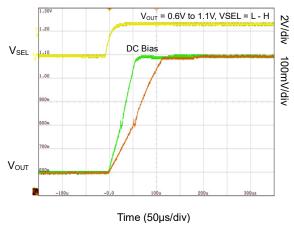

The device offers 2 selectable output voltage registers. Dynamic voltage scaling (DVS) is supported via these 2 registers. VSEL is utilized to select the active register between VO1\_SET bits and VO2\_SET bits.

Output voltage adjustment can be made via either I<sup>2</sup>C programming or toggling the VSEL pin, and the output voltage ramp-up/down speed is also configurable via the VOL\_RAMP bits in **REG0x03** register.

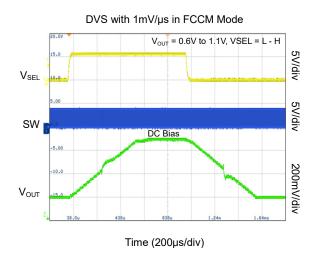

#### Forced PWM Mode during $V_{\mbox{\scriptsize OUT}}$ Change

During normal operation, the device does not enter forced PWM mode when receives a VSEL toggle or an  $I^2C$  command to adjust  $V_{OUT}$ . Forced PWM mode during DVS allows a controlled downward ramp of  $V_{OUT}$  independent of load condition.

#### Power Good (PG) for SGM6030B

The SGM6030B (do not have VSEL) offers power good function. The device starts to compare the actual output voltage with the VSEL1/2 programmed output voltage after the enable delay time. When the voltage reaches 96% (TYP) of programmed output voltage, after 50µs (TYP) delay, the PG enters high-impedance status. When VIN starts up for the first time, the PG remains high until the device is enabled for the first time.

By default, the PG is pulled low immediately during the DVS stage without any blanking period or delay. Once the output voltage ( $V_{OUT}$ ) reaches the new target level, the PG signal becomes high again.

|                           | Lo | gic Signals         | DVS                          |     |           |  |

|---------------------------|----|---------------------|------------------------------|-----|-----------|--|

|                           |    | Thermal<br>Shutdown | Vour                         |     | PG Status |  |

|                           | Н  | NO                  | $V_{\text{OUT}}$ on          | NO  | Z         |  |

|                           | Н  | NO                  | Target                       | YES | L         |  |

| V <sub>IN</sub> ><br>UVLO | Н  | NO                  | V <sub>OUT</sub> <<br>Target | X   | L         |  |

|                           | Н  | YES                 | X                            | X   | L         |  |

|                           | L  | X                   | Х                            | Х   | L         |  |

| V <sub>IN</sub> <<br>UVLO | X  | X                   | X                            | X   | Undefined |  |

#### Table 2. Power Good Indicator Function Table

H = High Voltage Level, L = Low Voltage Level,

Z = High-Impedance State, X = Don't Care

#### Under-Voltage Lockout (UVLO)

The SGM6030 offers input under-voltage lockout to prevent false triggering with unstable input source. The device's UVLO rising voltage is 1.69V (TYP) and falling threshold is 1.58V (TYP). Device stops operation as

soon as the input voltage drops below the falling threshold. The output voltage discharge is active when UVLO falling threshold is reached. The output voltage discharge function is programmable via **REG0x03** register.

#### Switch Current Limit/Short-Circuit Protection

The device implements over-current protection when the load exceeds the maximum allowed 1A (SGM6030E) or 0.6A (SGM6030A/B/C/D) to prevent excessive current drawn from battery type inputs. During an output short scenario or a saturated inductor, the inductor current will reach the current limit threshold. When the current limit threshold is reached, the device turns off the high-side switch to terminate the inductor current from further increase, and the low-side switch turns on to ramp down the inductor current to the low-side switch current limit.

During the short-circuit event, as the output voltage drops below 150mV, the current limit threshold is foldback to 0.66A for SGM6030A/B/C/D/E version to prevent the device from excessive temperature rise.

#### Output Voltage Discharge

The device implements I<sup>2</sup>C programmable output voltage discharge function for application requiring sequencing control. The internal discharge path discharges the output voltage through the SW pin to ground. There are four scenarios to discharge the output voltage: EN pin is toggled to logic low. EN\_DEVICE bit in **REG0x03** register is set to 0, input voltage UVLO and device thermal shutdown.

Output voltage discharge function is disabled when the EN\_DIS bit is set to 0. The output discharge function remains active as long as the input voltage is higher than 1V (TYP) and the EN\_DIS bit is retained. When a rising edge of the EN pin is applied, the EN\_DIS bit is reset.

#### **Thermal Shutdown**

As the junction temperature exceeds the  $T_{SD}$  (160°C, TYP), the device stops switching, enabling active discharge to discharge the output voltage and disable both MOSFETs. The device has a 20 °C thermal shutdown hysteresis to allow the device to resume operation automatically with an internal soft-start. The register settings are not changed during thermal shutdown. This function is disabled when the device is under PFM mode.

## **DETAILED DESCRIPTION (continued)**

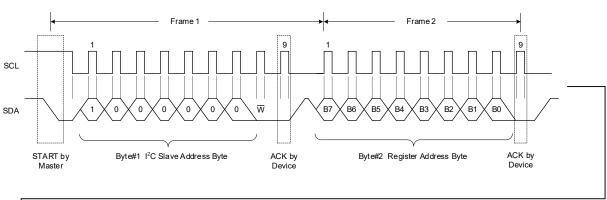

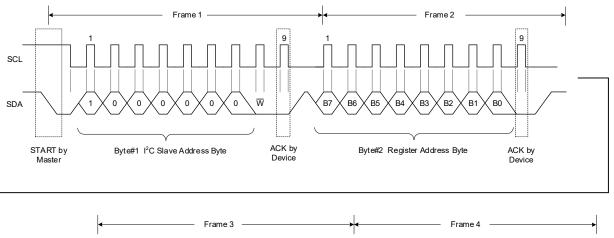

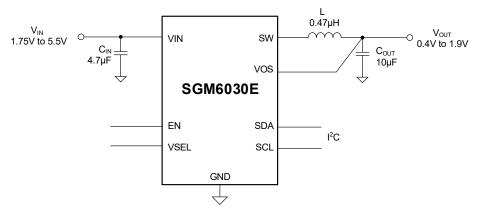

#### I<sup>2</sup>C Serial Interface and Data Communication

Standard I<sup>2</sup>C interface is used to program SGM6030 parameters and get status reports. I<sup>2</sup>C is the well-known 2-wire serial communication interface that can connect one (or more) master device(s) to some slave devices for two-way communication. The bus lines are named serial data (SDA) and serial clock (SCL). The device that initiates a data transfer is a master. A master generates the SCL signal. Slave devices have unique addresses to identify. A master is typically a micro controller or a digital signal processor.

The SGM6030 operates as a slave device that address is 0x40 (40H). It has four 8-bit registers, numbered from REG0x01 to REG0x03 and REG0x05. A register read besides these REGs returns 0xFF.

#### **Physical Layer**

The standard  $l^2C$  interface of SGM6030 supports standard mode and fast mode plus communication speeds. The frequency of stand mode is up to 100kbits/s, while the fast mode plus is up to 1Mbits/s. The SDA pin is open-drain.

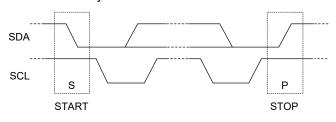

#### I<sup>2</sup>C Data Communication START and STOP Conditions

A transaction is started by taking control of the bus by master if the bus is free. The transaction is terminated by releasing the bus when the data transfer job is done as shown in Figure 6. All transactions begin by master which applies a START condition on the bus lines to take over the bus and exchange data. At the end, the master terminates the transaction by applying one (or more) STOP condition. START condition is defined when SCL is high and a high to low transition on the SDA is generated by master. Similarly, a STOP is defined when SCL is high and SDA goes from low to high. START and STOP are always generated by a master. After a START and before a STOP, the bus is considered busy.

Figure 4. I<sup>2</sup>C Bus in START and STOP Conditions

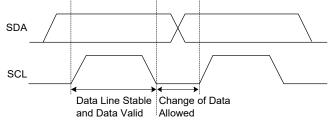

#### **Data Bit Transmission and Validity**

The data bit (high or low) must remain stable during clock high period. The state of SDA can only change when SCL is low. For each data bit transmission, one clock pulse is generated by master. Bit transfer in  $I^2C$  is shown in Figure 5.

Figure 5. I<sup>2</sup>C Bus Bit Transfer

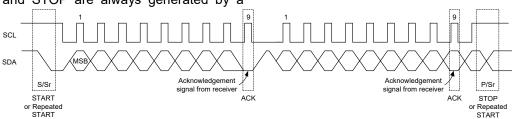

#### Byte Format

Data is transmitted in 8-bit packets (one byte at a time). The number of bytes in one transaction is not limited. In each packet, the 8 bits are sent successively with the Most Significant Bit (MSB) first. An acknowledge (or not-acknowledge) bit must come after the 8 data bits. This bit informs the transmitter whether the receiver is ready to proceed for the next byte or not. Figure 6 shows the byte transfer process with I<sup>2</sup>C interface.

Figure 6. Byte Transfer Process

# **DETAILED DESCRIPTION (continued)**

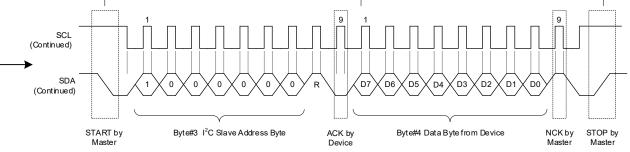

#### Acknowledge (ACK) and Not Acknowledge (NCK)

After transmission of each byte by transmitter, an acknowledge bit is replied by the receiver as the ninth bit. With the acknowledge bit, the receiver informs the transmitter that the byte is received, and another byte is expected or can be sent (ACK) or it is not expected (NCK = not ACK). Clock (SCL) is always generated by master, including the acknowledge clock pulse, no matter who is acting as transmitter or receiver. SDA line is released for receiver control during the acknowledge clock pulse. And the receiver can pull the SDA line low as ACK (reply a 0 bit) or let it be high as NCK during the SCL high pulse. After that, the master can either apply a STOP (P) condition to end the transaction or send a new START (S) condition to start a new transfer (called repeated start). For example, when master wants to read a register in slave, one start is needed to send the slave address and register address, and then, without a STOP condition, another start is sent by master to initiate the receiving transaction from slave. Master then sends the STOP condition and releases the bus.

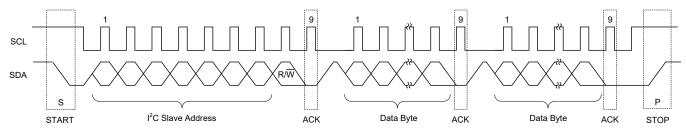

#### **Data Direction Bit and Addressing Slaves**

The first byte sent by master after the START is always the target slave address (7 bits) and an eighth data-direction bit ( $R/\overline{W}$ ).  $R/\overline{W}$  bit is 0 for a WRITE

transaction and 1 for READ (when master is asking for data). Data direction is the same for all next bytes of the transaction. To reverse it, a new START or repeated START condition must be sent by master (STOP will end the transaction). Usually the second byte is a WRITE sending the register address that is supposed to be accessed in the next byte(s). The data transfer transaction is shown in Figure 7.

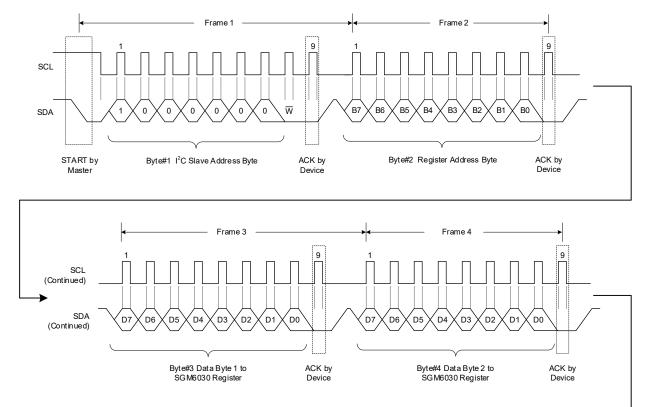

**WRITE:** If the master wants to write in the register, the third byte can be written directly as shown in Figure 10 for a single write data transfer. After receiving the ACK, master may issue a STOP condition to end the transaction or send the next register data, which will be written to the next address in a slave as multi-write. A STOP is needed after sending the last data.

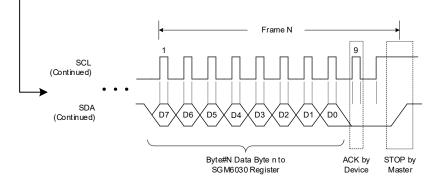

**READ:** If the master wants to read a single register (Figure 11), it sends a new START condition along with device address with  $R/\overline{W}$  bit = 1. After ACK is received, master reads the SDA line to receive the content of the register. Master replies with NCK to inform slave that no more data is needed (single read) or it can send an ACK to request for sending the next register content (multi-read). This can continue until an NCK is sent by master. A STOP must be sent by master in any case to end the transaction.

Figure 7. Data Transfer Transaction

# 0.6A/1A Synchronous Buck Converter with I<sup>2</sup>C/VSEL Interface

### **DETAILED DESCRIPTION (continued)**

Figure 8. A Single Write Transaction

### **DETAILED DESCRIPTION (continued)**

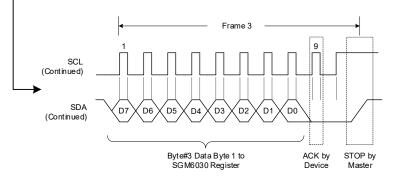

#### Data Transactions with Multi-Read or Multi-Write

Multi-read and multi-write are supported by SGM6030 for REG0x01 through REG0x05 registers. In the multi-write, every new data byte sent by master is written to the next register of the device. A STOP is sent whenever master is done with writing into device registers. In a multi-read transaction, after receiving the first register data (its address is already written to the slave), the master replies with an ACK to ask the slave to send the next register data. This can continue as much as it is needed by master. Master sends back an NCK after the last received byte and issues a STOP condition.

Figure 10. A Multi-Write Transaction

# 0.6A/1A Synchronous Buck Converter with I<sup>2</sup>C/VSEL Interface

Figure 11. A Multi-Read Transaction

### **REGISTER MAPS**

All registers are 8-bit and individual bits are named from D[0] (LSB) to D[7] (MSB).

### I<sup>2</sup>C Register Address

| ADDRESS | REGISTER NAME | D[7]         | D[6]            | D[5]         | D[4]    | D[3]   | D[2]     | D[1]          | D[0] |

|---------|---------------|--------------|-----------------|--------------|---------|--------|----------|---------------|------|

| 0x01    | VO1_SET       | Reserved     | VO1_SET[6:0]    |              |         |        |          |               |      |