# SGM25811 High-Voltage MOSFET Drivers for Buck Converter Applications

### **GENERAL DESCRIPTION**

The SGM25811 is a specialized dual, high-voltage MOSFET driver to efficiently drive two N-MOSFETs in a synchronous-rectified Buck converter. When combined with a multi-phase Buck PWM controller, it forms the core of voltage regulator for advanced micro-processors.

Its features also include anti-shoot-through protection, ensuring there's no cross-conduction in external MOSFETs while optimizing efficiency with minimal dead time. Additionally, it integrates a bootstrap switch, which eliminates the need for other external components. Controlling both gate drives is simple: pulling the EN pin low or putting the PWM pin to a high-impedance condition deactivates both, preventing the output capacitor from rapidly discharging while the system is shut down. Notably, the SGM25811 also has input under-voltage lockout function.

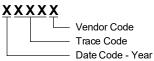

The SGM25811A and SGM25811B are available in a Green TDFN-2×2-8L package. The SGM25811C is available in a Green TDFN-3×3-8BL package. The SGM25811D is available in a Green SOIC-8 (Exposed Pad) package.

## FEATURES

- Suitable for HVMOS Driving (V<sub>GS</sub> = V<sub>IN</sub> = 12V)

- Single PWM Signal Controls Dual Drivers

- Integrated Synchronous Buck Driver Solution

- Anti-Shoot-Through Protection Circuitry

- Bridge Shutdown by Using Tri-State Input

- Built-in Bootstrap Switch Integration

- Turn Off both MOSFETs by Using EN Control

- Utilize PWM Pin for Multi-Functional Settings

- Supply Input Under-Voltage Lockout

- SGM25811A and SGM25811B are Available in a Green TDFN-2×2-8L Package SGM25811C is Available in a Green TDFN-3×3-8BL Package SGM25811D is Available in a Green SOIC-8 (Exposed Pad) Package

### APPLICATIONS

Voltage Regulators for Desktop CPU Cores Low Profile DC/DC Converters Operating at High Frequencies DC/DC Converters for Low Voltage at High Currents

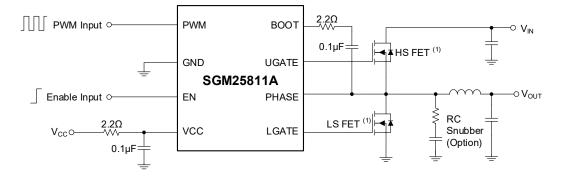

### **TYPICAL APPLICATION**

NOTE: 1. Suggested total solution: HS FET = SGMNQ40430, LS FET = SGMNQ28430.

Figure 1. Typical Application Circuit

### PACKAGE/ORDERING INFORMATION

| MODEL     | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING      | PACKING<br>OPTION   |

|-----------|------------------------|-----------------------------------|--------------------|-------------------------|---------------------|

| SGM25811A | TDFN-2×2-8L            | -40°C to +105°C                   | SGM25811AGTDE8G/TR | 0MK<br>XXXX             | Tape and Reel, 3000 |

| SGM25811B | TDFN-2×2-8L            | -40°C to +105°C                   | SGM25811BGTDE8G/TR | 0ML<br>XXXX             | Tape and Reel, 3000 |

| SGM25811C | TDFN-3×3-8BL           | -40°C to +105°C                   | SGM25811CGTDD8G/TR | SGM<br>0MNDD<br>XXXXX   | Tape and Reel, 4000 |

| SGM25811D | SOIC-8 (Exposed Pad)   | -40°C to +105°C                   | SGM25811DGPS8G/TR  | SGM<br>0MOGPS8<br>XXXXX | Tape and Reel, 4000 |

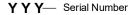

#### MARKING INFORMATION

NOTE: XXXX = Date Code, Trace Code and Vendor Code. XXXXX = Date Code, Trace Code and Vendor Code. TDFN-2×2-8L

XXXX

Vendor Code Trace Code

Date Code - Year

TDFN-3×3-8BL/SOIC-8 (Exposed Pad)

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Input Voltage, V <sub>CC</sub><br>BOOT to PHASE |                                   |

|--------------------------------------------------------|-----------------------------------|

| PHASE to GND                                           |                                   |

| DC                                                     | 0.7V to 15V                       |

| < 200ns                                                | 8V to 30V                         |

| BOOT to GND                                            |                                   |

| DC                                                     | -0.3V to (V <sub>cc</sub> + 15V)  |

| < 200ns                                                | -0.3V to 42V                      |

| UGATE to PHASE                                         |                                   |

| DC                                                     | -0.3V to (BOOT - PHASE + 0.3V)    |

| < 200ns                                                | 5V to (BOOT - PHASE + 0.3V)       |

| LGATE to GND                                           |                                   |

| DC                                                     | -0.3V to (V <sub>CC</sub> + 0.3V) |

| < 200ns                                                | -5V to (V <sub>CC</sub> + 0.3V)   |

| PWM                                                    | -0.3V to 6V                       |

| EN                                                     | -0.3V to (V <sub>CC</sub> + 0.3V) |

| Package Thermal Resistance                             |                                   |

| TDFN-2×2-8L, θ <sub>JA</sub>                           | 111.5°C/W                         |

| TDFN-2×2-8L, θ <sub>JB</sub>                           |                                   |

| TDFN-2×2-8L, θ <sub>JC (TOP)</sub>                     |                                   |

| TDFN-2×2-8L, θ <sub>JC (BOT)</sub>                     |                                   |

| TDFN-3×3-8BL, $\theta_{JA}$                            |                                   |

|                                                        | 57.7°C/W                          |

| TDFN-3×3-8BL, $\theta_{JC (TOP)}$                      |                                   |

| . ,                                                    |                                   |

|                                                        |                                   |

|                                                        |                                   |

|                                                        |                                   |

|                                                        | 10.4°C/W                          |

| Power Dissipation, $P_D @ T_A = +25$                   |                                   |

|                                                        | 0.89W                             |

| TDFN-3×3-8BL                                           |                                   |

|                                                        |                                   |

| •                                       |  |

|-----------------------------------------|--|

| SOIC-8 (Exposed Pad) 2.29W              |  |

| Junction Temperature+150°C              |  |

| Storage Temperature Range65°C to +150°C |  |

| Lead Temperature (Soldering, 10s)+260°C |  |

| ESD Susceptibility                      |  |

| HBM                                     |  |

| CDM                                     |  |

#### **RECOMMENDED OPERATING CONDITIONS**

| Supply Input Voltage, V <sub>CC</sub> | 10.8V to 13.2V |

|---------------------------------------|----------------|

| Operating Junction Temperature Range  | 40°C to +125°C |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### DISCLAIMER

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

### **PIN CONFIGURATIONS**

### **PIN DESCRIPTION**

| PIN                                      |                            |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|------------------------------------------|----------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| SGM25811A/<br>SGM25811C/<br>SGM25811D    | SGM25811B                  | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 1                                        | 8                          | BOOT  | Bootstrap Pin. Supply upper gate driver. A $0.1\mu$ F ceramic capacitor and a $2.2\Omega$ R <sub>BOOT</sub> are connected between this pin and PHASE pin. Ensure the $0.1\mu$ F ceramic capacitor is placed near the IC.                                                                                                                                                                                                                             |  |  |  |  |

| 2                                        | 1                          | PWM   | PWM Input. The PWM input pin receives logic-level signals, and directly controls the driver outputs. If the EN input is low, the PWM pin operates in a high-impedance state. Conversely, when the EN input is high, the internal circuit pulls the PWM pin voltage to a tri-state configuration. To ensure proper functionality of the PWM controller, the resistor connected from the PWM pin to GND should have a value greater than $15k\Omega$ . |  |  |  |  |

| 3                                        | 3                          | EN    | Enable Control. When pulled low, this pin disables normal operation, causing both UGATE and LGATE to be off. Additionally, it controls the state of the PWM pin. When the EN pin is low, the PWM pin operates in a high-impedance state. It's essential to note that there are no internal mechanisms for pulling the EN pin high or low.                                                                                                            |  |  |  |  |

| 4                                        | 4                          | VCC   | Power Supply for the IC. Please give a 12V voltage source to this pin and bypass it with an R/C filter.                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| 5                                        | 5                          | LGATE | Output for Low-side Gate Driver. Establish a connection between this pin and the low-side MOSFET gate. The shoot-through protection circuitry monitors this pin to detect the off-state of the lower MOSFET.                                                                                                                                                                                                                                         |  |  |  |  |

| 7                                        | 6                          | PHASE | Switch Node. Connect the source of the high-side MOSFET, and the drain of the low-side MOSFET to this pin. This pin serves as the return path for the UGATE driver and is monitored by the shoot-through protection circuit to detect the state of the upper MOSFET.                                                                                                                                                                                 |  |  |  |  |

| 8                                        | 7                          | UGATE | Output for High-side Gate Driver. Establish a connection between this pin and the high-side MOSFET gate. The shoot-through protection circuitry monitors this pin to detect the off-state of the high-side MOSFET.                                                                                                                                                                                                                                   |  |  |  |  |

| 6                                        | 2                          | GND   | The IC's Reference Ground Pin.                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Exposed Pad<br>(SGM25811A/<br>SGM25811C) | Exposed Pad<br>(SGM25811B) | NC    | Not Internally Connected. While the exposed pad of the SGM25811A isn't electrically connected to GND, it's strongly advised to connect it to the GND plane to optimize heat dissipation capabilities.                                                                                                                                                                                                                                                |  |  |  |  |

| Exposed Pad<br>(SGM25811D)               | -                          | GND   | The IC's Reference Ground Pin.                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

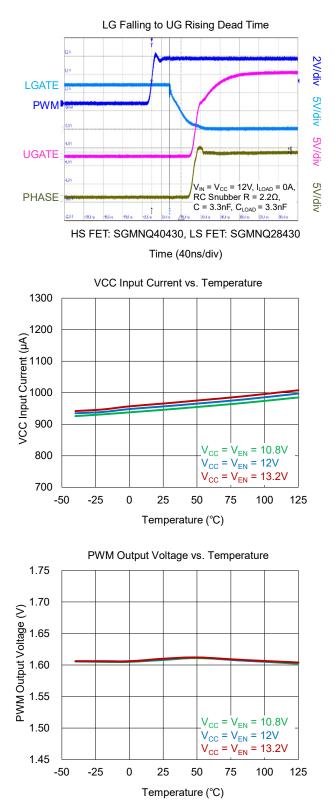

# **ELECTRICAL CHARACTERISTICS**

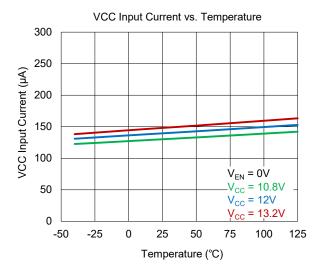

(V<sub>CC</sub> = 12V,  $T_A$  = +25°C, unless otherwise noted.)

| PARAMETER                | SYMBOL               | CONDITIONS                                                              | MIN  | TYP  | MAX  | UNITS |

|--------------------------|----------------------|-------------------------------------------------------------------------|------|------|------|-------|

| Supply Input (VCC)       | L                    |                                                                         |      |      |      |       |

| Supply Current           | I <sub>cc</sub>      | V <sub>EN</sub> = 0V                                                    |      | 1    |      | mA    |

| VCC POR Rising Threshold | V <sub>CCRTH</sub>   | V <sub>cc</sub> Rising                                                  |      | 4.2  |      | V     |

| VCC POR Hysteresis       | V <sub>CCHYS</sub>   |                                                                         |      | 240  |      | mV    |

| PWM Input (PWM)          |                      | <u>.</u>                                                                | •    | •    |      |       |

| High-Level Input Voltage | V <sub>PWMH</sub>    |                                                                         | 2.9  |      |      | V     |

| Low-Level Input Voltage  | V <sub>PWML</sub>    |                                                                         |      |      | 0.4  | V     |

| PWM Floating Voltage     | V <sub>PWM_FLT</sub> |                                                                         |      | 1.6  |      | V     |

|                          |                      | PWM = 0V                                                                | -760 | -490 | -200 | μA    |

| PWM Input Current        | I <sub>PWM</sub>     | PWM = 3.3V                                                              | 0.5  | 1.0  | 1.5  | mA    |

|                          |                      | PWM = 5V                                                                | 1.5  | 2.0  | 2.6  | mA    |

| Enable Control (EN)      | L                    | ·                                                                       |      | •    |      |       |

| High-Level Input Voltage | V <sub>ENH</sub>     |                                                                         | 2.0  |      |      | V     |

| Low-Level Input Voltage  | V <sub>ENL</sub>     |                                                                         |      |      | 0.6  | V     |

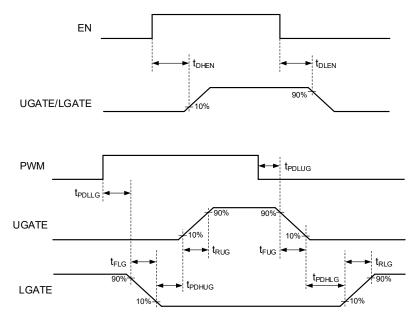

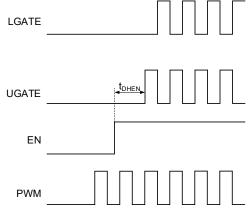

|                          | t <sub>DHEN</sub>    |                                                                         |      | 2    |      | μs    |

| Propagation Delay Time   | t <sub>DLEN</sub>    |                                                                         |      | 114  |      | ns    |

| Bootstrap Switch         | L                    | ·                                                                       |      | •    |      |       |

| On-Resistance            | R <sub>DSON</sub>    | Forward bias current = 1mA                                              |      | 22   |      | Ω     |

| High-side Driver         |                      |                                                                         |      |      |      |       |

| Outrust Desistance       | R <sub>H_SRC</sub>   | V <sub>BOOT</sub> - V <sub>PHASE</sub> = 12V, I <sub>UGATE</sub> = 80mA |      | 2.5  | 4    | Ω     |

| Output Resistance,       | R <sub>H_SNK</sub>   | $V_{BOOT}$ - $V_{PHASE}$ = 12V, $I_{UGATE}$ = -80mA                     |      | 1.4  | 2    | Ω     |

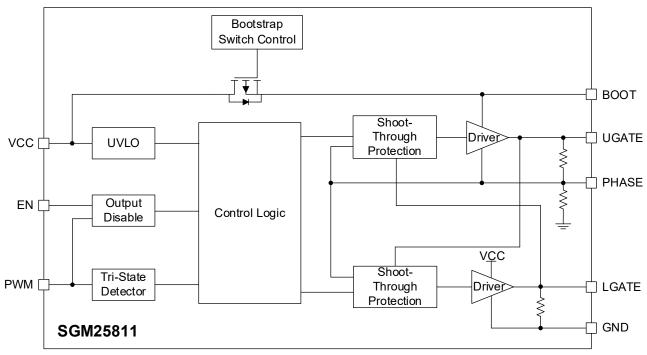

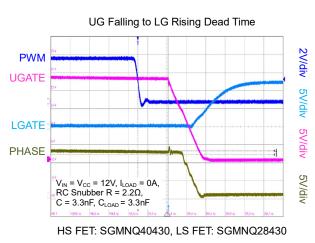

| Output Rising Time       | t <sub>RUG</sub>     | $V_{BOOT}$ - $V_{PHASE}$ = 12V, $C_{LOAD}$ = 3.3nF                      |      | 65   |      | ns    |

| Output Falling Time      | t <sub>FUG</sub>     | $V_{BOOT}$ - $V_{PHASE}$ = 12V, $C_{LOAD}$ = 3.3nF                      |      | 62   |      | ns    |

| Propagation Dalay Time   | t <sub>PDHUG</sub>   | V <sub>BOOT</sub> - V <sub>PHASE</sub> = 12V                            |      | 23   |      | ns    |

| Propagation Delay Time   | t <sub>PDLUG</sub>   | V <sub>BOOT</sub> - V <sub>PHASE</sub> = 12V                            |      | 60   |      | ns    |

| Low-side Driver          |                      |                                                                         |      |      |      |       |

| Output Registeres        | $R_{L\_SRC}$         | $V_{CC}$ = 12V, $I_{LGATE}$ = 80mA                                      |      | 2.7  | 4    | Ω     |

| Output Resistance,       | R <sub>L_SNK</sub>   | $V_{CC}$ = 12V, $I_{LGATE}$ = -80mA                                     |      | 1.3  | 2    | Ω     |

| Output Rising Time       | t <sub>RLG</sub>     | $V_{CC} = 12V, C_{LOAD} = 3.3nF$                                        |      | 73   |      | ns    |

| Output Falling Time      | t <sub>FLG</sub>     | $V_{CC} = 12V, C_{LOAD} = 3.3nF$                                        |      | 45   |      | ns    |

| Propagation Dolay Time   | t <sub>PDHLG</sub>   | $V_{CC} = 12V$                                                          |      | 25   |      | ns    |

| Propagation Delay Time   | t <sub>PDLLG</sub>   | V <sub>CC</sub> = 12V                                                   |      | 34   |      | ns    |

## PARAMETER MEASUREMENT INFORMATION

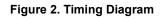

# FUNCTIONAL BLOCK DIAGRAM

#### Figure 3. Block Diagram

# **TYPICAL PERFORMANCE CHARACTERISTICS**

$T_A$  = +25°C, unless otherwise noted.

SG Micro Corp

### **DETAILED DESCRIPTION**

#### **Enable Control**

The enable (EN) pin controls both the state of the PWM pin and the output of the MOSFET gate drivers. When a logic low signal is applied to EN, it disables the gate drivers, keeping both UGATE and LGATE low, while the PWM pin will be in a high-impedance state. On the other hand, a logic high input to EN enables gate driver activation after delay time ( $t_{DHEN}$ ) illustrated in Figure 4. During this delay time, the PWM pin remains in a high-impedance state, with UGATE and LGATE outputs held low. Moreover, the internal control circuit can't respond to the PWM input voltage. Once  $t_{DHEN}$  finishes, both UGATE and LGATE start responding to the PWM input. This design is specifically for SGM's PWM controller, utilizing its PWM pin for multi-functional pin.

Figure 4. Enable Control

#### **PWM** Input

The PWM is a tri-state input pin. A logic high activates the high-side gate driver and deactivates the low-side gate driver once  $V_{CC}$  power-on reset (POR) is established and EN keeps high. Conversely, a logic low deactivates the high-side gate driver and activates the low-side gate driver. When the PWM pin is in high-impedance state, high-side and low-side gate drivers maintain in the low-state, turning off both MOSFETs.

In a floating state, an internal bias circuit keeps the PWM pin voltage at 1.6V. During  $t_{DHEN}$  (refer to Figure 4), both UGATE and LGATE remain low. The PWM pin stays in a high-impedance state, so any input to the PWM is disregarded.

#### Low-side Driver

The low-side driver is used to control an N-MOSFET referenced to ground. Its internal bias is connected to both the  $V_{CC}$  supply and ground. The low-side driver output is opposite to the PWM input: it is low when the PWM input is high, and it is high when the PWM input is low.

However, if a logic low signal is applied to EN pin or the PWM pin is set to a high-impedance state, the output of the low-side driver will remain at a low level.

#### **High-side Driver**

The high-side driver is used to control a floating N-MOSFET, and the bias voltage comes from the internally connected BOOT and PHASE pins. It utilizes an integrated bootstrap switch between the BOOT and VCC pins to provide bias current for the high-side gate driver.

The bootstrap capacitor  $C_{BOOT}$  charges to VCC when the PHASE pin is grounded, a result of turning on the low-side MOSFET. Subsequently, when the high-side MOSFET activates, PHASE pin voltage rises to  $V_{IN}$ , letting the BOOT pin voltage rise to  $V_{IN} + V_{CC}$ . It is crucial for maintaining voltage to keep the high-side MOSFET on.

If a logic low signal is applied to EN pin or the PWM pin is set to a high-impedance state, the output of the high-side driver will remain at a low level.

#### **Shoot-Through Protection**

The shoot-through protection circuit can stop the high-side and low-side MOSFETs conduct simultaneously. It accomplishes this by ensuring one MOSFET is activated only after the other has been completely turned off with a proper delay time.

During the high-side MOSFET is shutdown, the antishoot-through mechanism monitors UGATE and PHASE voltages. The low-side driver will be at high-state until  $(V_{UGATE} - V_{PHASE})$  voltage drops below 1.2V, confirming the completely turning off the high-side MOSFET.

Similarly, while the low-side MOSFET is shutdown, the high-side driver checks the LGATE voltage. It remains in the off-state until  $V_{LGATE}$  drops below 1.2V, ensuring the complete turn-off of the low-side MOSFET.

## **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Original (JUNE 2024) to REV.A      | Page |

|-------------------------------------------------|------|

| Changed from product preview to production data | All  |

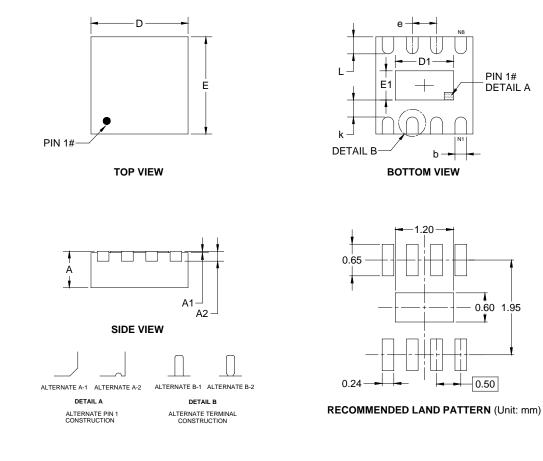

## PACKAGE OUTLINE DIMENSIONS

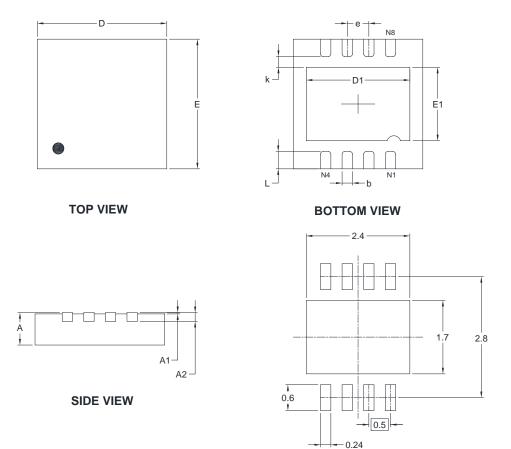

### TDFN-2×2-8L

| Symphol | Dimensions In Millimeters |           |       |  |  |  |  |  |

|---------|---------------------------|-----------|-------|--|--|--|--|--|

| Symbol  | MIN                       | MOD       | МАХ   |  |  |  |  |  |

| A       | 0.700                     | 0.750     | 0.800 |  |  |  |  |  |

| A1      | 0.000                     | -         | 0.050 |  |  |  |  |  |

| A2      |                           | 0.203 REF |       |  |  |  |  |  |

| D       | 1.900                     | 2.000     | 2.100 |  |  |  |  |  |

| E       | 1.900                     | 2.000     | 2.100 |  |  |  |  |  |

| D1      | 1.100                     | 1.200     | 1.300 |  |  |  |  |  |

| E1      | 0.500                     | 0.600     | 0.700 |  |  |  |  |  |

| b       | 0.180                     | -         | 0.300 |  |  |  |  |  |

| е       | 0.500 TYP                 |           |       |  |  |  |  |  |

| k       |                           | 0.200 MIN |       |  |  |  |  |  |

| L       | 0.250 0.350 0.450         |           |       |  |  |  |  |  |

NOTE: This drawing is subject to change without notice.

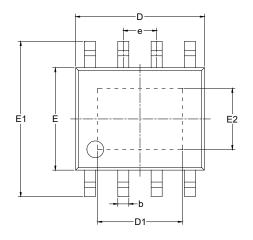

# PACKAGE OUTLINE DIMENSIONS

### TDFN-3×3-8BL

RECOMMENDED LAND PATTERN (Unit: mm)

| Symbol |       | nsions<br>meters | Dimensions<br>In Inches |       |  |  |

|--------|-------|------------------|-------------------------|-------|--|--|

|        | MIN   | MAX              | MIN                     | MAX   |  |  |

| А      | 0.700 | 0.800            | 0.028                   | 0.031 |  |  |

| A1     | 0.000 | 0.050            | 0.000                   | 0.002 |  |  |

| A2     | 0.203 | REF              | 0.008 REF               |       |  |  |

| D      | 2.900 | 3.100            | 0.114                   | 0.122 |  |  |

| D1     | 2.300 | 2.500            | 0.091                   | 0.098 |  |  |

| E      | 2.900 | 3.100            | 0.114                   | 0.122 |  |  |

| E1     | 1.600 | 1.800            | 0.063                   | 0.071 |  |  |

| k      | 0.200 | ) MIN            | 0.008                   | 8 MIN |  |  |

| b      | 0.180 | 0.300            | 0.007 0.012             |       |  |  |

| е      | 0.500 | ) TYP            | 0.020                   | TYP   |  |  |

| L      | 0.300 | 0.500            | 0.012 0.020             |       |  |  |

NOTE: This drawing is subject to change without notice.

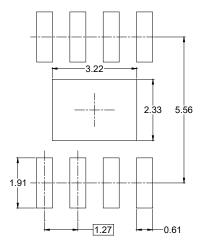

# PACKAGE OUTLINE DIMENSIONS

# **SOIC-8 (Exposed Pad)**

#### RECOMMENDED LAND PATTERN (Unit: mm)

| Symbol | Dimensions<br>In Millimeters |          |       |  |  |  |  |  |

|--------|------------------------------|----------|-------|--|--|--|--|--|

|        | MIN                          | MOD      | MAX   |  |  |  |  |  |

| A      |                              |          | 1.700 |  |  |  |  |  |

| A1     | 0.000                        | -        | 0.150 |  |  |  |  |  |

| A2     | 1.250                        | -        | 1.650 |  |  |  |  |  |

| b      | 0.330                        | -        | 0.510 |  |  |  |  |  |

| с      | 0.170                        | -        | 0.250 |  |  |  |  |  |

| D      | 4.700                        | -        | 5.100 |  |  |  |  |  |

| D1     | 3.020                        | -        | 3.420 |  |  |  |  |  |

| E      | 3.800                        | -        | 4.000 |  |  |  |  |  |

| E1     | 5.800                        | -        | 6.200 |  |  |  |  |  |

| E2     | 2.130                        | -        | 2.530 |  |  |  |  |  |

| е      |                              | 1.27 BSC |       |  |  |  |  |  |

| L      | 0.400                        | -        | 1.270 |  |  |  |  |  |

| θ      | 0°                           | -        | 8°    |  |  |  |  |  |

| ССС    |                              | 0.100    |       |  |  |  |  |  |

#### NOTES:

This drawing is subject to change without notice.

The dimensions do not include mold flashes, protrusions or gate burrs.

3. Reference JEDEC MS-012.

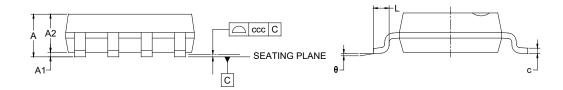

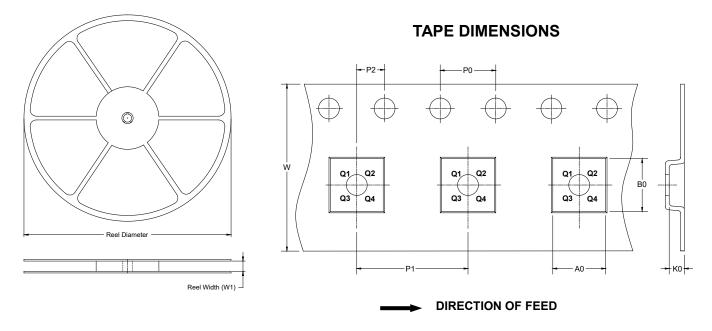

# TAPE AND REEL INFORMATION

#### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

| Package Type         | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| TDFN-2×2-8L          | 7"               | 9.5                      | 2.30       | 2.30       | 1.10       | 4.0        | 4.0        | 2.0        | 8.0       | Q1               |

| TDFN-3×3-8BL         | 13"              | 12.4                     | 3.35       | 3.35       | 1.13       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

| SOIC-8 (Exposed Pad) | 13"              | 12.4                     | 6.40       | 5.40       | 2.10       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

### **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

### **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type   | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |        |

|-------------|----------------|---------------|----------------|--------------|--------|

| 7" (Option) | 368            | 227           | 224            | 8            |        |

| 7"          | 442            | 410           | 224            | 18           | ]_     |

| 13″         | 386            | 280           | 370            | 5            | DD0002 |