# SGM4551YXET Dual Bidirectional I<sup>2</sup>C Bus and SMBus Voltage-Level Translator

## GENERAL DESCRIPTION

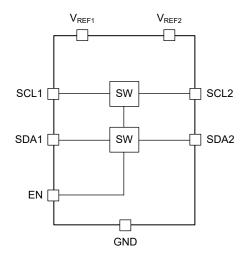

The SGM4551YXET is a 2-bit, SMbus, dual, bidirectional,  $I^2C$  voltage translator with the ability of enable (EN) function. For  $V_{REF1}$ , the typical operation range is from 1.2V to 3.3V and the typical operation for  $V_{REF2}$  is from 1.8V to 5.5V.

The signal can be transmitted bilaterally from 1.2V to 5V. The propagation delay is significant small as the low on-resistance of SGM4551YXET. Also, if the EN pin is in high position, the voltage translator is transparent and then it allows the connection between SCL1 and SCL2, SDA1 and SDA2 respectively. In addition, in this state, the transmitting direction is bidirectional. However, the transmitting will be suspended if the EN pin is in low state as the high-impedance property at this moment.

For the applications, the connections of the devices and bus length are limited as the 400pF capacitance of the bus pin. However, SGM4551YXET allows the isolation between two sides of I<sup>2</sup>C bus so that more and more I<sup>2</sup>C devices can be added and connected with SGM4551YXET.

Two different kinds of bus frequencies are supported by SGM4551YXET, one is 400kHz and the other is 100kHz. Also, if two frequencies for the buses are required, the priority of 400kHz should be always higher than that of 100kHz. Because of the adding of the additional delay, the operational frequency of the device must be lower than 400kHz if the frequency of the master is equal to 400kHz.

For the application of standard I<sup>2</sup>C, the pull-up resistor is required for the logic high levels, which means that the operation for I<sup>2</sup>C in this case is open-drain. Each side of the repeater requires a pull-up resistor and the value of resistor depends on the operation of SGM4551YXET. Also, when multiple masters are connected with SGM4551YXET, the standard operation current is 3mA, and high current can be taken into account under the specific conditions.

The resistance between SDA1 and SDA2 is low when the state of them is low. However, if the state of SDA1 or SDA2 is high, the level of high position depends on the corresponding voltage reference. In the transparent mode, when the position of SDA1 is high, SDA2 must be pulled to a high level through the pull-up resistor. In addition, the transition for high and low voltage is seamless which can be selected by the users.

Because of the same electrical characteristics for all the outputs of SGM4551YXET, so that the deviations of the propagation delay and voltage is extremely small. In addition, this advantage is good for the transition of discrete transistors as the symmetrical switch inside SGM4551YXET. On top of this, SGM4551YXET can also provide the protection of ESD for the devices with weak ESD ability.

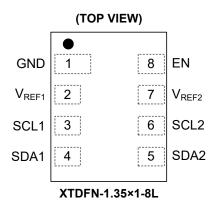

The SGM4551YXET is available in a Green XTDFN-1.35×1-8L package. It operates over an ambient temperature range of -40°C to +85°C.

## **FEATURES**

- Bidirectional I<sup>2</sup>C Translator

- Support I<sup>2</sup>C and SMBus Compatible

- Propagation Delay: Less than 5.5ns

- Acceptable Voltage Reference

- 1.2V  $V_{REF1}$  and 1.8V, 2.5V, 3.3V, or 5V  $V_{REF2}$

- 1.8V  $V_{REF1}$  and 2.5V, 3.3V, or 5V  $V_{REF2}$

- 2.5V  $V_{REF1}$  and 3.3V or 5V  $V_{REF2}$

- 3.3V V<sub>REF1</sub> and 5V V<sub>REF2</sub>

- Low On-Resistance: 3.5Ω (TYP)

- GPIO Ports with I<sup>2</sup>C Open-Drain Logic (SCL1, SDA1, SCL2 and SDA2)

- Mixed-Mode Signal be Supported by I/O Ports with 5V Tolerant

- When EN is Low, SGM4551YXET is in High-Impedance Mode

- Lock-Up-Free Operation for Isolation when EN =

- The Pinout of the Internal Material is Beneficial for PCB Layout

- Available in a Green XTDFN-1.35×1-8L Package

## **LOGIC DIAGRAM**

## **FUNCTION TABLE**

| EN <sup>(1)</sup> | FUNCTION                  |

|-------------------|---------------------------|

| Н                 | SCL1 = SCL2, SDA1 = SDA2. |

| L                 | Disconnect.               |

#### NOTE:

1. The transparent mode will be launched if the voltage of EN pin is 1V higher than the voltage of SCL1 and SCL2. And so does the condition of SDA. H = HIGH level, L = LOW level.

## PACKAGE/ORDERING INFORMATION

| MODEL       | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING | PACKING<br>OPTION   |

|-------------|------------------------|-----------------------------------|--------------------|--------------------|---------------------|

| SGM4551YXET | XTDFN-1.35×1-8L        | -40°C to +85°C                    | SGM4551YXET8G/TR   | 2SX                | Tape and Reel, 5000 |

#### MARKING INFORMATION

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### ABSOLUTE MAXIMUM RATINGS

| DC Reference Voltage Range                                  |                |

|-------------------------------------------------------------|----------------|

| V <sub>REF1</sub>                                           | 0.3V to 6V     |

| V <sub>REF2</sub>                                           | 0.3V to 6V     |

| Input Voltage Range (1), V <sub>I</sub>                     | 0.3V to 6V     |

| Input/Output Voltage Range (1), V <sub>I/O</sub>            | 0.3V to 6V     |

| Continuous Channel Current                                  | 64mA           |

| Input Clamp Current, I <sub>IK</sub> , (V <sub>I</sub> < 0) | 50mA           |

| Junction Temperature                                        | +150°C         |

| Storage Temperature Range                                   | 65°C to +150°C |

| Lead Temperature (Soldering, 10s)                           | +260°C         |

| ESD Susceptibility                                          |                |

| HBM                                                         | 3000V          |

| MM                                                          | 300V           |

| CDM                                                         | 1000V          |

#### NOTE:

1. When the input and output current ratings are observed, the input and I/O negative voltage ratings may be exceeded.

# RECOMMENDED OPERATING CONDITIONS

Operating Temperature Range .....-40°C to +85°C

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

# **PIN CONFIGURATION**

# **PIN DESCRIPTION**

| PIN | NAME              | FUNCTION                                              |

|-----|-------------------|-------------------------------------------------------|

| 1   | GND               | Ground.                                               |

| 2   | $V_{REF1}$        | Low-side Reference Supply Voltage for SCL1 and SDA1.  |

| 3   | SCL1              | Low-side Clock Signal.                                |

| 4   | SDA1              | Low-side Data Signal.                                 |

| 5   | SDA2              | High-side Data Signal.                                |

| 6   | SCL2              | High-side Clock Signal.                               |

| 7   | V <sub>REF2</sub> | High-side Reference Supply Voltage for SCL2 and SDA2. |

| 8   | EN                | Enable Control Pin.                                   |

# **ELECTRICAL CHARACTERISTICS**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ typical values are at } T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

| PARAM                 | ETER       | SYMBOL               | CONDITI                                      | ONS                                       | MIN | TYP | MAX  | UNITS |

|-----------------------|------------|----------------------|----------------------------------------------|-------------------------------------------|-----|-----|------|-------|

| Input/Output Voltage  |            | V <sub>I/O</sub>     | SCL1, SDA1, SCL2, SDA2                       |                                           | 0   |     | 5    | V     |

| Reference Voltage     |            | $V_{REF1}$           |                                              |                                           | 0   |     | 5    | V     |

| Reference Voltage     |            | $V_{REF2}$           |                                              |                                           | 0   |     | 5    | V     |

| Enable Input Voltage  | •          | $V_{EN}$             |                                              |                                           | 0   |     | 5    | V     |

| Pass Switch Current   |            | I <sub>PASS</sub>    |                                              |                                           |     |     | 64   | mA    |

| Input Clamp Voltage   |            | V <sub>IK</sub>      | $I_{i} = -18mA, V_{EN} = 0V$                 |                                           |     |     | -1.2 | V     |

| Input Leakage Current |            | I <sub>IH</sub>      | V <sub>I</sub> = 5V, V <sub>EN</sub> = 0V    | V <sub>I</sub> = 5V, V <sub>EN</sub> = 0V |     |     | 8    | μA    |

| Enable Leakage Cur    | rent       | I <sub>EN</sub>      | V <sub>1</sub> = 5V                          |                                           |     |     | 1    | μA    |

| Input Capacitance     |            | $C_{I(EN)}$          | V <sub>I</sub> = 3V or 0V                    |                                           |     | 15  |      | pF    |

| Off Capacitance       | SCLn, SDAn | C <sub>IO(OFF)</sub> | $V_0 = 3V \text{ or } 0V, V_{EN} = 0V$       | /                                         |     | 8   |      | pF    |

| On Capacitance        | SCLn, SDAn | C <sub>IO(ON)</sub>  | $V_0 = 3V \text{ or } 0V, V_{EN} = 3V$       | /                                         |     | 7   |      | pF    |

|                       |            |                      |                                              | V <sub>EN</sub> = 4.5V                    |     | 3.5 | 5.5  |       |

|                       |            |                      | \( \ - 0\\ \ \ \ - 0\\ \ \ \ \ \ \ \ \ \ \   | V <sub>EN</sub> = 3.0V                    |     | 3.8 | 6.0  |       |

|                       |            |                      | $V_1 = 0V, I_0 = 64mA$                       | V <sub>EN</sub> = 2.3V                    |     | 4.0 | 6.0  |       |

| On-Resistance (1)     | SCLn, SDAn | R <sub>on</sub>      |                                              | V <sub>EN</sub> = 1.5V                    |     | 4.5 | 6.5  | Ω     |

|                       |            |                      | \\ - 0 4\\ 1 - 45\\                          | V <sub>EN</sub> = 4.5V                    | 1.5 | 4.5 | 7.0  |       |

|                       |            |                      | $V_1 = 2.4V, I_0 = 15mA$                     | V <sub>EN</sub> = 3.0V                    | 11  | 40  | 65   |       |

|                       |            |                      | V <sub>I</sub> = 1.7V, I <sub>O</sub> = 15mA | V <sub>EN</sub> = 2.3V                    | 9   | 35  | 58   |       |

#### NOTE:

1. It is measured by a voltage drop between SCL1 and SCL2, or between SDA1 and SDA2, at the indicated current through the switch. The on-resistance depends on the lowest voltage of the two ports.

# **SWITCHING CHARACTERISTICS**

| PARAMETER                                                                                                                                                                    | FROM (INPUT)                                                                                                                            | TO (OUTPUT)                    | C <sub>L</sub> = 50pF           | C <sub>L</sub> = 30pF         | C <sub>L</sub> = 15pF | UNITS         |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|---------------------------------|-------------------------------|-----------------------|---------------|--|--|

| AC Performance (Tr                                                                                                                                                           | anslating Down) (2)                                                                                                                     |                                |                                 |                               |                       |               |  |  |

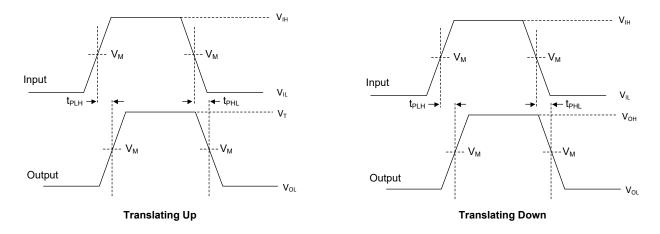

| (Typical values are at                                                                                                                                                       | $T_A = +25^{\circ}C$ , EN = 3.3                                                                                                         | $V, V_{IH} = 2.3V, V_{IL} = 0$ | $V$ , $V_M$ = 1.15 $V$ , unless | otherwise noted.) (Se         | ee Figure 1)          |               |  |  |

| t <sub>PLH</sub>                                                                                                                                                             | SCL2 or SDA2                                                                                                                            | SCL1 or SDA1                   | 0.9                             | 0.7                           | 0.5                   | no            |  |  |

| t <sub>PHL</sub>                                                                                                                                                             | SCLZ OF SDAZ                                                                                                                            | SCLT OF SDAT                   | 0.9                             | 0.7                           | 0.5                   | ns            |  |  |

| AC Performance (Tr                                                                                                                                                           | AC Performance (Translating Down) (2)                                                                                                   |                                |                                 |                               |                       |               |  |  |

| (Typical values are at                                                                                                                                                       | (Typical values are at $T_A$ = +25°C, EN = 2.5V, $V_{IH}$ = 1.5V, $V_{IL}$ = 0V, $V_M$ = 0.75V, unless otherwise noted.) (See Figure 1) |                                |                                 |                               |                       |               |  |  |

| t <sub>PLH</sub>                                                                                                                                                             | 2012 2012                                                                                                                               | SCL2 or SDA2 SCL1 or SDA1      | 0.9                             | 0.7                           | 0.5                   | no            |  |  |

| t <sub>PHL</sub>                                                                                                                                                             | SCL2 or SDA2                                                                                                                            |                                | 0.9                             | 0.7                           | 0.5                   | ns            |  |  |

| AC Performance (Tr                                                                                                                                                           | anslating Up) (3)                                                                                                                       |                                |                                 |                               |                       |               |  |  |

| (Typical values are at                                                                                                                                                       | $T_A = +25^{\circ}C$ , EN = 3.3                                                                                                         | $V, V_{IH} = 2.3V, V_{IL} = 0$ | $V, V_T = 3.3V, V_M = 1.1$      | 5V, $R_L = 300\Omega$ , unles | s otherwise noted.) ( | See Figure 1) |  |  |

| t <sub>PLH</sub>                                                                                                                                                             | SCL1 or SDA1                                                                                                                            | 0010 0040                      | 1                               | 0.8                           | 0.6                   | 20            |  |  |

| t <sub>PHL</sub>                                                                                                                                                             | SCLI OF SDAT                                                                                                                            | SCL2 or SDA2                   | 1                               | 0.8                           | 0.6                   | ns            |  |  |

| AC Performance (Tr                                                                                                                                                           | AC Performance (Translating Up) (3)                                                                                                     |                                |                                 |                               |                       |               |  |  |

| (Typical values are at $T_A$ = +25°C, EN = 2.5V, $V_{IH}$ = 1.5V, $V_{IL}$ = 0V, $V_T$ = 2.5V, $V_M$ = 0.75V, $R_L$ = 300 $\Omega$ , unless otherwise noted.) (See Figure 1) |                                                                                                                                         |                                |                                 |                               |                       |               |  |  |

| t <sub>PLH</sub>                                                                                                                                                             | SCL1 or SDA1                                                                                                                            | SCL2 or SDA2                   | 1                               | 0.8                           | 0.6                   | no            |  |  |

| t <sub>PHL</sub>                                                                                                                                                             | 30LTUI SDAT                                                                                                                             | SULZ UI SUAZ                   | 1                               | 0.8                           | 0.6                   | ns            |  |  |

#### NOTES:

- 2. TRANSLATING DOWN: The high voltage side drives the low voltage side.

- 3. TRANSLATING UP: The low voltage side drives the high voltage side.

## **WAVEFORMS**

Figure 1. Translating Up and Translating Down Waveforms

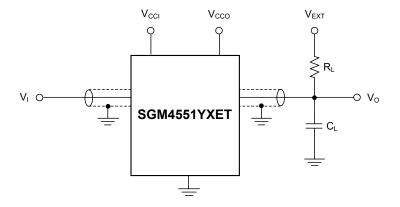

# **TEST CIRCUIT**

Definitions for test circuit:

R<sub>L</sub> = Load resistance.

$C_L$  = Load capacitance including jig and probe capacitance.

V<sub>EXT</sub> = External voltage for measuring switching times.

$V_{CCI}$  = Supply voltage associated with the input.

V<sub>CCO</sub> = Supply voltage associated with the output.

Figure 2. Test Circuit for Measuring Switching Times

## **APPLICATION INFORMATION**

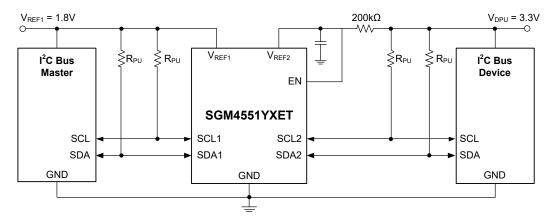

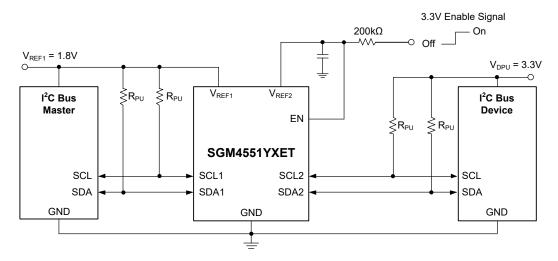

## General Applications of I<sup>2</sup>C

Since the limitation of the load capacitance is 400pF, so that the number of devices which are connected to SGM4551YXET will be limited. Also, the advantage of SGM4551YXET is that it can isolate the buses of two sides, which means that more and more I<sup>2</sup>C devices can be connected with this device.

Two different kinds of bus frequencies are supported by SGM4551YXET, one is 400kHz and the other is 100kHz. Also, if two frequencies for the buses are required, the priority of 400kHz should be always higher than that of 100kHz.

Because of the adding of the additional delay of the repeater, the operational frequency of the device must be lower than 400kHz if the frequency of the master is equal to 400kHz.

For the application of standard I<sup>2</sup>C, the pull-up resistor is required for the logic high levels, which means that the operation for I<sup>2</sup>C in this case is open-drain. Each side of the repeater requires a pull-up resistor and the value of resistors depend on the operation of SGM4551YXET. Also, when multiple masters are connected with SGM4551YXET, the standard operation current is 3mA, and high current can be taken into account under the specific conditions.

Figure 3. Typical Application Circuit (Switch Always Enabled)

Figure 4. Typical Application Circuit (Switch Enable Control)

# **APPLICATION INFORMATION (continued)**

#### **Bidirectional Translation**

For both directional applications, it is recommended to connect reference pins to  $V_{REF2}$ . Also, both SCL and SDA pins should be pulled up by a resistor. A bypass capacitor should be added at the pin of  $V_{REF2}$  to improve the stability. Both the outputs of master and slave device can be push-pull or open-drain (a pull-up resistor is required at this case). In addition, if the users desire to use push-pull structure to generate the output, SGM4551YXET can operate unidirectional or be controlled by direction-control mechanism to prevent the risk of contentions. For open-drain output structure, it does not need any control mechanism for the transmitting direction.

The pin of  $V_{\text{REF1}}$  should be tied to the  $V_{\text{CC}}$  of processor directly.

## Sizing Pull-Up Resistor

The function of pull-up resistor is used to limit the operation current to 15mA when the output is in high position, which means that the pass voltage will be around 350mV. The larger the current flowing to the pull-up resistor, the larger the pass voltage it is. To meet the requirement of 15mA, the pull-up resistor should be calculated as below:

$$R_{PU} = \frac{V_{DPU} - 0.35V}{0.015A}$$

Table 2 illustrates the corresponding value of pull-up resistor for different  $V_{REF}$  and operation current. The +10% resistance value is recommended, as it ensures the pass voltage within 350mV. In addition, if considering use a driver, please make sure that it has the ability to sink the total current of SGM4551YXET.

Table 1. Application Operating Conditions (1)

| PARAMETER                    | SYMBOL            | MIN                     | TYP                     | MAX                     | UNITS |

|------------------------------|-------------------|-------------------------|-------------------------|-------------------------|-------|

| Reference Voltage            | $V_{REF2}$        | V <sub>REF1</sub> + 0.6 | V <sub>REF1</sub> + 0.6 | V <sub>REF1</sub> + 0.6 | V     |

| Enable Input Voltage         | V <sub>EN</sub>   | V <sub>REF1</sub> + 0.6 | V <sub>REF1</sub> + 0.6 | V <sub>REF1</sub> + 0.6 | V     |

| Reference Voltage            | V <sub>REF1</sub> | 0                       | 1.5                     | 4.4                     | V     |

| Pass Switch Current          | I <sub>PASS</sub> |                         | 15                      |                         | mA    |

| Reference Transistor Current | I <sub>REF</sub>  |                         | 5                       |                         | μΑ    |

| Operating Temperature Range  | T <sub>A</sub>    | -40                     |                         | 85                      | °C    |

#### NOTE:

1. The typical values are measured at  $T_A = +25$ °C.

Table 2. Pull-Up Resistor Values (1) (2)

|           | Pull-Up Resistor Value (Ω) |          |         |          |         |                     |  |  |  |

|-----------|----------------------------|----------|---------|----------|---------|---------------------|--|--|--|

| $V_{DPU}$ | 15                         | mA       | 10      | mA       | 3mA     |                     |  |  |  |

|           | NOMINAL                    | +10% (3) | NOMINAL | +10% (3) | NOMINAL | +10% <sup>(3)</sup> |  |  |  |

| 5V        | 310                        | 341      | 465     | 512      | 1550    | 1705                |  |  |  |

| 3.3V      | 197                        | 217      | 295     | 325      | 983     | 1082                |  |  |  |

| 2.5V      | 143                        | 158      | 215     | 237      | 717     | 788                 |  |  |  |

| 1.8V      | 97                         | 106      | 145     | 160      | 483     | 532                 |  |  |  |

| 1.5V      | 77                         | 85       | 115     | 127      | 383     | 422                 |  |  |  |

| 1.2V      | 57                         | 63       | 85      | 94       | 283     | 312                 |  |  |  |

#### NOTES:

- 1. Measured at the condition of  $V_{OL}$  = 350mV.

- 2. The  $V_{OL}$  of the output is equal to 175mV.

- 3. 10% range of resistor for suitable operation current.

# **APPLICATION INFORMATION (continued)**

#### SGM4551YXET Bandwidth

Different kinds of applications support different frequencies. Also, SGM4551YXET can operate for the conditions which the frequency is greater than 100MHz. The loading of the SGM4551YXET affects the maximum operation frequency. Also, the bandwidth of the SGM4551YXET is affected by the on-resistance and on-capacitance.

The corner frequency (-3dB point) of SGM4551YXET is 500MHz, which is measured in an analog way. However, for digital applications, the previous five harmonics of the input signal should never be degraded by the device, which means that the maximum bandwidth should be five times larger than the input digital signal. Also, the previous five harmonics are significant. Since the corner frequency of SGM4551YXET is around 500MHz, so that this device can support the digital signal with the frequency of 100MHz.

There is no drive capability for SGM4551YXET so that the driver of the host should be strengthen enough for the condition of high frequency. If the output structure of the host device is push-pull, the pull-up resistor will not be taken into account, which can significantly decrease the length of trace.

The maximum frequency harmonic (knee frequency:  $f_{\rm knee}$ ) can be calculated by the following equations. For the input signal with fast rising or falling edge, like square waveform, the high frequency component is infinite. However, the knee frequency is used to determine the important frequency component,

which means that if the frequency of harmonics is larger than this limitation, the users can assume that it will not influence the shape of the input signal.

The equations to calculate f<sub>knee</sub> are shown as below:

$f_{knee} = 0.5/RT(10\% - 90\%)$  $f_{knee} = 0.4/RT(20\% - 80\%)$

If the threshold of the input signal is determined by 10% to 90%, the knee frequency can be defined as 0.5 divided by the rising time. If the threshold of the input signal is determined by 20% to 80%, the knee frequency can be defined as 0.4 divided by the rising time.

The following suggestions should be accepted to improve the performance of SGM4551YXET:

- 1. Minimize the distance between processor and SGM4551YXET as close as possible by minimizing the length of trace in PCB.

- 2. The ringing and reflection can be improved by reducing the length of trace which is less than half the transmission time of the signal.

- 3. A pull-up resistor should be taken into account to be added at 1.8V side for reducing the overshoot. Also, a falling edge with slow falling time is expected by the application of SGM4551YXET.

# Dual Bidirectional I<sup>2</sup>C Bus and SMBus Voltage-Level Translator

# SGM4551YXET

# **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Original (OCTOBER 2023) to REV.A

Page

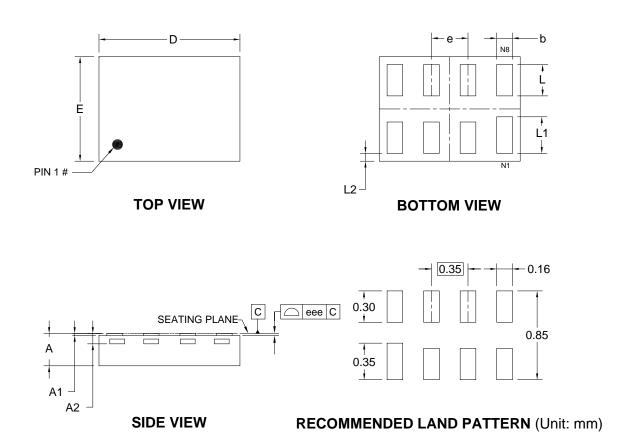

# PACKAGE OUTLINE DIMENSIONS XTDFN-1.35×1-8L

| Symbol | Dimensions In Millimeters |             |       |  |  |  |

|--------|---------------------------|-------------|-------|--|--|--|

| Symbol | MIN                       | MOD         | MAX   |  |  |  |

| Α      | -                         | 0.310       | 0.330 |  |  |  |

| A1     | 0.000                     | -           | 0.050 |  |  |  |

| A2     |                           | 0.100 REF   |       |  |  |  |

| D      | 1.250                     | 1.350       | 1.450 |  |  |  |

| Е      | 0.900 1.000               |             | 1.100 |  |  |  |

| b      | 0.110                     | 0.160       | 0.210 |  |  |  |

| е      |                           | 0.350 BSC   |       |  |  |  |

| L      | 0.250                     | 0.300       | 0.350 |  |  |  |

| L1     | 0.300                     | 0.300 0.350 |       |  |  |  |

| L2     | 0.075 REF                 |             |       |  |  |  |

| eee    | -                         | 0.050       | -     |  |  |  |

NOTE: This drawing is subject to change without notice.

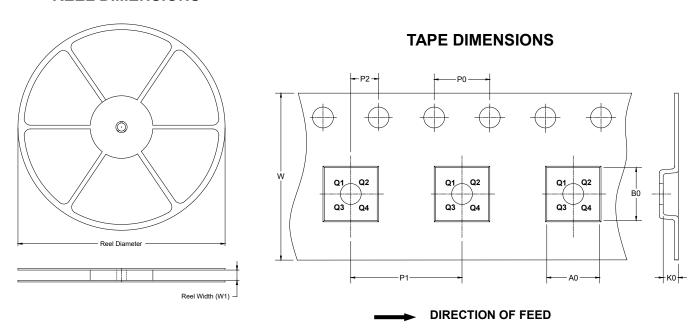

# TAPE AND REEL INFORMATION

## **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

## **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type    | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| XTDFN-1.35×1-8L | 7"               | 9.5                      | 1.21       | 1.51       | 0.39       | 4.0        | 4.0        | 2.0        | 8.0       | Q1               |

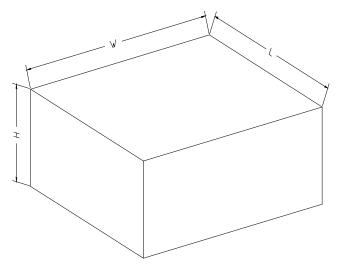

## **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

## **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type   | Length<br>(mm) | Width<br>(mm) | Height (mm) | Pizza/Carton |

|-------------|----------------|---------------|-------------|--------------|

| 7" (Option) | 368            | 227           | 224         | 8            |

| 7"          | 442            | 410           | 224         | 18           |